(54) ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Пороговый элемент | 1984 |

|

SU1261100A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1984 |

|

SU1236602A1 |

| Пороговое устройство | 1986 |

|

SU1368979A1 |

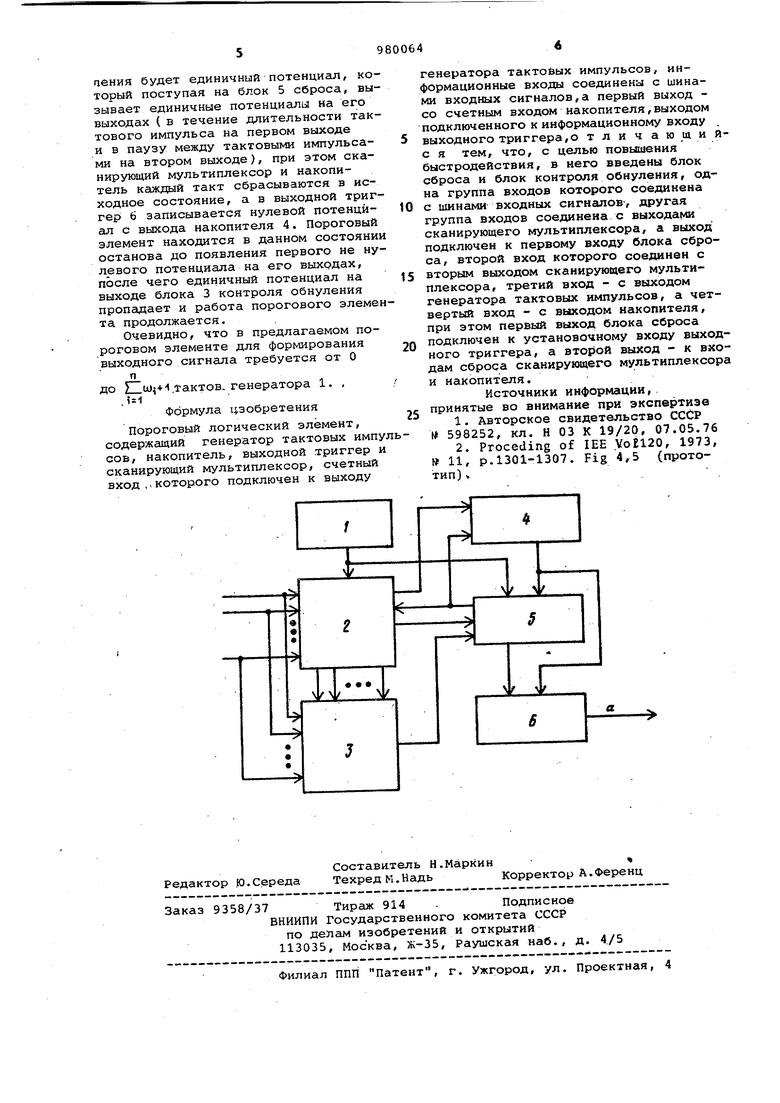

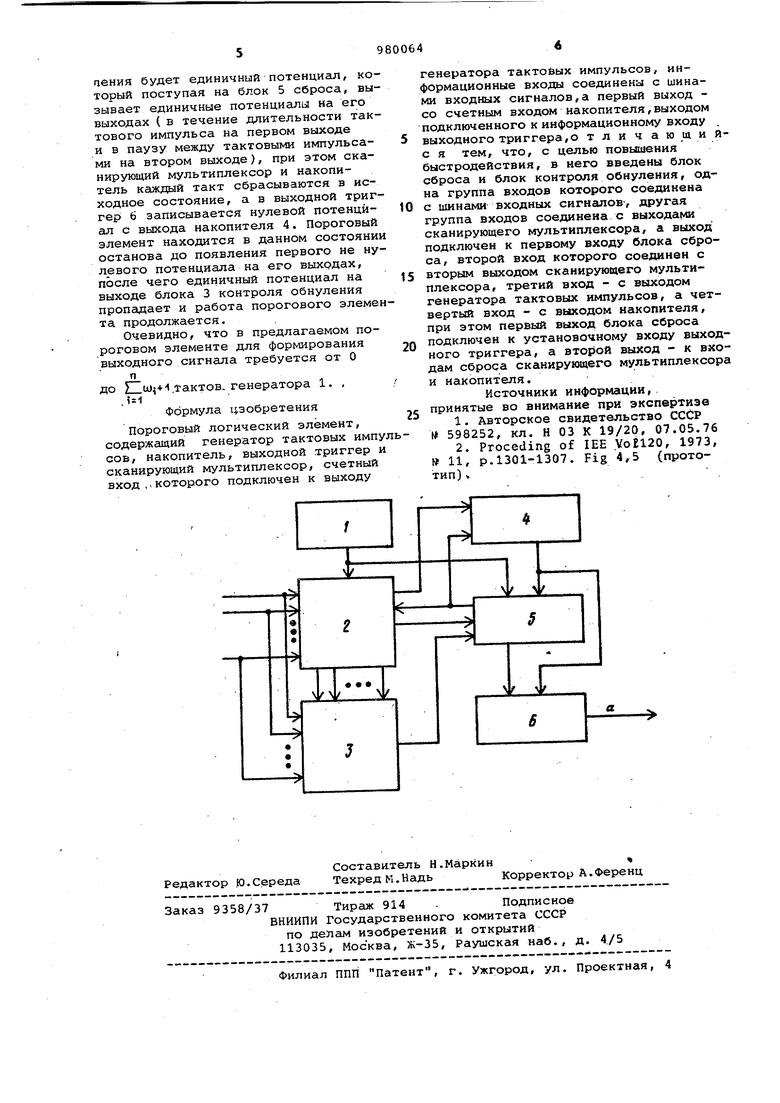

ИзоОретёние относится к автоматике и вычислительно.й технике и может .быть использовано для построения раз личных устройств обработки дискрет. ной чнформсщии. Известен пороговый элемент, содержащий многоБХОдовой элемент Ш1И, входы которого соединены с выходами пяти трехвходовых элементов И, ;ве группы по четыре двухвходовых . элемента ИЛИ, соединенные с входами элементов И СП. Недостатком таких пороговых логических элементов являются ограничен ные функциональные возможности, так как он реализует только пороговую функцию семи переменных с порогом 3. Наиболее близким по технической сущности к предлагаемому является пороговый элемент, содержащий генератор тактовых импульсов, накопитель выходной -триггер и сканирующий мульт плексор, -дополнительн1 й вход которог подключен к выходу генератора тактов импульсов, входы соединены с шинами входных сигналов, а первый выход с счетным входом накопителя, выходом подключенного к информационному входу выходного -триггера 2 . Недостатком таких пороговых элементов является низкое быстродействие. Цепь изобретения - повышение быстродействия. Поставленная цель достигается тем, что в пороговый логический элемент, содержащий генератор тактовых импульсов, накопитель, выходной триггер и сканирукяций мультиплексор, счетный вход которого подключен к выходу генератора тактовых импульсов, информационные входы соединены с шинами входных сигналов, а первый выход со счетным входом накопителя, выходом подключенного к информационному входу выходного триггера, введены блок сброса и блок контроля обнуления, одна группа входов которого соединена с шинами входных сигналов, другая группа входов соединена с выходами сканирующего мультиплексора, третий вход - с выходом генератора тактовых импульсов, а четвертый входс выходом накопителя, при этом первый выход блока сброса подключен к установочному входу выходного триггера, а второй выход - к входам сброса сканирующего мультиплексора и накопителя. На чертеже представлена блок-схема предлагаемого порогового элемента Пороговый, элемент состоит- из генератора 1 тактовых импульсов, сканирующего мультиплексора 2, блока 3 контроля обнуления, накопителя 4, блока 5 сброса и выходного триггера Выход.генератора 1.тактовых импул сов соединен со счетным входом скани рующего мультиплексора, группа из t входов которого является входами порогового элемента и соединена с вх дами блока 3 контроля обнуления. Гру па выходов сканирующего мультиплексора (выходы регистра сдвига мультиплексора ) соединена с второй группой входов блока 3 контроля обнуления, а первый выход - со счетным входом накопителя 4. Выход блока контроля обнуления соединен с первым входом блока 5 сброса, второй вход которого соединен с вторым выходом сканирую-, ЛГ щего мультиплексора 2 {выходом (ZZ. + 1 }-го выхода регистра сдвига сканирующего мультиплексора, где п - число входов; ш - веса.входов, третий вход - с выходом генератора 1 тактовых импульсов, с информационным входом выходного триггера б. Пер вый выход блока 5 сброса соединен с входом разрешения записи выходного триггера 6, а второй - с входами сбр са сканирующего мультиплексора 2 и .накопителя 4. Элемент работает следующим образом. В исходном состоянии сканирующий мультиплексор 2, накопитель 4 и выходной триггер б сброшены. Входные сигналы поступают на входы сканирующего мультиплексора 2 и блока 3 конт роля обнуления. На счетный вход сканирующего мультиплексора 2 поступают тактовые импульсы с выхода генератора 1. При этом сканирующий мультиплексор 2 производит последовательное подключение входов порогового элемента на свой первый выход, соединенный со счетным входом накопи теля 4. Причем каждый вход порогового элемента подключается к первому выходу сканирующего мультиплексора 2 число раз, равное его весу uJ.j . Нако питель 4 считает число единичных потенциалов, поступающих на его счет ный вход. В момент; .когда число импульсов (единичных потенциалов с вхо дов порогового элемента ), поступающих на вход накопителя 4, становится равным порогу элемента, на выходе накопителя появляется единичный потенциал, поступающий на информационный вход триггера б и четвертый вход блока 5 сброса. При этом на . первом выходе блока 5 сброса формируется единичный потенциал, поступающий на установочный вход ( вход разрешения записиJ выходного триггера б, в который при этом записывается единичный потенциал, с выхода накопителя 4. По окончании тактового импульса на втором выходе блока 5 сброса формируется единичный потенциал, поступающий на входы сброса сканирующего мультиплексора 2 и накопителя 4, устанавливая их в исходное состояние. После чего цикл работы порогового элемента.повторяется. Если после опроса всех входов порогового элемента на выходе накопителя 4не прявится единичный потенциал . п (т.е. EIiw,-x,.c(,, где о - порог), то сканирующий мультиплексор 2 возвращается в исходное ..состояние, на его втором выходе появляется единичный потенциал, поступающий на второй вход блока 5 сброса. При этом на первом выходе блока 5 сброса появляется единичный потенциал, разрешающий запись в выходной триггер б нулевого потенциала с выхода накопителя 4. По окончании тактового импульса единичный потенциал появляется на втором выходе блока 5 сброса, устанавливая в исходное состояние накопитель 4 и подтверждая исходное состояние сканирующего мультиплексора 2. Если в процессе опроса входов порогового элемента сканирующим муль.типлексором 2 оказывается, что на все входы, начиная с К-го и до п -го поданы нулевые потенциалы, то на K-l 5,. ;-м такте работы сканирую1 v щего мультиплексора 2 на выходе блока 3 контроля обнуления появляется единичный потенциал, свидетельствующий о том, что на все неопрошенные входы поданы нулевые потенциалы. При этом единичный пЬтенциал с выхода блока 3 контроля обнуления поступает на первый вход блока 5 сброса,вызывая на его первом выходе .единичный потенциал, разрешающий запись в выходной .триггер б сигнала с выхода накопителя 4 . При этом, если Illw,, то на выходе накопителя 4 в этот момент единичный потенциал, а п .1о-х- а io нулевой.. По ,-- t « окончании тактового импульса на втором входе блока 5 сброса формируется единичн1ай потенциал, устанавливающий накопитель 4 и сканирующий мультиплексор 2 в исходное состояние. После чего цикл работы мультиплексора повторяется. Если на все входы порогового элемента поданы нулевые потенциалы, то на выходе блока 3 контроля обнуаения будет единичный потенцигш, ко торый поступая на блок 5 сброса, вы зывает единичные потенциалы на его выходах ( в течение длительности так тового импульса на первом выходе и в паузу между тактовыми импульсами на втором выходе), при этом сканирующий мультиплексор и накопитель каждый такт сбрасываются в исходное состояние, а в выходной триг гер 6 записывается нулевой потенциал с выхода накопителя 4. Пороговый элемент находится в данном состояни останова до появления первого не ну л евого потенциала на его выходах, после чего единичный потенциал на выходе блока 3 контроля обнуления пропгадает и работа порогового элеме та продолжается. Очевидно, что в предлагаемом пороговом элементе для формирования выходного сигнала требуется от О п до тактов, генератора 1. , Формула изобретения Пороговый логический элемент, содержащий генератор тактовых импу сов, накопитель, выходной триггер и сканирующий мультиплексор, счетный вход , которого подключен к выходу

fM.

f r генератора тактобых импульсов, информационные входы соединены с шинами входных сигналов,а первый выход со счетным входом накопителя,выходом подключенного к информационному входу выходного триггера, о тличающийс я тем, что, с целью по&ышения быстродействия, в него введены блок сброса и блок контроля обнуления, одна группа входов которого соединена с шинами входных сигналов, другая группа входов соединена с выходами сканирующего мультиплексора, а выход подключен к первому входу блока сброса, второй вход которого соединен с вторым выходом сканирующего мультиплексора, третий вход - с выходом генератора тактовых импульсов, а четвертый вход - с выходом накопителя, при этом первый выход блока сброса подключен к установочному входу выходного триггера, а второй выход - к входам сброса сканирующего мультиплексора и накопителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР ( 598252, кл, Н 03 К 19/20, 07.05.76 2.Preceding of lEE Yoil20, 1973, № 11, p.1301-1307. Fig 4,5 (прототип)

Авторы

Даты

1982-12-07—Публикация

1980-12-01—Подача