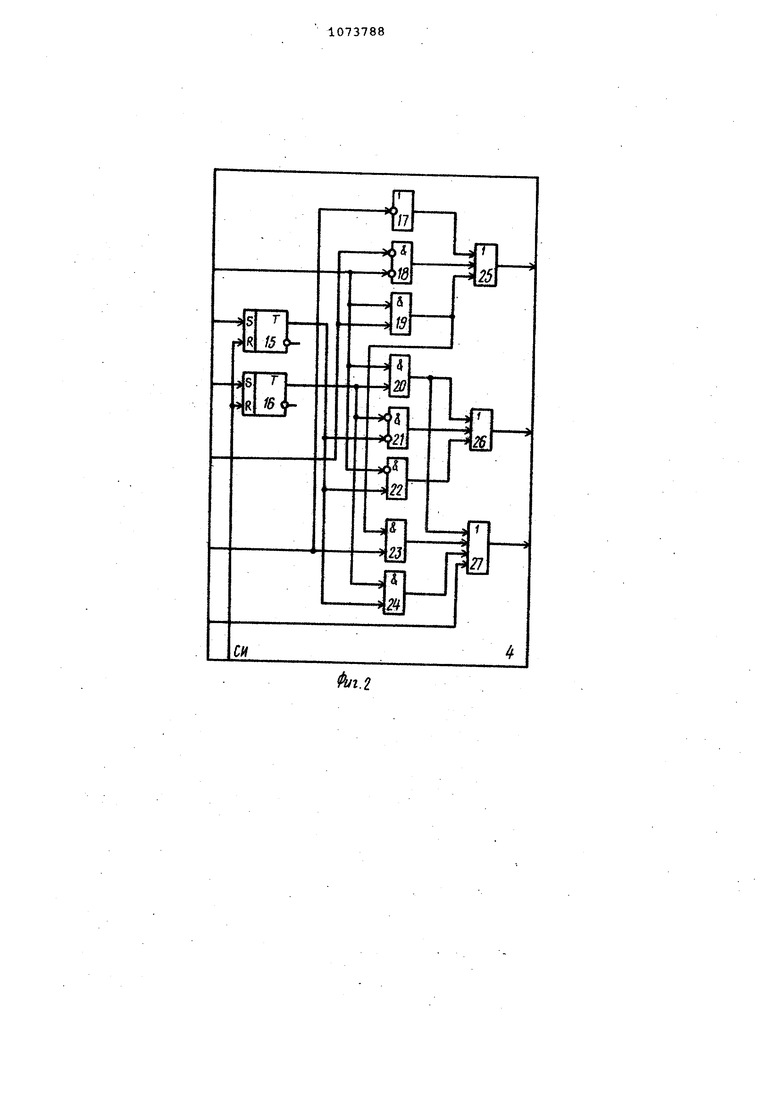

венно к первому, второму и третьему выходам формирователя сигналов, первый вход третьего элемента ИЛИ подключен к четвертому входу формирователя сигналов, вторые входы первых элементов И и И-НЕ объединен с первыми входами третьего элемента И и элемента ЗЛПРЕТ и подключены к пятому входу формирователя сигналов вторые входы первого и второго триггеров подключены соответственно к шестому и седьмому входам формирователя сигналов, выходы первого и второго триггеров соединены соответственно с первыми входами второго элемента И-НЕ, четвертого элемента И, с вторым входом элемента ЗЛПРЕТ и с вторыми входами третьего, четветого элементов И, второго элемента , выходы элемента НЕ, первого и второго элементов И-НЕ, элемента ЗАПРЕТ, второго и четвертого элементов И соединены соответственно с первым и вторыг/1 входами первого и второго элементов ИЛИ и с вторьм и третьим входами третьего элемента ИЛИ, выход первого элемента И соединен с вторым входом второго элемента И и третьим входом первого элемента ИЛИ, выход третьего элемент И соединен с третьим входом второго элемента ИЛИ и с четвертьм входом третьего элемента ИЛИ.

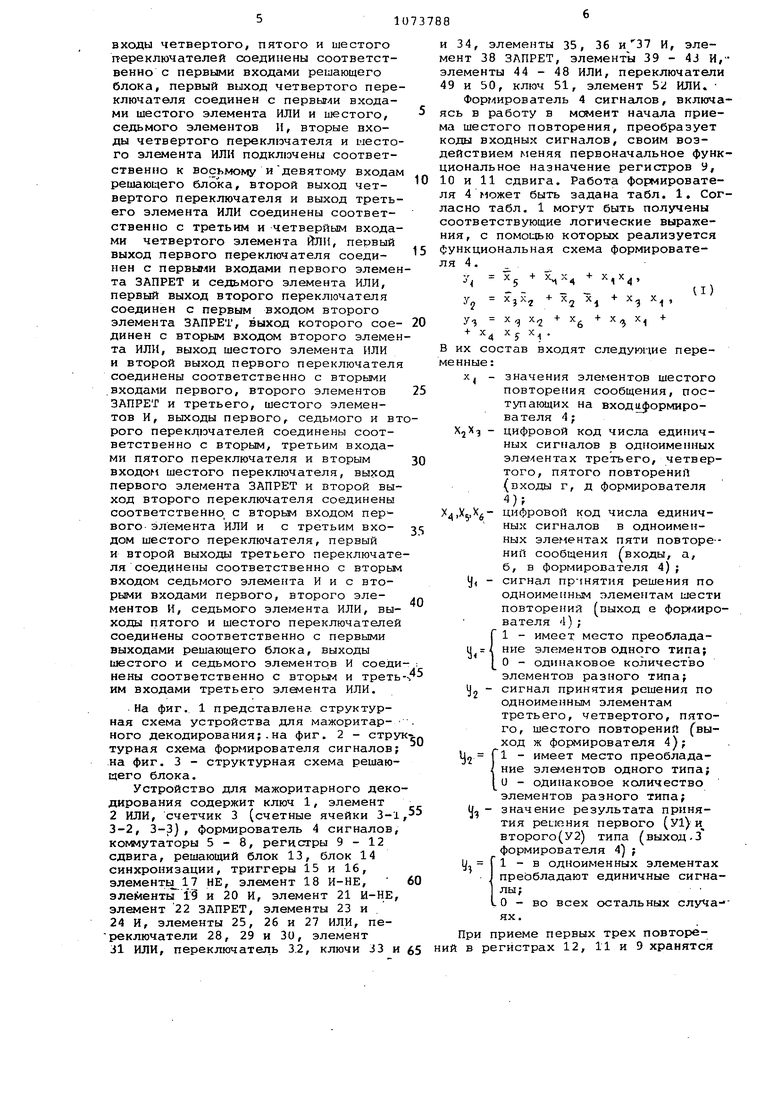

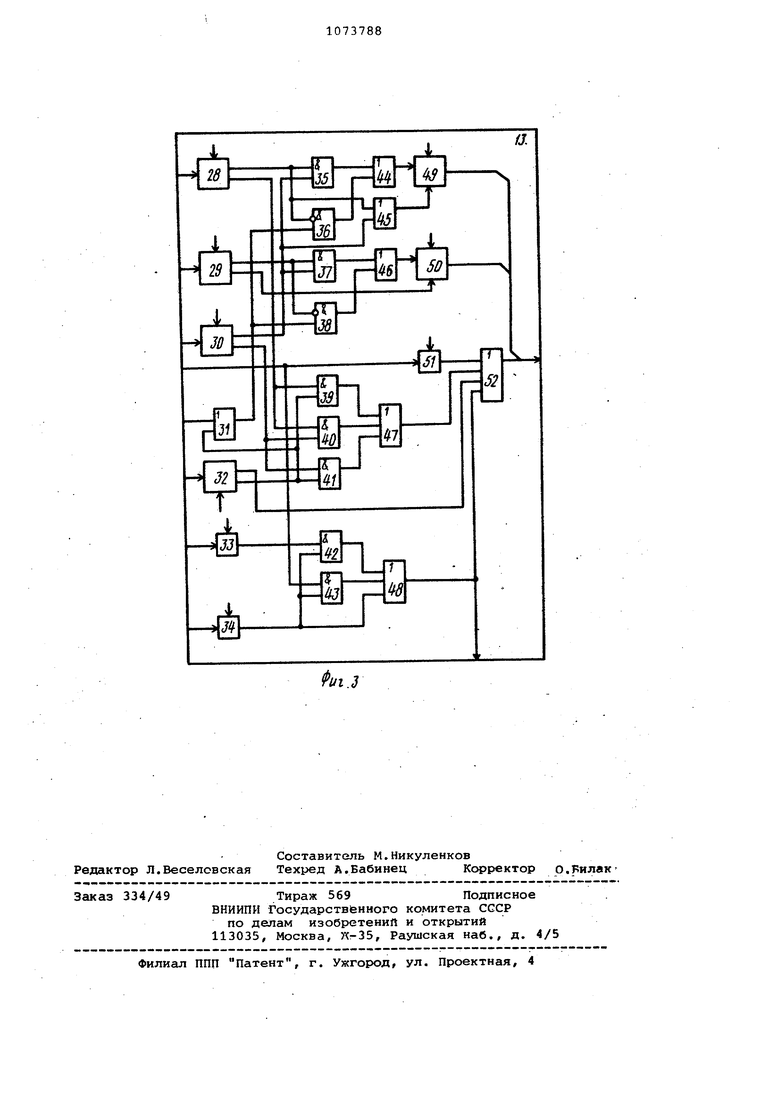

3. Устройство по п. 1, отличающееся тем, что решающий бЛок содержит переключатели, первый второй и третий ключи, первые входы которых соединены соответственно с первыми входами решающего блока, входы первого, второго и третьего переключателей подключены соответственно к второму, третьему и четвертому входам решающего блока первые вюсоды первого, второго и третьего переключателей соединены соответственно с первыми входами первого, второго и третьего элементов И, выходы которых соединены соответственно с первыгли входами первого, второго и третьего элементов JiJiH, выход первого ключа соединен с Первым входом четвертого элемента ИЛИ, выход которого подключен к. первому выходу решающего блока, первай и второй элементы ЗАПРЕТ, второ вход второго ключа подключен к пятому входу решающего блока, выход Btoporo ключа соединен с первым взгодсм четвертого элемента И, второй вход первого ключа объединен с первым входом пятого элемента И и подключен к шестому входу решающего

блока, второй вход третьего ключа подключен к седьмому входу реша1эщего блока, выход третьего ключа соединен с первым входом пятого элемента ИЛИ и с вторыми входами четвертого и пятогоэлеглентов И, выходы четвертого и пятого элементов И соединены соответственно с вторыг и третьим входами пятого элег1ента ИЛИ, выход которого соединен с вторым входом четвертого элемента ИЛИ и с вторыгд выходе решающего блока, первые входы четвертого, пятого и шестого переключателей соединены соответственно с первыми входами решающего блока, первый выход четветого переключателя соединен с первыми входами шестого элемента ИЛИ и шестого, седьмого элементов И, вторые входы четвертого переключателя и шестого элемента ИЛИ подключены соответственно к восьмому и девятому входам решающего блока, второй выход четвертого переключателя и выход третьего элемента ИЛИ соединены соответственно с третьш- и четвертым входами четвертого элемента ИЛИ, первый выход первого переключателя соединен с первыг 1и входами первого элемента ЗАПРЕТ и седьмого элемента ИЛИ первый выход второго переключателя соединен с первым входом второго элемента ЗДПPET, выход которого соединен с вторым входбм второго элемента ИЛИ, выход шестого элемента ИЛИ и второй выход первого переключателя соединены соответственно с вторыми входами первого, второго элементов ЗАПРЕТ и третьего, шестого элементов И, выходы первого, седьмого и второго переключателей соединены соответственно с вторьм, третьим входами.пятого переключателя и вторьЕ 1 входом шестого переключателя выход первого элемента ЗАПРЕТ и второй выход второго переключателя соедьнень соответственно с вторым входом первого элемента ИЛИ и с третьим входом шестого переключателя, первый и второй выходы третьего переключателя соединены соответственно с вторым входсяи седьмого элемента И и с вторьяля входами первого второго элементов И, седьмого элемента ИЛИ,выходал пятого и шестого переключателей соединены соответственно с первьв 1и выходами решающего блока, выходы atecToro и седьмого элементов И соединены соответственн с вторым и третьим входами третьего элемента ИЛИ.

Изобретение относится к телемеха нике и вычислительной технике и быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при многократном повторении сообщений.

Известно устройство для мажоританого декодирования при приеме информации по, параллельным каналам связи содерхсащее регистры и элементы И, ИЛИ, НЕ ij .

Недостатком этого устройства является отсутствие возможности декодирования кодов, с повторением, разнесенных во времени, без дополнительных буферных накопителей.

Известно устройство для мажоритарного декодирования, содержащее регистры, ключ, сумматоры, элементы И, ИЛИ, НЕ, переключатель, триггер, элемент задержки и позволяющее подвергать мажоритарной обработке три, пять и более повторений сообщения без потери промежуточных результатов 2 .

Недостатком этого устройства является низкая помехоустойчивость, поскольку анализируются не все возможные сочетания повторений сообщения.

Наиболее близким по технической сущности к предлагаемому является устройство для мажоритарного декодирования , содержащее ключ, счетчик, первый, второй и третий регистры и решаюгдий блок, первые входы которых соединены соответственно с выходами блока синхронизации, первые входы первого, второго и третьего элементов И объединены с вторым входом ключа и подключены к входу устройства, выход ключа соединен с вторым входом счетчика, выходы счетчика содинены соответственно с вторыми входами первого, второго и третьего элментов И, выходы которых соединены соответственно с вторыми входами певого, второго и третьего регистров и решающего блока, выходы первого, второго и третьего регистров соединены соответственно с третьими, четвертыми и пятыми входами решающего блока и счетчика,первый и второй выходы решающего блока подключены соответственно к третьему входу ключа и к выходу устройства.

Решающий блок содержит первый, второй и третий переключатели, первый, второй, третий, четвертый, пятый и шестой ключи, первые входы котррых подключены соответственно к первым входам решающего блока, первые входы первого, второго и третьего элементов ИЛИ соединены сосггветственно с вторими входами решающего блока, вторые входы первого, второго и третьего переключателей соединены соответственно с третьим, четвертым и пятым входами решакадего блока, выход первого переключателя соединен с nepBLDiiH входами первого, второго и третьего элементов И, выход второго переключателя соединен с первым входом четвертого элемента И и с вторыми входами первого элемента И и первого ключа,вт6.рые входы четвертого элемента И и второго ключа объединены и подключены к первому входу первого элемента ИЛИ, выход третьего переключателя соединен с вторым входом третьего элемента И, выход которого соединен с вторь ли входами первого и втого элементов ИЛИ, выходы которых соединены соответственно с вторьми входами третьего и четвертого ключей выход первого элемента И соединен с вторым вxoдo i первого элемента ИЛИ, выход четвертого элемента И соединен с вторь -чи входами второго элемента И и третьего элемента ИЛИ, выход последнего соединен с вторым входом пятого ключа и с третьим входом второго элемента ИЛИ, выход второго элемента И соединен с.вторы входом шестого ключа, выходы первого, второго, третьего, четвертого, пятого и LiincToro ключей соединены соответственно с первым, вторьм, третьим, четвертым, пятым и шестым входами четвертого элемента ИЛИ, выход которого соединен с первым и вторым выходами решапщего блока З Недостатком этого устройства яв-ляется низкая помехоустойчивость, поскольку подвергая мажоритарной обработке первые три, затем пять, семь повторений сообщения, устройство не анализирует группу, состоящую из трех или пяти повторений, сдвинутую относительно начала на два повторения, и не осуществляет мажоритарно обработки. Если интенсивному воздействию помех подвергаются четыре повторения, возникают группирующиеся ошибки (что характерно для реальных каналов связи), то известным устройством будут исправлены не все ошибки после приема cf.iecn повторени.

Цель изобретения - повышение помехоустойчивости устройства.

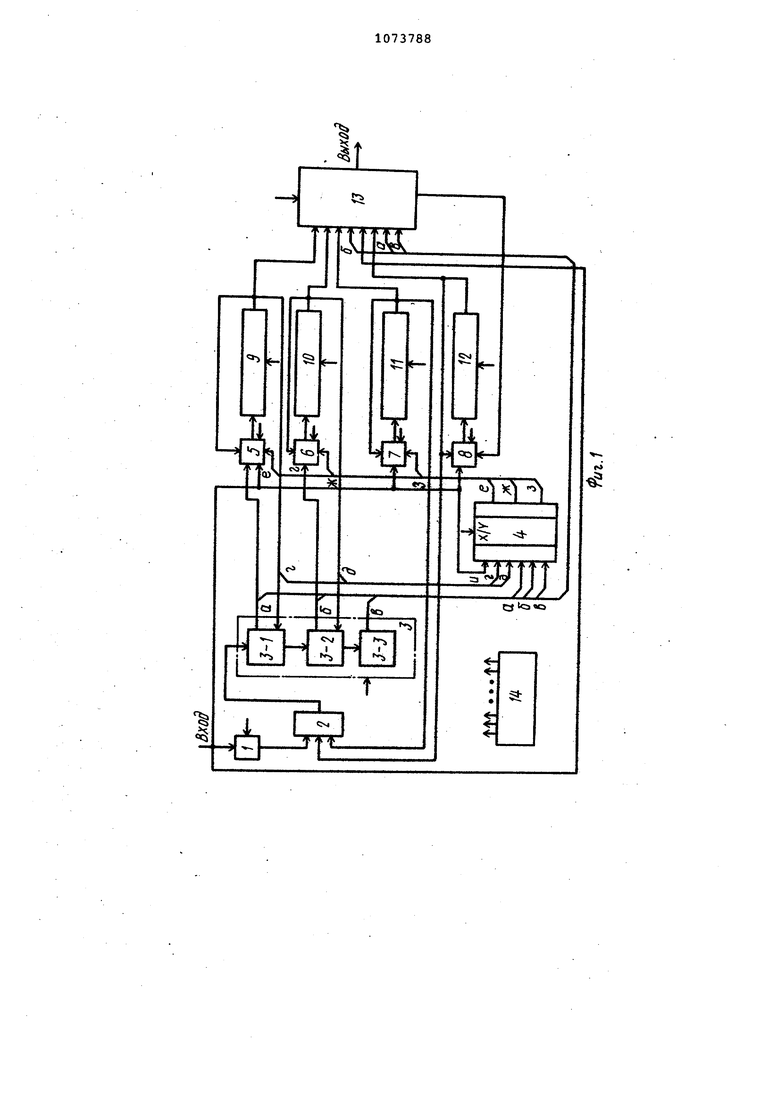

Поставленная цель достигается тем, что в устройство, содержащее ключ, счетчик, регистры и решающей блок, первые входы которых соединен соответственно с первыми входани блока синз ронизации, второй вход ключа является устройства, выходы первого и второго регистров соединены соответственно с вторыми и третьими входами счетчика и решающего блока, выход третьего регистра соединен с четвертым входом решающего блока, первые входы которого яв- ляются выходами устроПства, введены элемент ИЛИ, формирователь сигналов, коммутаторы и четвертый регистр, первые входы формирователя сигналов, четвертого регистра и первого, второго, третьего и четвертого ключей подключены соответственно к вторым выходам блока синхронизации, выход ключа соединен с первым Входом элемента ИЛИ, выход которого соединен с четверТЕЛм входом счетчика, первый и второй выходы счетчика соединены соответственно с вторьми входами первого и второго коммутаторов , вторым и третьим входами формирователя сигналов и пятым и шестым входами решающего блока, третий выход счетчика соединен с четвертым входом формирователя сигналов и седьмым входом решающего блока, выходы первого, второго, третьего и четвертого коммутаторов подключены соответственно к вторым входам первого, второго, третьего и четвертого, регистров, выходы третьего и четвертого регистров соединены соответственно с вторыми входами третьего и четвертого коммутаторов и с вторым и третьим входами элемента ИЛИ, рЫход четвертого регистра соединен с восьмым входом решающего блока, второй выхбд .которого подключен к третьему входу четвертого коммутатора первый, второй и третий выходы формирователя сигналов соединены соответственно с третьими входами первого, второго и третьего коммутаторов четвертые входы первого, третьего и четвертого коммутаторов и пятый вход формирователя сигналов объединены с девятым входом решающего блока и подключены к входУ устройства, выходы первого и второго регистров соединены соответственно с пятым вхдом первого коммутатора и четвертым входом второго коммутатора, с шестым и седьмым входами формирователя сигналов.

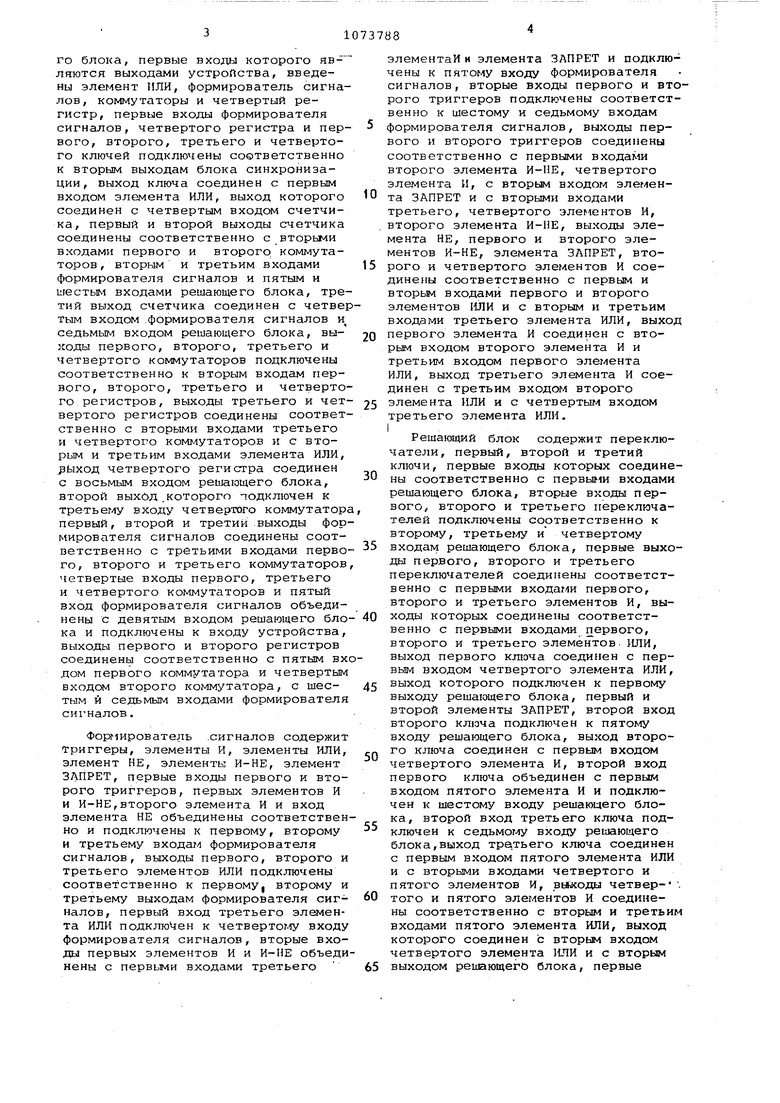

Формирователь .сигналов содержит триггеры, элементы И, элементы ИЛИ, элемент НЕ, элементы И-НЕ, элемент ЗАПРЕТ, первые входы первого и второго триггеров, первых элементов И и И-НЕ,второго элемента И и вход элемента НЕ объединены соответственно и подключены к первому, второму и третьему входам формирователя сигналов, выходы первого, второго и третьего элементов ИЛИ подключены соответственно к первому, второму и третьему выходам формирователя сигналов, первый вход третьего элемента ИЛИ подключен к четвертому входу формирователя сигналов, вторые входы первых элементов И и И-НЕ объединены с первыми входами третьего

элементам и элемента ЗАПРЕТ и подключены к пятому входу формирователя сигналов, вторые входы первого и втрого триггеров подключены соответственно к шестому и седьмому входам формирователя сигналов, выходы первого и второго триггеров соединены соответственно с первыми входаь-то второго элемента И-НЕ, четвертого элемента И, с вторьви входом элемента ЗАПРЕТ и с вторыми входами третьего, четвертого элементов И, второго элемента И-НЕ, выходы элемента НЕ, первого и второго элементов И-НЕ, элемента ЗАПРЕТ, второго и четвертого эле лентов И соединены соответственно с первьЕ«1 и вторьм входами первого и второго элементов 1-ШИ и с вторым и третьим входами третьего элемента ИЛИ, выхо первого элемента И соединен с вторьм входом второго элемента И и третьим входом первого элемента ИЛИ, выход третьего элемента И соединен с третьим входом второго элемента ИЛИ и с четвертым входом третьего элемента ИЛИ, 1

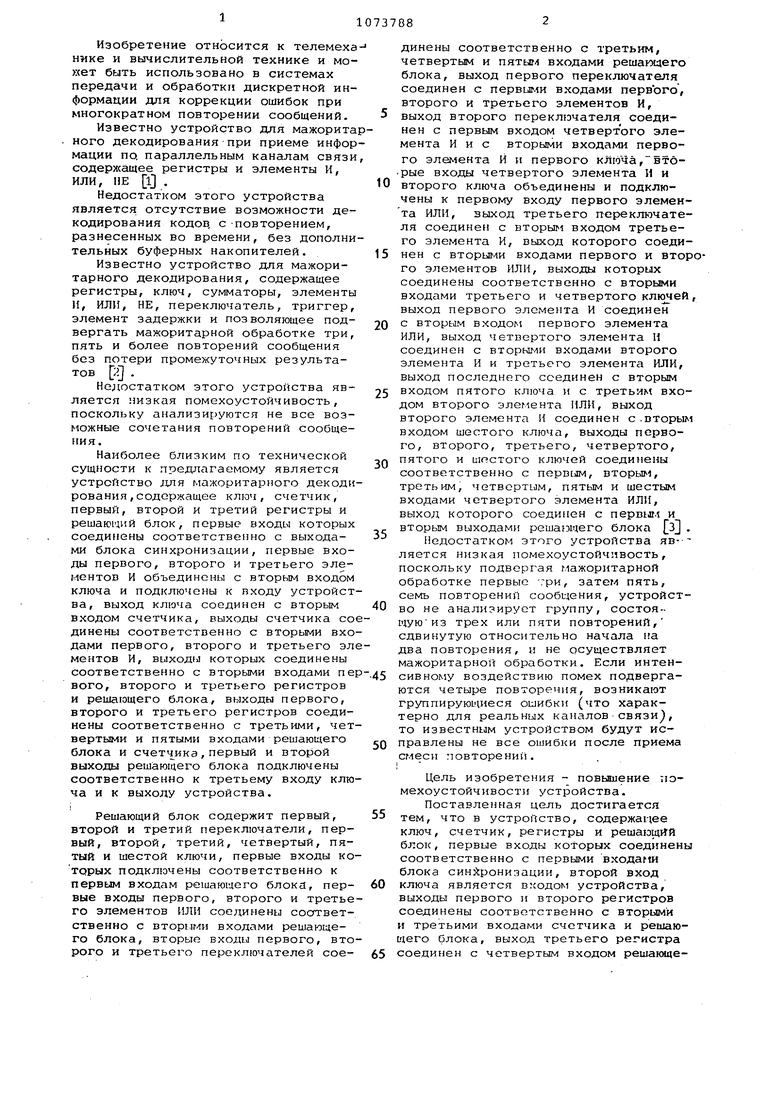

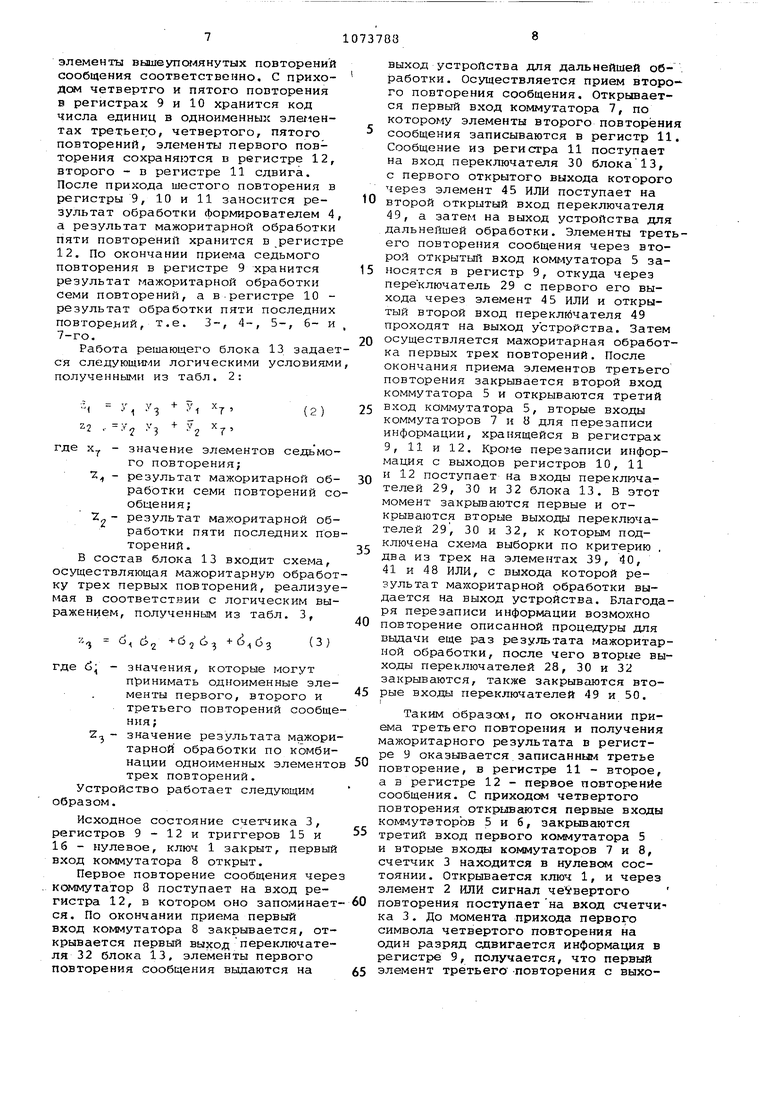

Решающий блок содержит переключатели, первый, второй и третий ключи, первые входы которых соединены соответственно с первьаш входами решающего блока, вторые входы первого второго и третьего переключателей подключены соответственно к второму, третьег/1у и четвертому входам решающего блока, первые выходы первого, второго и третьего переключателей соединены соответственно с первьвли входами первого, второго и третьего элементов И, выходы которых соединены соответственно с первыми входами первого, второго и третьего элементов. ИЛИ, выход первого ключа соеди ен с первым входом четвертого элемента ИЛИ, выход которого подключен к первому выходу решающего блока, первый и второй элементы ЗАПРЕТ, второй вход второго кл1ача подключен к пятому входу решающего блока, выход второго ключа соединен с первым входсяи четвертого элемента И, второй вход первого ключа объединен с первым входом пятого элемента И и подключен к шестому входу решакадего блока, второй вход третьего ключа подключен к седьмого входу решающего блока,выход TpeiTbero ключа соединен с первым входом пятого элемента ИЛИ и с вторыми входами четвертого и пятого элементов И, вьЛходы четвертого и пятого элементов И соединены соответственно с вторым и третьи входами пятого элемента ИЛИ, выход которого соединен с вторьм входом четвертого элемента ИЛИ и с вторым выходом решающего блока, первые входы четвертого, пятого и шестого г ереключателей соединены соответственно с первыми входами решающего блока, первый выход четвертого пере ключателя соединен с первьгу1и входами шестого элемента ИЛИ и шестого, седьмого элементов И, вторые входы четвертого переключателя и шесто го элемента ИЛИ подключены соответственно к восьмому и девятому входа решающего блока, второй выход четвертого переключателя и выход треть его элемента ИЛИ соединены соответственно с третьим и четверйым входа ми четвертого элемента ИЛИ, первый выход первого переключателя соединен с первыг и входами первого элеме та ЗАПРЕТ и седьмого элемента ИЛИ, первый выход второго переключателя соединен с первым входом второго элемента ЗАПРЕТ, выход которого сое динен с вторым входом второго элеме та ИЛИ, выход шестого элемента ИЛИ и второй выход первого переключател соединены соответственно с вторыми .входами первого, второго элементов ЗАПРЕТ и третьего, шестого элементов И, выходы первого, седьмого и в рого переключателей соединены соответственно с вторым, третьим входами пятого переключателя и вторым входом шестого переключателя, выход первого элемента ЗАПРЕТ и второй вы ход второго переключателя соединены соответственно, с вторым входом первого- элемента ИЛИ и с третьим входом шестого переключателя, первый и второй выходы третьего переключат ля соединены соответственно с вторым входом седьмого элемента И и с вторыми входами первого, второго элементов И, седьмого элемента ИЛИ, выходы пятого и шестого переключателей соединены соответственно с первыми выходами решающего блока, выходы шестого и седьмого элементов И соеДи иены соответственно с вторьте и треть им входами третьего элемента ИЛИ. На фиг. 1 представлена структурная схема устройства для мажоритарного декодирования;.на фиг. 2 - стру турная схема формирователя сигналов на фиг. 3 - структурная схема решающего блока. Устройство для мажоритарного деко дирования содержит ключ 1, элемент 2 ИЛИ, счетчик 3 (счетные ячейки З3-2, 3-3), формирователь 4 сигналов коммутаторы 5-8, регистры 9-12 сдвига, решающий блок 13, блок 14 синхронизации, триггеры 15 и 16, элементы 17 НЕ, элемент 18 И-НЕ, элементы 19 и 20 И, элемент 21 И-НЕ элемент 22 ЗАПРЕТ, элементы 23 и . 24 И, элементы 25, 26 и 27 ИЛИ, переключатели 28, 29 и 30, элемент 31 ИЛИ, переключатель 3.2, ключи 33 и 4, элементы 35, 36 И, элет 38 ЗАПРЕТ, элементы 39 - 4J И,енты 44 - 48 ИЛИ, переключатели и 50, ключ 51, элемент 52 ИЛИ. Форг/1ирователь 4 сигналов, включав работу в момент начала приеестого повторения, преобразует входных сигналов, своим возствием меняя первоначальное функнальное назначение регистров У, и 11 сдвига. Работа формировате4 Может быть задана табл. 1. Согно табл. 1 могут быть получены тветствующие логические выраже, с помощью которых реализуется кциональная схема формировате4 . - 5 4. Х2 Х + Х + X X + Х Ху Х. х состав входят следующие переные:х - значения элементов шестого повторения сообщения, поступающих на входиформирователя 4; Хз - цифровой код числа единичных сигналов в одноименных элеглентах третьего, четвертого, пятого повторений (входы г, д формирователя 4); Цифровой код числа единичных сигналов в одноименных элементах пяти повторе-ний сообщения (входы, а, б, в формирователя 4); сигнал прчнятия решения по одноименным элементам шести повторений выход е форг 1ирователя 4); 1 - имеет место преобладание элементов одного типа; О - одинаковое количество элементов разного типа; сигнал принятия решения по одноименным элементам третьего, четвертого, пятого, шестого повторений (выход ж формирователя 4); J2 fl - имеет место преобладаI ние эле лентов одного типа; и - одинаковое количество элементов разного типа; tj - значение результата принятия реиюния первого (У1) и второго(У2) типа (выход-З формирователя 4 ; f 1 - в одноименных элементах преобладают единичные сигналы; .О - во всех остальных случа-ях. ри приеме первых трех повторев регистрах 12, 11 и 9 хранятся элементы вьлиеупоглянутых повторений сообщения соответственно. С приходсм четвертго и пятого повторения в регистрах 9 и 10 хранится код числа единиц в одноименных элепентах третьего, четвертого, пятого повторений, элементы первого повторения сохраняются в регистре 12, второго - в регистре 11 сдвига. После прихода шестого повторения в регистры 9, 10 и 11 заносится результат обработки формирователем 4 а результат мажоритарной обработки пяти повторений хранится в регистре 12. По окончании приема седьмого повторения в регистре 9 хранится результат мажоритарной обработки семи повторений, а в-регистре 10 результат обработки пяти последних повторе.ний, т.е. 3-, 4-, 5-, 6- и 7-го. Работа решающего блока 13 задает ся следующигли логическими условиями полученными из табл. 2: i У, У- У, г 2 . УЗ 2 V где х - значение элементов седьмого повторения; Z - результат мажоритарной обработки семи повторений со обшения; Zy - результат мажоритарной обработки пяти последних пов торений. В состав блока 13 входит схема, осуществляющая мажоритарную обработ ку трех первых повторений, реализуе мая в соответствии с логическим выражением, полученным из табл. 3, 6 cio -t-fJ, 6. где (J - значения, которые могут принимать одноименные элементы первого, второго и третьего повторений сообщ ния; Z - значение результата мажори тарной обработки по комби нации одноименных элементо трех повторений. Устройство работаегт следующим образом. Исходное состояние счетчика 3, регистров 9 - 12 и триггеров 15 и 16 - нулевое, ключ 1 закрыт, первый вход коммутатора 8 открыт. Первое повторение сообщения чер коммутатор 8 поступает на вход регистра 12, в котором оно запоминае ся. По окончании приема первый вход коммутатора 8 закрывается, от крывается первый выход переключате ля 32 блока 13, элементы первого повторения сообщения выдаются на выход устройства для дальнейшей об- . работки. Осуществляется прием второ го повторения сообщения. Открьлвается первый вход коммутатора 7, по которому элементы второго повторения сообщения записываются в регистр 11. Сообщение из регистра 11 поступает на вход переключателя 30 блока13, с первого открытого выхода которого через элемент 45 ИЛИ поступает на второй открытый вход переключателя 49, а затем на выход устройства для дальнейшей обработки. Элементы третьего повторения сообщения через второй открытый вход коммутатора 5 заносятся в регистр 9, откуда через переключатель 29 с первого его выхода через элемент 45 ИЛИ и открытый второй вход переключателя 49 проходят на выход устройства. Затем осуществляется мажоритарная обработка первых трех повторений. После окончания приема элементов третьего повторения закрывается второй вход коммутатора 5 и открываются третий Бход коммутатора 5, вторые входы коммутаторов 7 и У для перезаписи информации, хранящейся в регистрах 9, 11 и 12. Кроме перезаписи информация с выходов регистров 10, 11 и 12 поступает на входы переключателей 29, 30 и 32 блока 13. В этот момент закрываются первые и открываются вторые выходы переключателей 29, 30 и 32, к которым подключена схема выборки по критерию , два из трех на элементах 39, 40, 41 и 48 ИЛИ, с выхода которой результат мажоритарной обработки выдается на выход устройства. Благодаря перезаписи информации возможно повторение описанной процедуры для выдачи еще раз результата мажоритарной обработки, после чего вторые выходы переключателей 28, 30 и 32 закрываются, также закрывгиотся вторые входы переключателей 49 и 50. I Таким образом, по окончании приема третьего повторения и получения мажоритарного результата в регистре 9 оказывается записанным третье повторение, в регистре 11 - второе, а в регистре 12 - первое повторение сообщения. С приходом четвертого повторения открываются первые входы коммутаторов 5 и б, закрываются третий вход первого коммутатора 5 и вторые входы коммутаторов 7 и 8, счетчик 3 находится в нулевсм состоянии . Открывается ключ 1, и через элемент 2 ИЛИ сигнал че1вертого повторения поступает на вход счетчика 3. До момента прихода первого символа четвертого повторения на один разряд сдвигается информация в регистре 9, получается, что первый элемент третьего -повторения с выхода регистра 9 поступает на установочный вход первого разряда 3-1 .сче чика 3. Если этот эле1лент 1, то первый разряд счетчика 3 устанавливается в это же состояние. Если первый элемент четвертого повтореНИН также 1, то состояние счетчика 3 изменяется - первый разряд устанавливается в Q, а второй разряд в 1. При считывании состояний счетчика в первый разряд регист ра 9 записывается О, а в первый разряд регистра 10 - 1. Далее счетчик В сбрасывается в ноль, информация в регистрах 9 и 10 сдвигается на один разряд, и счетчик 3 устанавливаетсяв состояние, соответствующее второму элементу третье го повторения. С приходом очередног элемента четвертого повторения процесс обработки повторяется. При приеме каждого элемента пятого повторения состояние первого и вторго разрядов счетчика 3 может оказаться в одном из следующих состояний: 00, 10, 01, 11, - определяющих код числа единиц в одноименных элементах трех повторений (третьего, четвертого и пятого). По Данным можно получить результат мажоритарной обработки трех вышеупомянутых повторений, используя следующее правило. Информация 1 формируется и выдается на выход устройства в тех случаях, когда счетчик 3 находится в состоянии 01, 11 (две или три единицы из трех возможных). Информационный О фор 4ируется и выдается на выход устройства для состояний 00 и 10 счетчика 3 (три или два из трех возможных). Следовательно, информационные элементы могут непосредственно формироваться по состоянию второго раз ряда счетчика 3. поступая .на четвертый вход решающего блока 13, информационные элементы результата ма жоритарной обработки через открытый ключ 51 и элемент 52 ИЛИ выдаются на выход устройства для дальнейшей обработки. Если результат мажори- тарной обработки два из трех необходимо выдать повторно, то содержимое регистра 10 поступает в решающи блок 13 на второй вход, где через переключатель 29 со второго его выхода по второму открытому входу переключателя 50 выдается на выход ;устройства. С мсмента окончания приема пятого повторения закрываются ключи 1 и 51, на коммутаторах и 6 . отклю чаются первые входы, подключаются на коммутаторе 5 четвертый вход, на -к мутаторак 6 и 7 - третьи входы, открывается третий вход коммутатора 8. Затем продолжается прием шестого повторения. До момента поступления первого элемента шестого повторения на первый вход формирователя 4 происходит сдвиг кнфс(1ации в регистрах 9 и 10. Элементы, считываемые с регистров 9 и 10, поступая на установочные входы разрядов 3-1, 3-2 счетчика 3, формируют код числа принятых единиц для каждого разряда сообщений по трем принятым повторениям (третьему, четвертому, пятому. Код, считываемый с выходов регистров 9 и 10, поступает на входы , формирователя 4, устанавливает триггеры 15 и 16 в положение считываемого цифрового кода. За время следования первого элемента шестого повторения происходит поочередйьЙ сдвиг на один разряд информации, хранящейся в регистрах 11 и 12, которая через элемент 2 ИЛИ поступает на вход счетчика J, изменяя цифровой код числа единиц в соответствующиз элементах трех повторений до кода числа единиц в соответствующих символах первих пяти повторений, код с выходов ; ;тика 3 поступает на входы Q, S, Ь формирователя 4, где совместно с первым элементом шестого повторения и запомненным кодом числа единиц в соответствующих элементах третьего, четвертого, пятого повторений на триггерах 15 и 16 поступает на вход схемы, реализующей логические выражения (1). Выходные сигналы у , у , у , формирующиеся в соответствии с выражением (1), записываются в регистры 9, 10, 11, проходя по четвертому oткpытo 1y входу коммутатора 5 и третьим входам коммутаторов б и 7. В это же время Цифровой код числа единиц в соответствующих элементах пяти повторений поступает с в лходов Q , 5 , В счетчика 3 на соответствующие входы блока 13, где через открытые на время спедования шестого повторения ключи 33 и 34 подаются на схему вьщачи результата мажоритарной обработки три из пяти, которая для состояний 110, 001, 101 формирует единицу, а для состояний 000, 100, 010 - ноль. Результат с выхода элемента 48 ИЛИ поступает через коммутатор 8 в регистр 12, где запоминается для случая повторной выдачи, а также подается через элемент 52 ИЛИ на выход устройства для дальнейшей обработки. Перечисленные операции повторяются для всех элементов шестого повторения, но предварительно перед приходом кагвдого нового элемента шестого повторения триггеры 15 и 16 и счетчик 3 обнуляются. По окончании приема шестого повторения в регистрах 9, 10 и 11

хранятся результаты обработки формирователем 4, а в регистре 12 результат мажоритарной обработки г три из пяти, который в случаенеобходимости выдается повторно через переключатель 32 блока 13 на выход устройства.

Перед приходом элементов седьмого повторения закрываются четвертый вход коммутатора 5, третьи входы коммутаторов 6, 7 и 8, счетчик 3 устанавливается в ноль; вторые входы переключателей 49 и 50 и первый выход переключателя 32 .закрываются . Открываются первый вход коммутатора 8, третий вход коммутатора 5, вторые входы коммутатора 6 и 7, первые выходы переключателей 28, 9 и 30 и первые входы переключателей 49 и 50.

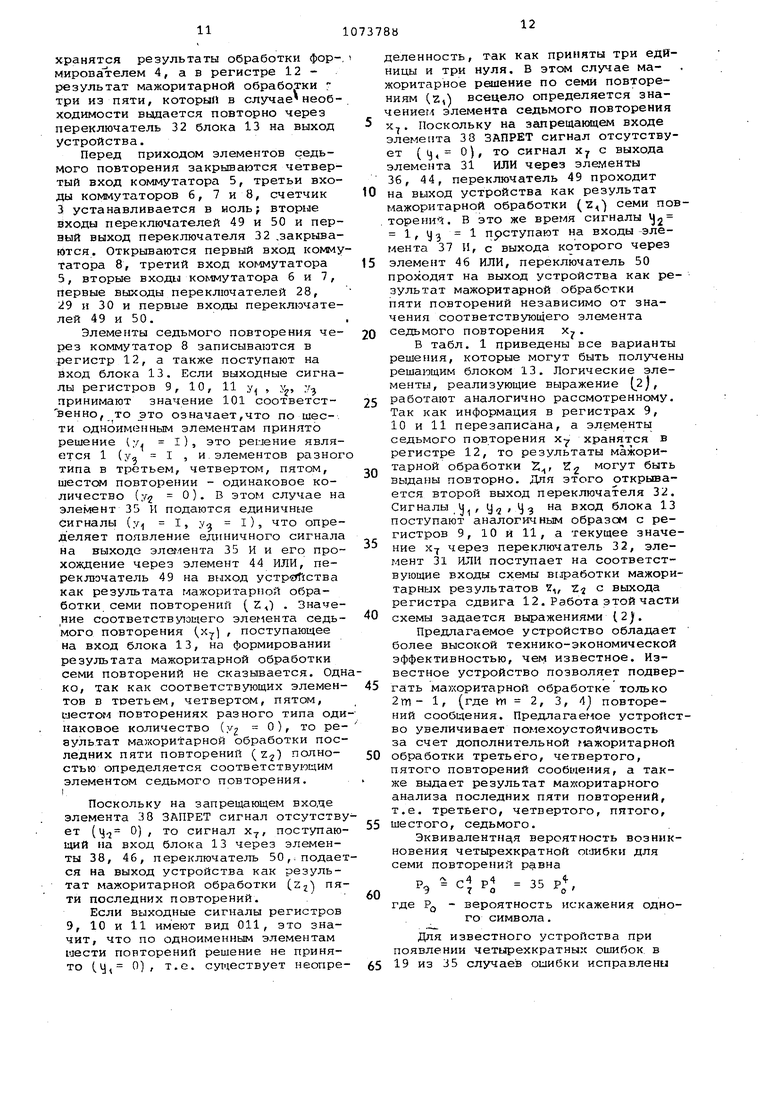

Элементы седьмого повторения через коммутатор В записываются в регистр 12, а также поступают на вход блока 13. Если выходные сигналы регистров 9, 10, 11 у , у, у принимают значение 101 соответственно, то это означает,что по шести одноименным элементам принято решение (у. 1), это реыение является 1 (у„ I , и элементов разног типа в третьем, четвертом, пятом, шестс 1 повторении - одинаковое количество (у2 0). В этом случае на элемент 35 И подаются единичные сигналы (у I, у I), что определяет появление единичного сигнала на выходе элеглента 35 И и его прохождение через элемент 44 ИЛИ, переключатель 49 на вьлход устрггйства как результата мажоритарной обработки семи повторений (Z,) . Значе,ние соответствующего элемента седьмого повторения (у.- , поступающее на вход блока 13, на формировании результата мажоритарной обработки семи повторений не сказывается. Однко, так как соответствующих элементов в третьем, четвертом, пятом, шестом повторениях разного типа одинаковое количество (у 0)г реаультат мажоритарной обработки последних пяти повторений (z) полностью определяется соответствующим

элементом седьмого повторения.

I

Поскольку на запрещающем входе элемента 38 ЗАПРЕТ сигнал отсутствует (4-2 0) , то сигнал х-, поступающий на вход блока 13 через элементы 38, 46, переключатель 50,1 подается на выход устройства как результат мажоритарной обработки (z) пяти последних повторений.

Если выходные сигналы регистров 9, 10 и 11 имеют вид 011, это значит, что по одноименным элементам шести повторений решение не принято (.Ч 0) , т.е. сугчествует неопределенность, так как приняты три единицы и три нуля. В этом случае мажоритарное решение по семи повторениям (z,) всецело определяется значением элемента седьмого повторения

х. Поскольку на запрещаквдем входе элемента 38 ЗАПРЕТ сигнал отсутствует (j, 0), то сигнал х с выхода элемента 31 ИЛИ через элементы 36, 44, переключатель 49 проходит

0 на выход устройства как результат

мажоритарной обработки (2,) семи пов.торений. В это же время сигналы VJ2 1, Уз прступают на входы-элемента 37 И, с выхода которого через

5 элемент 46 ИЛИ, переключатель 50

проходят на выход устройства как результат мажоритарной обработки пяти повторений независимо от значения соответствующего элемента

0 седьмого повторения х.

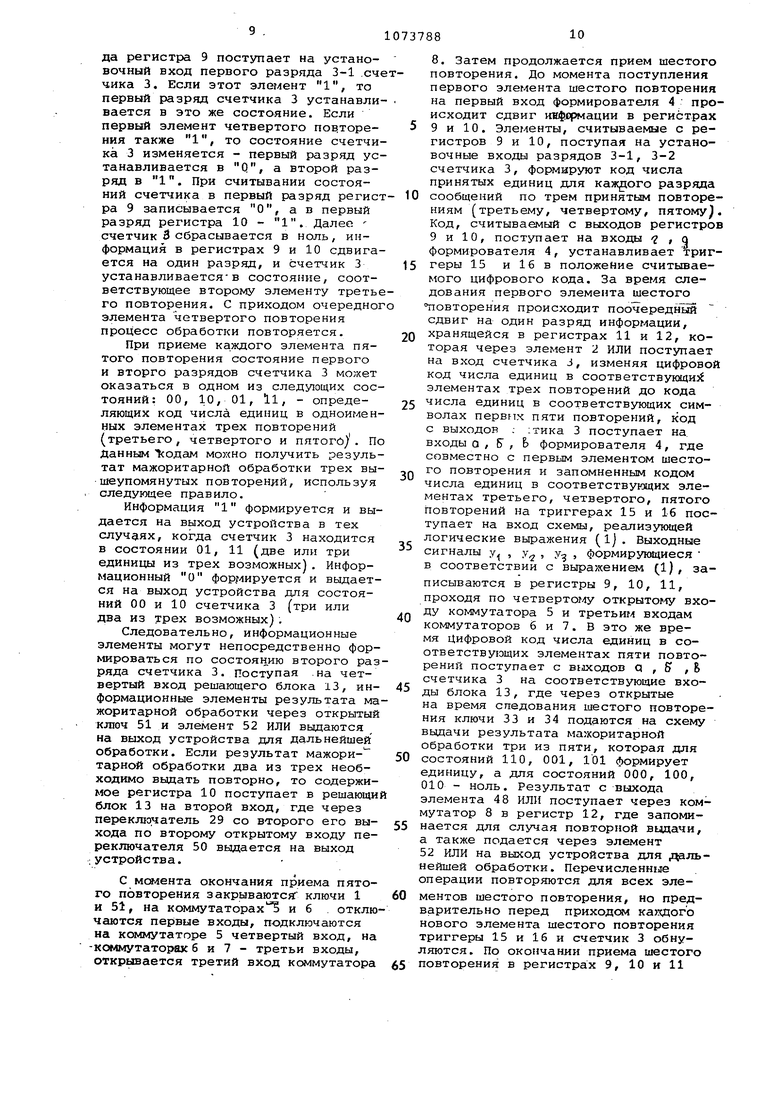

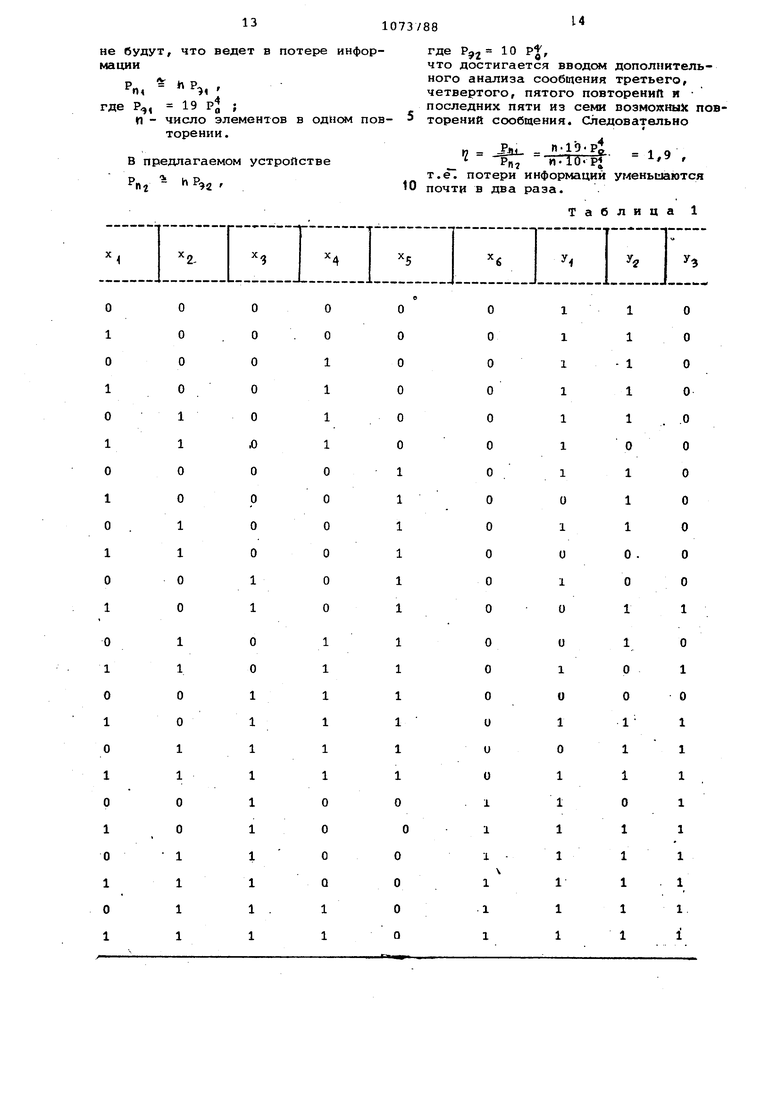

В табл. 1 приведены все варианты решения, которые могут быть получены решающим блоком 13. Логические элементы, реализующие выражение (2),

5 работают аналогично рассмотренному. Так как информация в регистрах 9, 10 и 11 перезаписана, а элементы седьмого повторения х- хранятся в регистре 12, то результаты мажори,, тарной обработки Z, И2 могут быть выданы повторно. Для этого открывается второй выход переключателя 32. Сигналы ij, у,2Чз вход блока 13 поступают аналогичным образом с регистров 9, 10 и 11, а текущее значе ние x-f через переключатель 32, элемент 31 ИЛИ поступает на соответствующие входы схемы выработки мажоритарных результатов 7,, 2 с выхода регистра сдвига 12. Работа этой части

0 схемы задается выражениями (2).

Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное. Известное устройство позволяет подвер5 гать мажоритарной обработке только 2т- 1, (где ш 2, 3, 4J повторений сообщения. Предлагаемое устройство увеличивает помехоустойчивость за счет дополнительной мажоритарной

0 обработки третьего, четвертого,

пятого повторений сообщения, а также выдает результат махгаритарного анализа последних пяти повторений, т.е. третьего, четвертого, пятого,

5 шестого, седьмого.

Эквивалентная вероятность возникновения четырехкратной ог-либки для семи повторений равна

РЭ с, Р

45 Р

° °

где PQ - вероятность искажения одного символа.

Для известного устройства при появлении четырехкратных ошибок в 19 из 35 случаев ошибки исправлены не будут, что ведет в потере информацииРП, Р, где Р, 19 Р ; П - число элементов в однсм пов торении. где Рз,2 10 Р, что достигается вводом дополнительного анализа сообщения третьего, четвертого, пятого повторений и последних пяти из семи возможных повторений сообщения. Следовательно

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для приема и мажоритарного декодирования информации | 1981 |

|

SU980114A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1978 |

|

SU884163A1 |

| Устройство для мажоритарного декодирования в целом | 1984 |

|

SU1243101A1 |

| Модифицированное устройство коррекции ошибок | 2016 |

|

RU2635253C1 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

1. УСТРОЙСТВО ДЛЯ 1У1АЖОРИ- . ТАРНОГО ДЕКОДИРОВАНИЯ, содеряащее ключ, счетчик, регистры и реиающий блок, первые входы KOTOPI-OX соединены соответственно с перпими входами блока синхронизации, второй вход ключа является входом устройства, выходы первого и второго регистров соединены соответственно с вторьоми и третьими входами счетчпка и peuiai щего блока, выход третьего регистра соединен с четвертыг/i входом решающего блока, первые выходы которого являются выходами устройства, о т л и ч а п щ е е с я теп, что, с целью повышения помехоустойчивости устройства,в него введены элемент ИЛИ, формирователь сигналов, коммутаторы и четвертый регистр, первые входы формирователя сигналов, четвертого регистра и первого, второго, третьего и четвертого ключей подключены соответственно к вторьм выходам блока синхронизапии, выход ключа соединен с первым входом элемента ИЛИ, выход которого соединен с четверти; входом счетчика, первый и второй выходы счетчика соединены соответственно с вторыми входами первого и второго комг утаторов, втopы I и третьим входами формирователя сигналов и пят1-1м и шестым входами решающего блока, третий выход счетчика соединен с четвер тым входом формирователя сигналов и седьмым входом решающего блока, выходы первого, второго, третьего и четвертого коммутаторов подключены соответственно к вторым входам первого, второго, третьего и четвертого регистров, выходы третьего и четвертого регистров соединены соответственно с вторыми входами третьего и четвертого коммутаторов и с вторырд и третьим входами элемента ИЛИ,выход четвертого регистра соединен с восьг сым входом решающего блока, второй выход кот торого подключен С третьему входу (Л четвертого коммутатора, первый, второй и третий выходы формирователя с: сигналов соединены соответственно с третьими входами первого, второго и третьего кo 1г/Iyтaтopoв, четвертые входы первого, третьего и четвертого коммутаторов и пятый вход формирователя сигналов объединены с девятым входом решающего блока и подключены к входу устройства, выходы-первого и второго регистров соединены соответственно с пятым входом первого 00 коммутатора и четвертым входом рого коммутатора, с шестым и седьглым входами формирователя сигналов. СХ5 2. Устройство по п. 1, отли00 чающееся тем, что формирователь сигналов содержит триггеры; элементы И, элементы ИЛИ, элемент НЕ, элементы И-НЕ, элементы ЗАПРЕТ, первые вхо)цы первого и второго триггеров, первых элементов и и Ит-НЕ, второго элемента И и вход элег.1ента НЕ объединены соответственно и подключены к первому, второму и третьему входам формирователя сигналов, выходы первого,второго и третьего элементов ИЛИ подключены соответст

о 1 о 1 о 1 о 1 о 1 о 1 о 1

о о о о о о о о 1 1 1 1 1 1

о о

о о

1 1 1 1 о о 1 1 1 1

О 1 О 1 О

о о 1 1 о о 1 1

1 о

1

о

1

о

1

о

о

о

о

о

1

1

1

1

1

Таблица 3

о о о о 1 1 1 1

о о о 1 о 1 о 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптивное мажоритарное устройство | 1974 |

|

SU495767A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-15—Публикация

1982-04-23—Подача