;54) АДАПТИВНЫЙ ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1480127A1 |

| Цифровое устройство для измерения частоты | 1982 |

|

SU1114966A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Цифровой вольтметр | 1988 |

|

SU1597756A2 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Вычислитель оценки математического ожидания случайного процесса | 1980 |

|

SU932502A1 |

Изобретение относится к вычислительной технике и может быть использовано, например, при автоматизации статистической обработки результатов измерений.

Известно устройство для оценки математического ожидания, содержащее аналого-цифровой преобразователь, генератор импульсов опроса, два временных селектора, триггер, делитель частоты и счетчик импульсов ij.

Однако это устройство Не обеспечивает необходимой точности оценки, так как объем выборки рстается постоянным для всего диапазона изменения оцениваемого параметра.

Наиболее близким по технической сущности к предлагаемому является адаптивный вычислитель оценки математического ожидания, содержащий источник чисел выборки, счетчик, первый регистр, ключи, два блока элементов И, формирователь управляющих сигналов и сумматор, подключенный информационными входами к разрядным выходам источника чисел выборки, управляющий выход которого соединен с первым управляющим входом сумматора и с первым входом формирователя управляющих сигналов, подключенного первым выходом к управляющему входу источника чисел выборки и к четному входу счетчика, выходца которого соединены со входами второго блока элементов И, выход которого подключен к первому входу первого ключа, второй вход которого соединен с выходом первого блока элементов И, информационные входы которого объединены с информа10ционны11да входами первого регистра и подключены к выходам сумматора, выход второго ключа соединен со вторым входом формирователя управляющих сигналов, первый управляющий вход первого

15 регистра соединен с третьим входом формирователя управляющих, сигналов {J2j,

Недостаток этого устройства сое- тоит в его невысокой точности, что

20 обусловлено тем, что в этом устройстве объем выборки п чисел х определяется автоматически в зависимости от истинного значения измеряемой величины а (здесь , где Д - не25зависимые одинаково распределенные случайные величины с нулевым средним

и дисперсией 0

представляющие

собой случайные ошибки измерений)

согласно следующим условиям:

30

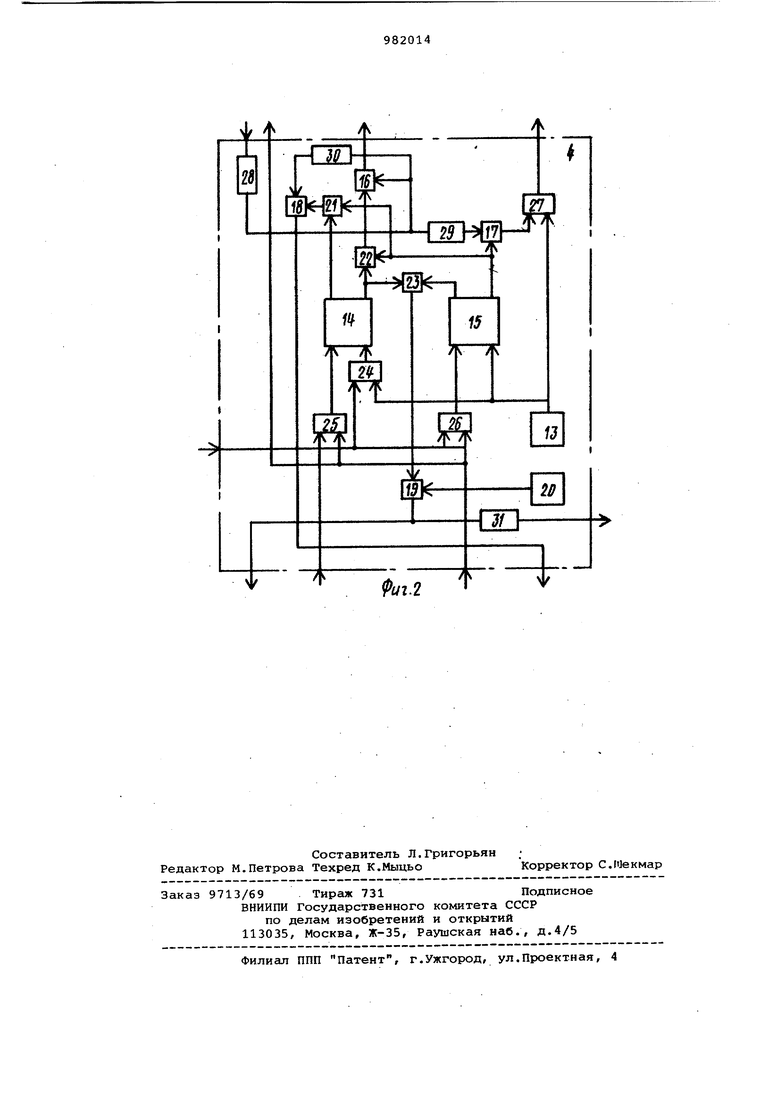

А) Число п имеет вид п 2, k О ; IB) Xi ft ТГ. (здесь 2 - регулируе .ь«й параметр устройства). В результа те оказывается, что п л --а (с превышением, порождаемым выполне1нием условия А), т.е. объем выборки обратно пропорционален (с указанным превышением) измеряемой величине. Однако, как показывает анализ, для получения строго постоянной относительной погрешности во всем диапазоне (а ,.a,i) возможных значений а функ циональная зависимость ) должна быть иной. Пусть относительная ошибка оценивается величиной f{a)3Sp,/a,(2) где (J - дисперсия величины, Д а-1н|и, or где Гц Требование (a). у г Явокл1: с учетом (2) к формуле эо с , эег (;-) т.е. объем.выборки должен быть обрат но пропорционален не самой величине а, как это реализует прототип, а ее квадрату. Следовательно, хотя данное устройство дает гораздо лучшие результаты, чем устройства, в которых объем выборки вообще не зависит от измеряемой величины, оно все же не обеспечивает постоянства относительной по.грешности во всем диапазоне возможных значений а. Цель изобретения - повышение точности устройства. Для достижения поставленной цели в адаптивный вычислитель оцейки мате матического ожидания, содержащий источник чисел выборки, разрядные выходы которого подключены к информационным входам сумматора, первый управляющий вход которого объединен с первым входом формирователя управляющих сигналов и соединен с управляю щим выходом источника чисел выборки управляющий вход которого объединен со счетным входом счетчика .и подключен к первому выходу формирователя управляющих сигналов, второй выход формирователя управлякнцих сигналов соединен с управляющим входом перво блока элементов И, информационные входы которого объединены с информа ционными входами первого регистра и подключены к информационным выходам сумматора, выход первого блока элементов И соединен с первым входом первого ключа, второй вход которого подключен к выходу второго блока эл ментов И, входы которого соединены с разр}вдными выходами счетчика, упавляющий вход счетчика объединен со вторым управляющи входом сумматора и подключен к третьему выходу формирователя управляющих сигналов, четвертый выход которого соединен с первыми входами второго и третьего ключей, выход второго ключа подключен ко второму входу формирователя управляющих сигналов, выход третьего ключа соединен с первым управляющим входом первого регистра, введены второй ре гистр и цифровой нуль-орган, при этом первая группа информационных входов цифрового нуль-органа объединена с соответствующими информационными входами второго регистра и подключена к разрядным выходам счетчика, вторая группа информационных входов цифрового нуль-органа соединена с информационными выходами второго регистра, первый управляющий вход которого объединен с третьим входом фор-мирователя управляющих сигналов и подключен к выходу первого ключа, второй управляющий вход первого регистра объединен с четвертым входом формирователя управляющих сигналов и соединен с выходом цифрового нульоргана, управляющий вход которого подключен к пятому выходу формирователя управляющих сигналов, шестой выход которого соединен со вторым управляющим входом второго регистра, единичный и нулевой выходы младшего разряда которого подключены соответственно ко вторым входам второго и третьего ключей. Кроме того, формирователь управляющих сигналов содержит генератор тактовых импульсов, генератор периодических импульсов, два триггера, четыре ключа, четыре элемента ИЛИ, четыре элемента задержки, три элемента И, при этом выход первого элемента задержки подключен ко входам второго и третьего элементов задержки и к первому входу первого ключа, единичный выход первого триггера соединен с первым входом первого элемента И, второй вход которого объединен с первым входом второго элемента И, с первым входом второго ключа и подключен к нулевому выходу второго триггера, единичный выход которого роединен с первым входом третьего элемента И, второй вход которого объединен со вторым входом второго.элемента И и подключен к нулевому выходу первого триггера, выход второго элемента И соединен со вторым входом первого ключа, выход которого является вторым выходом формирователя, вход первого элемента задержки является первым входом формирователя, выход первого элемента ИЛИ соединен с единичным входом первого триггера, нулевой вход которого подключен к выходу второго элемента ИЛИ, первый вход которого объединен с первым входом третьего элемента ИЛИ и является вт рым входом и третьим выходом формир вателя, выход второго элемента заде ки соединен со вторым входом второг ключа, выход которого подключен к первому входу четвертого элемента ИЛ выход которого является первым выхо 1дом формирователя, второй вход четвертого элемента ИЛИ объединен с пе вым входом первого элементаИЛИ, с единичным входом второго триггера и соединен с выходом генератора такто вых импульсов, второй вход второго элемента ИЛИ является третьим входо формирователя, второй вход первого элемента ИЛИ объединен со йторым входом третьего элемента ИЛИ и явля ется четвертым входом формирователя выход третьего элемен.а задержки под ключен к первому входу третьего клю ча, второй вход которого соединен с выходом первого элемента И, выход третьего элемента И подключен к пер вому входу четвертого ключа, второй вход которого соединен с выходом ге нератора периодических импульсов, выход четвертого ключа подключен ко входу четвертого элемента задержки и является четвертым выходом формирователя, выход третьего ключа явля ется пятым выходом формирователя, выход четвертого элемента задержки является шестым выходом формирователя. На фиг.1 приведена блок-схема вычислителя J на фиг.2 - пример построения генератора импульсов. Вычислитель содержит источник чисел выборки 1, сумматор 2, первый регистр 3, формирователь управляющих сигналов 4, счетчик 5, первый и второй блоки элементов И 6 и 7, второй регистр 8, цифровой нуль-орган 9, первый, второй и третий ключи 10, 1 и 12 соответственно. Формирователь управляющих сигналов содержит генератор тактовых импульсов (кнопка пуска) 13, триггеры 14 и 15, ключи 16-19, генератор периодических импульсов 20, элементы И 21, 22 и 23, элементы ИЛИ 24-27, эле менты задержки 28-31. Работа формирователя достаточно очевидна из блок-схемы и описания его функций, следует указать лишь состояния Т и Т триггеров 14 и 15 в различных режимах соответственно работы: Исходное ,. , состояние Т.1, , Режим А , , Режим н , . Режим Д Источник чисел выборКи 1 после каждого импульса, подаваемого на его запускающий (управляющий) вход, соединенный с первым выходом формирователя 4, формирует на своих разрядных потенциальных выходах число х выборки ( i 1 , 2) в двоичном коде. После окончания формирования числа возникает импульс на управляющем выходе источника, соединенном с первым входом формирователя 4. В качестве источника чисел выборки может служить, например, цифровой измерительный прибор, преобразователь аналог - код и т.п., I Сумматор 2 - это обычный двоичный сумматор с потенциальными входами и выходами. После импульса, поступающего на его первый управляющий вход, соединенный с управляющим выходом источника чисел выборки 1, сумматор прибавляет к своему содержимому число, присутствующее в это время на выходах источника 1. Он вычисляет величину . Регистр 3 является сдвиговым регистром. Импульс, поступающий на его первый управляющий вход с выхода цифрового нуль-органа 9, помещает в регистр 3 число SM , находящееся в это время в сумматоре 2. Импульс, поступающий на первый управляющий вход с выхода третьего ключа 12, сдвигает содержимое регистра на два разряда в сторону младших разрядов (в этом его отличие от регистра 3 прототипа). Регистр 3 служит для приема величины 31и и деления ее на число путем k сдвигов на два разряда кгиждый в сторону младших разрядов. Выход регистра 3 является выходом вычислителя. Формирователь управляющих сигналов 4 выполнен многорежимным, управляемым. В исходном состоянии импульсы на его выходах отсутствуют, после пуска возникает один импульс на первом выходе и генератор переходит в режим Д (адаптации) - определения необходимой величины п. В этом режиме, получая импульс на первый вход, формирователь формирует импульс на втором выходе и затем, спустя некоторое время, очередной импульс на первом выходе (если он раньше не переведен в другой режим, в котором этот импульс уже не формируется) . Получив импульс на третий вход свидетельствующий об окончании работы в режиме А , т.е. о том, что величина -frT определена, формирователь переходит в режим Н (накопления), отличающийся от предыдущего тем, что вместо импульсов на втором выходе начинают появляться (с некоторой задержкой) импульсы на пятом выходе. После получения импульса на четвертом входе, свидетельствующего об окончании работы в режиме Н г т.е. о

том, что величина 2, определена, формирователь переходит в режим Д (деление) . В этом режиме импульсы фиксированной частоты генерируются только на четвертом и шестом выходах.

импульс на второй вход,. свидетельствуюгдий об окончании работ в режиме Д (т.е. о том, что оценка вычислена), формирователь формирует импульс на третьем выходе и возвращается в исходное состояние.

Устройство р.аботает следующим об|разом.

В исходном состоянии сумматор 2, регистры 3 и 8 и счетчик 5 установлены в нуль, импульсы на выходах формирователя 4 отсутствуют. Число Х выбранное из соображений требуемой точности, установлено на блоке элементов И 7 (например, если относительная погрешность определяется согласно формуле (1), то выбирают

z -Vc/ад,

т.е. число должно быть таким, чтобы при максимальном значении вели чины а величина ( ) была равн минимальному значению п, обеспечивающему заданную относительную точность) ;

После запуска формирователя 4 он генерирует импульс на первом выходе, в результате на счетчике 5 фиксируется единица, источник чисел выборки 1 формирует число х, передает его в сумматор 2 и сообщает о- завершении этих действий формирователю 4 импульсом, подаваемым на его первый вход. Получив импульс на первый вкод формирователь 4 в дальнейшем формирует по одному импульсу на первом и втором выходах, и этот цикл повторяется до тех пор, пока увеличивающееся с ростом i число Vi , фиксируемое сумматором 2, не начнет удовлетворять условию 51vi7/5. После этого блок элементов И 7 начнет пропускать на -первый вход первого ключа 10 импульсы со второго выхода формирователя 4

Как только число, фиксируемое счетчиком 5, примет вид , ключ 10 откроется и теперь очередной импульс со второго выхода формировател 4, пройдя через блок 7 и ключ 10, поступит на первый управляющий вход второго регистра 8 и на третий вход формирователя 4. Регистр 8 зафиксирует число m , содержащееся при этом в счетчике 5, формирователь 4 перейдет в режим Н.

Если , то первый же импульс с пятого выхода формирователя 4 прохолит через цифровой нуль-орган 9 и поступает, во-первых, на второй управляющий вход регистра 3, передавая в него содержимое 2 сумматора 2, и, во-вторых, на четвертый вход формирователя 4, который переходит в режим Д, формируя импульс на четвертом выходе, а затем - на шестом выходе. Поскольку в рассматриваемом случае т 2, ключ 11 открыт, а ключ 12 закрыт, и импульс с четвертого выхода формирователя 4 поступает на второй, вход генератора 4. Получив этот импульс, генератор 4 формирует импульс на третьем выходе и возвращается в исходное состояние. В этом случае а х и, следовательно, оценка (3) вычислена. Импульс с третьего выхода формирователя 4 установит в нуль сум1матор 2 и счетчик 5.

Цифровой нуль-орган 9 пропускает на выход импульс, поступающий на его управляющий вход с пятого выхода формирователя 4 только в том случае если кодовые комбинации, поступающие на первую и вторую группы его информационных входов, соединенных соответственно с выходами счетчика 5 и с выходами регистра 8, совпадают. Существенно, что вторая группа входов соединена особым способом: выход i-r разряда регистра 8 соединен со входо 2i-ro разряда нуль-органа 9 (,1, 2,...), на входы остальных его разрядов подан нулевой сигнал. В результате такого соединения совпадение кодовых комбинаций на обеих группах входов нуль-органа 9 {представляющего собой, по сути, блок элементов совпадения) означает, что число, содержащееся в счетчике 5, равно квадрату числа, содержащегося в регистре 8.

Если величина m, при которой появляется импульс на выходе ключа 10, больше 1, т.е. т 2, k7 О, работа в режиме Н продолжается до тех пор, пока не совпадут кодовые комбинации на обеих группах входов цифрового нуль-органа 9, т.е. пока не выполнено условие (2/a) , т.е. условие (4) с запасом, обусловленным

округлением m до числа вида 2 . t

При выполнении этого условия импульс с выхода нуль-органа 9 передает величину Ху, в регистр 3 и переводит, формирователь 4 в режим Д. В этом режиме каждый импульс с четвертого выхода сдвигает содержимое регистра 3 на два разряда, а каждый импульс с шестого выхода - содержимое регистра 8 на один разряд в сторону младших разрядов (поскольку то ключ 11 закрыт, а ключ 12 открыт) После того, как с шестого выхода формирователя 4 поступит К-1 импульс в регистре 8 окажется зафиксированно единица в младшем разряде, т.е. ключ 11 откроется, а ключ 12 закроется, и очередной импульс с четвертого выхода формирователя 4 поступит на его второй вход, свидетельствуя об

окончании вычисления оценки (3). В регистре 3 зафиксируется число Zwifvi/ где n () , что и требуется согласно (4),

Относительная погрешность вычислителя существенно меньше зависит от оцениваемого значения, чем у известных устройств, оставаясь практически постоянной во всем его диапазоне, что позволяет повысить качество управления в стохастических системах широкого класса и получить благодаря этому положительный экономический эффект.

Формула изобретения

подключен к выходу первого ключа, второй управляющий вход первого регистра объединен с четвертым входом формирователя управляющих сигналов и соединен с выходом цифрового нульоргана, управляющий вход которого подключен к пятому выходу формирователя управляющих сигналов, шестой выход которого соединен со вторым управляющим входом второго регистра,

0 единичный и нулевой выходы младшего разряда которого подключены соответственно ко вторым входам.второго и

третьего ключей. I

5 ключа, единичный выход первого триггера соединен с первым входом первого элемента И, второй вход которого объединен с первым входом вторюго элемента И, с первым входом второго

0 ключа и подключен к нулево1игу выходу второго триггера, единичный выход которого соединен с первым входом третьего элемента И, второй вход которого объединен со вторым входом

5 второго элемента И и подключен к ну левому Выходу первого триггера, выход второго элемента И соединен со вторым входом первого ключа, выход которого является вторым выходом формирователя, вход первого элемента

0 задержки является первым входом формирователя, выход первого элеменгта ИЛИ соединен с единичным входом первого триггера, нулевой вход которого подключен к выходу второго эле5мента ИЛИ, первый вход которого объединен с первым входом третьего элемента ИЛИ и является вторым входом и третьим выходом формирователя, выход второго элемента задержки соединен

0 со вторым входом второго ключа, выход которого подключен к первому входу четвертого элемента ИЛИ, выход которого является первым выходом формирователя , второй вход четвертого эле5мента ИЛИ объединен с первым входом первого элемента ИЛИ, с единичным входом второго триггера и соединен с выходом генератора тактовых импульсов, второй вход второго элемента ИЛИ яв0ляется третьим входом формирователя, второй вход первого элемента ИЛИ объединен со вторым входом третьего элемента ИЛИ и является четвертым входом формирователя, выход третьего

5 элемента задержки подключен к гервому

входу третьего ключа, второй вход которого соединен с выходом первого элемента И, выход третьего элемента И подключен к первому входу четвертого ключа, второй вход которого соединен с-выходом генератора периодических импульсов, выход четвертого ключа подключен ко входу четвертого элемента задержки и является четвертым выходом формирователя, выход третьего ключа является пятым выходом

формирователя, выход четвертого элемента задержки является шестым выходом формирователя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-12-15—Публикация

1981-06-15—Подача