(5) ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ СЛУЧАЙНОГО ПРОЦЕССА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения среднего | 1978 |

|

SU748419A1 |

| Рекуррентный вычислитель оценки математического ожидания | 1978 |

|

SU746548A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Времяимпульсный компаратор | 1986 |

|

SU1403361A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2128853C1 |

| Адаптивный вычислитель оценки математического ожидания | 1981 |

|

SU982014A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

I

; Изобретение относится к вычислительной технике и может быть испрль зовано для текущего статистического анализа случайных процессов.

Известно устройство для вычисления математического ожидания, состоящее из аналого-цифрового преобразователя, генератора импульсов, двух временных селекторов, счетчика импульсов, триггера и делителя частоты D.

Наиболее близким к предлагаемому по техническому решению является вычислитель оценки математического ожидания случайного процесса, содержащий времяимпульсный преобразователь, управляющий вход которого подключен к первому выходу блока управления, информационный вход времяимпульсного преобразователя является входом устройства, выход времяимпульсного преобразователя подключен ко входу установки в нуль триггера , нулевой выход которого соединен с управляющим входом первого ключа , информационный вход которого объединен с информационным входом второго ключа и подключен к выходу генератора импульсов, выход первого ключа соединен со входом установки в единицу триггера и с первым входом блока управления, .второй выход которого подключен к управляющему входу второго ключа, выход которого непос10редственно и через элемент задержки соединен соответственно с управляющим входом первого блока сравнения и со счетным входом счетчика, вход установки в нуль которого подключен

15 к третьему выходу блока управления, выходы счетчика соединены с первой . группой информационных входов блока сравнения, вторая группа информационных входов которого подключены к

20 выходам первого регистра, управляющий вход которого соединен с четвертым выходом блока управления, пятый и шестой выходы ксэторого подключены соответственно к управляющим входам сложение и вычитание реверсивного счетчика, сметный вход которого соединен с выходом элемента задержки, седьмой выход блока управления подключен ко входу установkи в нуль первого регистра 2.

Известное устройство имеет низкое быстродействие

Цель изобретения - повышение быстродействия вычислителя..

Поставленная цель достигается тем, что вычислитель оценки математическрго ожидания случайного процесса содержит второй и третий регистры и второй блок сравнения, при этом выходы сметчика подключены к первой г Ьуппе информационных входов второго блока сравнения, выход которого соединен с третьим входом блока управления, восьмой выход которого подключен к управляющему входу . второго регистра, информационные выходы которого соединены со второй группой информационных входов второго блока сравнения, управляющий вход которого подключен к выходу второго ключа, девятый выход блока управления соединен со входом установки в нуль второго регистра, информационны входы которого подключены к информационным выходам третьего регистра, информационные входы которого соединены свыходами счетчика, управляющий вход третьего регистра подключен к десятому выходу блока управления одиннадцатый выход которого соединен со входом установки в нуль третьего регистра. Кроме того, блок управления содер жит генератор импульсов, четыре триггера, счетчик импульсов, восемь ключей, четыре элемента ИЛИ, два элемента И и шесть элементов задержки, при этом выход генератора импуль сов подключен к первому входу первог элемента ИЛИ, выход которого соединен со входом установки в единицу первого триггера и является первым выходом блока, вход установки в нуль первого триггера подключен к выходу второго элемента ИЛИ, первый вход которого соединен с выходом первого ключа, первый вход которого объединен с первым входом второго ключа и является первым входом блока, выход второго ключа соединен с первым входом третьего ключа, выход которого подключен ко входу установки в единицу второго триггера, единичный выход которого соединен с первым входом четвертого ключа и является шестым выходом блока, выход первого элемента И соединен с первым входом пятого ключа, второй вход которого подключен к выходу шестого ключа, первый вход которого объединен с выходом первого элемента задержки и соединен с выходом второго элемента ИЛИ, первые входы седьмого и восьмого ключей объединены и подключены к выходу второго элемента И, первый и второй входы которого подключены соответственно к первому и второму выходам счетчика импульсов, третий выход которого соединен с первым входом первого элемента И, второй вход которого объединен с первыми входами девятого ключа и третьего элемента ИЛИ и подключен к четвертому выходу счетчика имп;ульсов, пятый выход которого .соединен со вторым входом третьего ключа, входы установки в нуль третьего и четвертого триггеров объединены и подключены к выходу первого элемента ИЛИ, ед1 нимный выход третьего триггера соединен со вторыми входами третьего элемента ИЛИ и шестого ключа, выход которого соединен со входом второго элемента задержки и является четвертым выходом блока, первый вход четвертого элемента ИЛИ объединен со вторым входом второго -элемента ИЛИ, со входом установки в нуль второго триггера и подключен к выходу четвертого ключа, второй вход которого объединен со входом установки в единицу четвертого триггера и является третьим входом блока, выход пя.того элемента ИЛИ соединен со входом третьего элемента задержки и является десятым выходом блока, первый вход пятого элемента ИЛИ объединен со входом четвертого элемента задержки, со вторым входом восьмого ключа и соединен с выходом второго ключа, второй вход которого подключен к нулевому выходу четвертого триггера, единичный выход которого соединен со вторым входом первого ключа, выход четвертого элемента задержки подключен ко второму входу седьмого ключа, выход которого соединен со вторым входом четвертого элемента ИЛИ, третий вход которого соединен с выходом пятого элемента задержки, вход которого объединен со вторым вхЬдом

пятого элемента ИЛИ и подключен к выходу пятого ключа, выход четвертого элемента ИЛИ подключен ко входу шестого элемента задержки и является восьмым выходом блока, счетный вход счетчика импульсов соединен с выходом девятого ключа, второй вход которого объединен со вторым входом первого элемента ИЛИ и подключен к выходу седьмого элемента задержки, вход которого объединен с выходом первого элемента задержки и является третьим выходом блока, вход установки в единицу третьего триггера является вторым входом блока, выход первого триггера является вторым выходом блока, выходы второго, третьего и шестого элементов задержки являются соответственно вторым, седьмым, одиннадцатым и девятым выходами блока, выход восьмого ключа соединен с третьим входом второго элемента ИЛИ

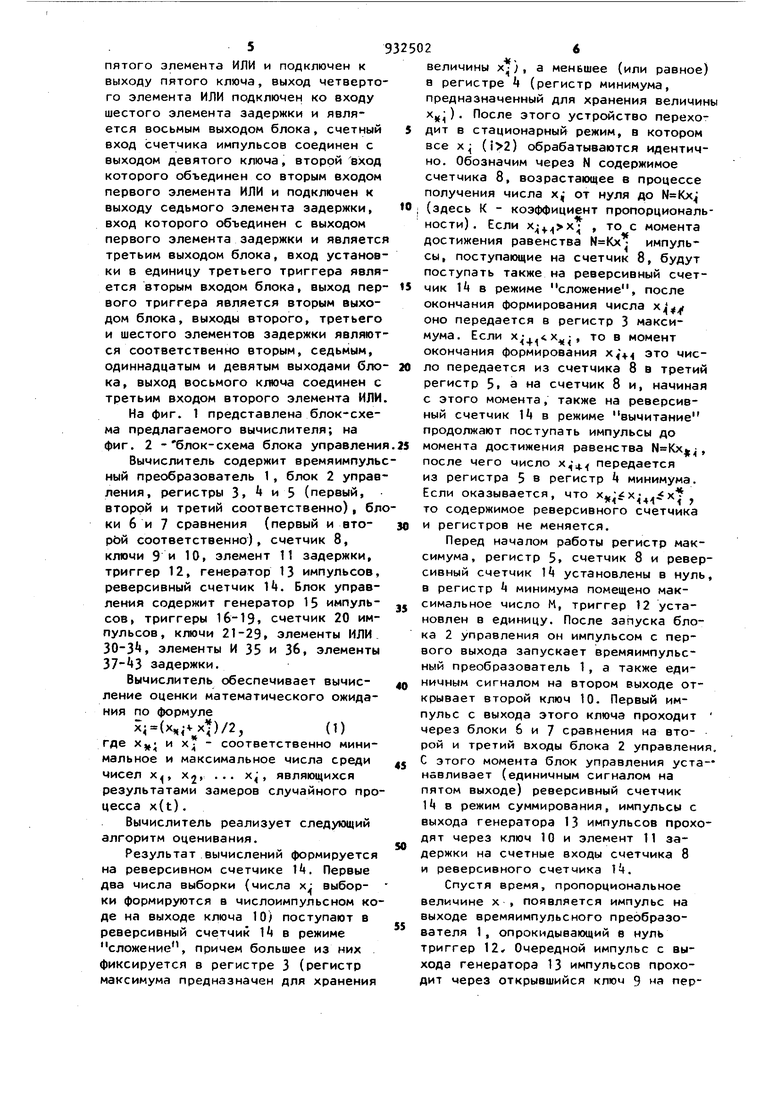

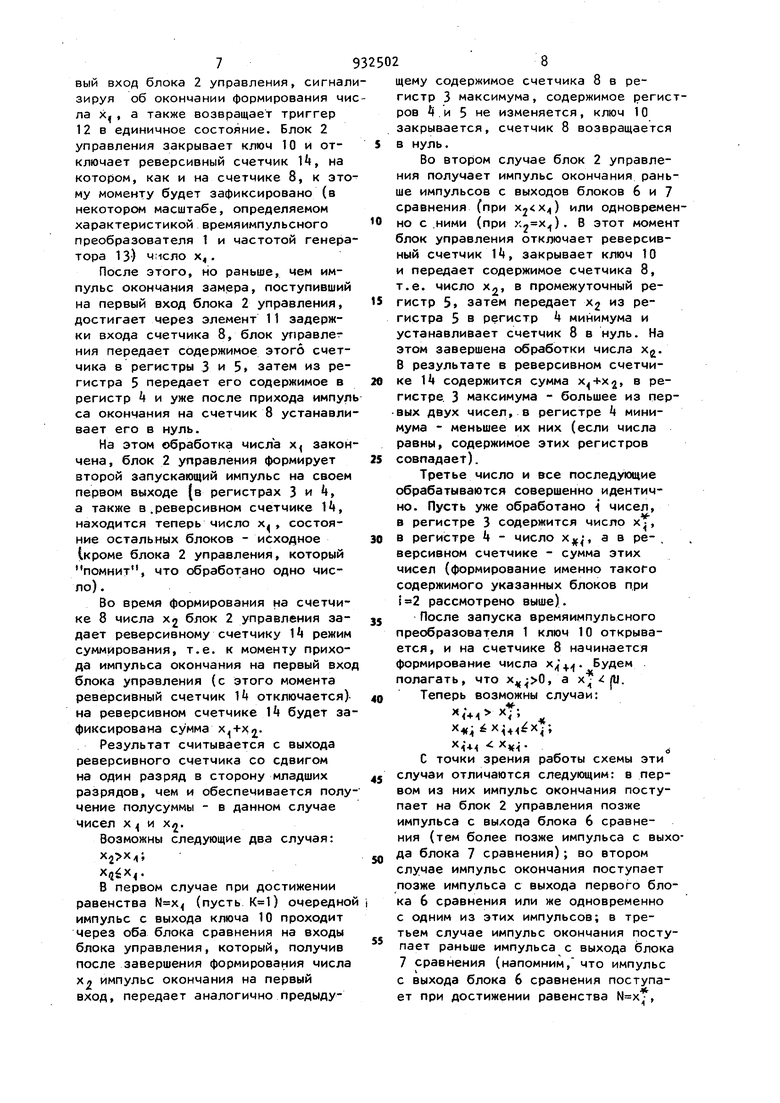

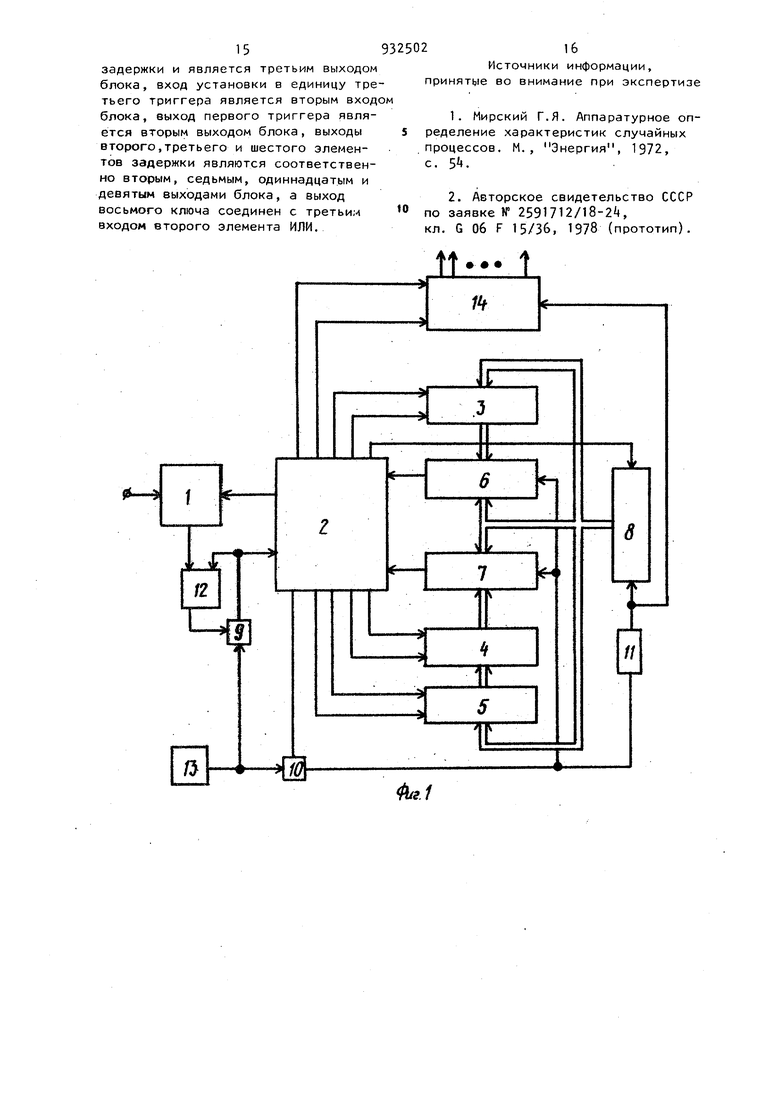

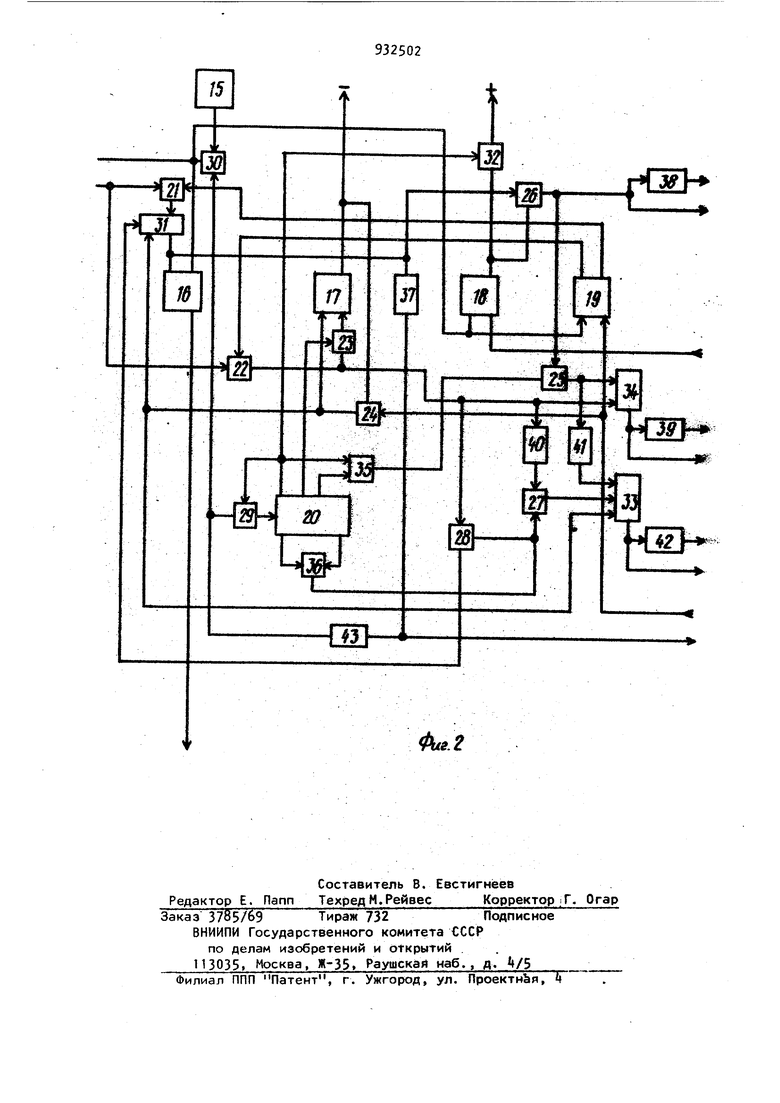

На фиг. 1 представлена блок-схема предлагаемого вычислителя; на фиг. 2 -блок-схема блока управления

Вычислитель содержит времяимпульсный преобразователь 1, блок 2 управления, регистры 3, и 5 (первый, второй и третий соответственно), блоки 6 и 7 сравнения (первый и аторьй соответственно), счетчик 8, ключи 9 и 10, элемент 11 задержки, триггер 12, генератор 13 импульсов, реверсивный счетчик 1. Блок управления содержит генератор 15 импульсов, триггеры 16-19. счетчик 20 импульсов, ключи 21-29, элементы ИЛИ. 30-3, элементы И 35 и 36, элементы задержки.

Вычислитель обеспечивает вычисление оценки математического ожидания по формуле

х(х,,-л.х|)/2, (1) где и X - соответственно минимальное и максимальное числа среди чисел х, Х2, ... X,, являющихся результатами замеров случайного процесса x(t).

Вычислитель реализует следующий алгоритм оценивания.

Результат вычислений формируется на реверсивном счетчике It. Первые два числа выборки (числа х- выборки формируются в числоимпульсном коде на выходе ключа 10) поступают в реверсивный счетчик в режиме сложение, причем большее из них фиксируется в регистре 3 (регистр максимума предназначен для хранения

величины х), а меньшее (или равное) в регистре k (регистр минимума, предназначенный для хранения величины х). После этого устройство переходит в стационарный режим, в котором все х () обрабатываются идентично. Обозначим через N содержимое счетчика 8, возрастающее в процессе получения числа х, от нуля до (здесь К - коэффициент пропорциональности) . Если .х , то с момента достижения равенства импульсы, поступающие на счетчик 8, будут поступать также на реверсивный счетчик Ц в режиме сложение, после окончания формирования числа оно передается в регистр 3 максимума. Если ,.х,, то в момент окончания формирования это число передается из счетчика 8 в третий регистр 5i а на счетчик 8 и, начиная с этого момента, также на реверсивный счетчик l в режиме вычитание продолжают поступать импульсы до момента достижения равенства , после чего число .| передается из регистра 5 в регистр Ц минимума. Если оказывается, что у то содержимое реверсивного счетчика и регистров не меняется.

Перед началом работы регистр максимума, регистр 5 счетчик 8 и реверсивный счетчик 1 установлены в нуль, в регистр А минимума помещено максимальное число М, триггер 12 установлен в единицу. После запуска блока 2 управления он импульсом с первого выхода запускает времяимпульсный преобразователь 1, а также единичным сигналом на втором выходе открывает второй ключ 10. Первый импульс с выхода этого ключа проходит через блоки 6 и 7 сравнения на второй и третий входы блока 2 управления. С этого момента блок управления устанавливает (единичным сигналом на пятом выходе) реверсивный счетчик в режим суммирования, импульсы с выхода генератора 13 импульсов проходят через ключ 10 и элемент 11 задержки на счетные входы счетчика 8 и реверсивного счетчика .

Спустя время, пропорциональное величине х , появляется импульс на выходе времяимпульсного преобразователя 1, опрокидывающий в нуль триггер 12 Очередной импульс с выхода генератора 13 импульсов проходит через открывшийся ключ 9 я первый вход блока 2 управления, сигнал зируя об окончании формирования чи ла X,, а также возвращает триггер 12 в единичное состояние. Блок 2 управления закрывает ключ 10 и отключает реверсивный сметчик }k, на КОТ000М, как и на счетчике 8, к это му моменту будет зафиксировано (в некотором масштабе, определяемом характеристикой времяимпульсного преобразователя 1 и частотой генера тора 13) число X,, После этого, но раньше, чем импульс окончания замера, поступивший на первый вход блока 2 управления, достигает через элемент 11 задержки входа счетчика 8, блок управлег ния передает содержимое этого счетчика в регистры 3 и 5 затем из регистра 5 передает его содержимое в регистр k и уже после прихода импул са окончания на счетчик 8 устанавли вает его в нуль. На этом обработка числа х закон чена , блок 2 управления формирует второй запускающий импульс на своем первом выходе (в регистрах 3 и 4, а также в .реверсивном счетчике 1А, находится теперь число х, состояние остальных блоков - исходное 1кроме блока 2 управления, который помнит, что обработано одно число) . Во время формирования на счетчике 8 числа Х2 блок 2 управления задает реверсивному счетчику 1k режим суммирования, т.е. к моменту прихода импульса окончания на первый вхо блока управления (с этого момента реверсивный счетчик Н отключается) на реверсивном счетчике I будет за фиксирована сумма . Результат считывается с выхода реверсивного счетчика со сдвигом на один разряд в сторону младших разрядов, чем и обеспечивается полу чение полусуммы - в данном случае чисел X и X Возможны следующие два случая: . В первом случае при достижении равенства (пусть ) очередно импульс с выхода ключа 10 проходит через оба блока сравнения на входы блока управления, который, получив после завершения формирования числа Х2 импульс окончания на первый вход, передает аналогично предыдущему содержимое счетчика 8 в регистр 3 максимума, содержимое регистров и 5 не изменяется, ключ 10 закрывается, счетчик 8 возвращается в нуль. Во втором случае блок 2 управления получает импульс окончания раньше импульсов с выходов блоков 6 и 7 Xjix) или одновременсравнения). В этот момент но с .ними блок управления отключает реверсивный счетчик l, закрывает ключ 10 и передает содержимое счетчика 8, т.е. число Х2, в промежуточный регистр 5 затем передает Xj из регистра 5 в регистр k минимума и устанавливает счетчик 8 в нуль. На этом завершена обработки числа Xg. В результате в реверсивном счетчике Il содержится сумма , в регистре. 3 максимума - большее из первых двух чисел, в регистре k минимума - меньшее их них (если числа равны, содержимое этих регистров совпадает). Третье число и все последующие обрабатываются совершенно идентично. Пусть уже обработано чисел, в регистре 3 содержится число х в регистре 4 - число , а в реверсивном счетчике - сумма этих чисел (формирование именно такого содержимого указанных блоков п.ри рассмотрено выше). После запуска времяимпульсного преобразователя 1 ключ 10 открывается, и на счетчике 8 начинается формирование числа . Будем полагать, что , а . Теперь возможны случаи: ... i i v-i-о С точки зрения работы схемы эти случаи отличаются следующим: в первом из них импульс окончания поступает на блок 2 управления позже импульса с выхода блока 6 сравнения (тем более позже импульса с выхода блока 7 сравнения); во втором случае импульс окончания поступает позже импульса с выхода первого блока 6 сравнения или же одновременно с одним из этих импульсов; в третьем случае импульс окончания поступает раньше импульса с выхода блока 7 сравнения (напомним, что импульс с выхода блока 6 сравнения поступает при достижении равенства , а с выхода блока 7 сравнения - равенства ) . Работа схемы в указанных трех сл чаях протекает следующим образом. Во всех случаях с момента запуска времяимпульсного преобразователя 1 открывается ключ 10, а реверсивный счетчик остается отключенным, в счетчике 8, на счетный вход которого поступают через ключ 10 импуль сы с выхода генератора 13, начинает ся формирование числа х,ц. . Первый случай. Импуль с выхода блока 7 сравнения, поступа щий раньше импульса окончания, игно рирует блок 2 управления. Получив импульс с выхода блока 6 сравнения, блок управления переводит реверсивный счетчик в режим суммирования, затем, получив импульс окончания, блок управления закрывает ключ 10, передает содержимое счетчика 8, т.е число х:, в.регистр 3 максимума, после чего устанавливает счетчик 8 в нуль и снова запускает времяимпульсный преобразователь 1 для полу чения следующего числа выборки. Таким образом, в реверсивный счетчик tt прибавилось число импульсов пропорциональное разности т;е. в нем теперь находится сумма . , а в регистре максимума - число хо |Второй случай. Как и в предыдущем случае, импульс, пришедший с выхода блока 7 сравнения раньше импульса окончания (или одновременно с ним) игнорируется, а импульс окончания, пришедший раньше импульса с выхода блока 6 сравнения (или одновременно с ним), побуждает блок 2 управления закрыть ключ 10, возвратить счетчик 8 в нуль и снова запустить времяимпульсный преобразователь 1. Таким образом, в этом случае содержимое реверсивного счет чика 11 и регистров не изменяется. Третийслучай. Импуль окончания поступает при этом раньше импульса с выхода блока 7 сравнения получив ЭТОТ импульс, блок 2 управления передает содержимое счетчика 8 (т.е. число x.) в промежуточный регистр 5 и переводит реверсивный счетчик k в режим вычитания, ключ10 остается открытым, т.е. содвржимое счетчика 8 продолжает расти, и по достижении равенства №:XK| возникает импульс на выходе блока 7 сравнения. Получив этот импульс, блок 2 управления закрывает ключ 10, отключает реверсивный счетчик Т, передает содержимое промежуточного регистра 5 в регистр t минимума, после чего устанавливает в нуль счетчик 8 и снова запускает времяимпульсный преобразователь 1. Таким образом, из содержимого реверсивного счетчика 1 вычтено число импульсов, пропорциональное разности х(, , а в регистре t минимума находится теперь число Возможность вычисления оценки математического ожидания по формуле (1), реализуемая предлагаемым устройством, позволяет в тех случаях, когда данная оценка является предпочтительной, повысить эффективность функционирования управляющих и контрольно-измерительных систем. Рассмотрим работу блока управления при выполнении перечисленных выше операций. В исходном состоянии все триггеры Схемы, включая два триггера счетчика 20, установлены в нуль. Устройство запускается импульсом с выхода генератора 15 (с помощью кнопки или внешней команды). Первый пусковой импульс проходит через элемент 30 на управляющий вход преобразователя 1 и на единичный вход триггера 16, открывая тем самым ключ 10. Первый импульс с выхода этого ключа поступает - ввиду нулевого исходного состояния регистров 3 и - через блоки 6 и 7 на единичные входы триггеров 18 и 19 соответственно, ключи 21, 25 и 26 при этом открыты, ключи 22 и 2k закрыты, реверсивный счетчик I находится в режиме суммирования. Импульс окончания формирования х, поступающий на входы ключей 21 и 22, проходит только через ключ 21 и элемент ИЛИ 31 на нулеаой вход триггера 16, закрывая ключ 10, а также через ключи 25 и 26 - на входы регистров 3 и 5. передавая в них содержимое счетчика 8, т.е. число , а затем через элементы k и 33 на входы регистра . Кроме того, импульс с выхода элемента ИЛИ 31 с соответствующими задержками, поступает на сбросовый вход счетчика 8, на счетный вход счетчика 20 и, наконец, на второй вход элемента ИЛИ 30 задавая начало формирования очередного числа выборки х. Число х помегдено, таким образом, в реверсивный счетчик , а также в регистры 3 ,и 5. Если , то к моменту окончания формирования числа Х триггеры 18 и 19 находятся в единичном состоянии, ключ 25 закрыт, и импульс с выхода элемента 31 проходит только на входы регистра 3, передавая в него х со счетчика 8, после чего счетчик сбрасывается в нуль и формируется очередной импульс запуска преобразователя 1, как и в предыдущем случае. Если , то в момент прихода импульса окончания формирования Xg ключ 21 закрыт, зато открыт ключ 22 с выхода которого через открытый при обработке Xj ключ 28 и элемент ИЛИ 3 этот импульс поступает на нулевой вход триггера 16, закрывая ключ 10, а затем через элементы 3, 39, 0, 27, 33 и 42 - на входы регистров 5 и 4 (последовательно всг времени) ключ 27 открыт только при обработке Х2 ключ 23 nptd этом закрыт, так что реверсивный счетчик остается в режиме суммирования. Поскольку кл ключ 26 в этом случае заперт, содер жимое регистра 3 не изменяется, через элементы 37 и 3 импульс поступает на сбросовый вход счетчика 8 на счетный вход счетчика 20 (которы после этого блокируется ключом 29) и на вход элемента ИЛИ 30. Следовательно, в результате на реверсивном счетчике И будет Сформирована сумма , причем большее из этих чисел будет размещено в регистре 3 максимума, а меньшее - в регистре . k минимума и в промежуточном регист ре 5 (если , содержимое всех регистров будет, естественно, совпадать) . Каждое следующее число x(ij.3) обрабатывается одинаково; если , оно помещается в регистр 3, причем реверсивный счетчик I оказы вается в режиме суммирования с момента достижения равенства до момента окончания формирования числа X;;, если , то содер жимое регистров и реверсивного счет чика не меняется, если , то с момента прихода импульса окончания формирования Хц триггер 17 устанавливается в .единичное состояние, за давая реверсивному счетчику k ре; жим вычитания, число х помещается В промежуточный регистр 5 в момент достижения равенства импульс с выхода блока 7 проходит через открытый при этом ключ , опрокидывая триггеры 16 и 17, число х- из регистра 5 передается в регистр k минимума; аналогично предыдущему осуществляется сброс в нуль счетчика 8 и формирование очередного запускающего импульса, подаваемого на управляющий вход преобразователя 1. Формула изобретения 1. Вычислитель оценки математического ожидания случайного процесса, содержащий времяимпульсный преобразовател1., управляющий вход которого подключен к первому выходу блока управления, информационный вход времяимпульсного преобразователя является входом устройства, выход аремяимпульсного преобразователя подключен к входу установки в нуль триггера, нулевой выход которого соединен с управляющим входом первого ключа , информационный вход которого объединен с информационным входом второго ключа.и подключен к выходу генератора импульсов, выход первого ключа соединен с входом установки в единицу триггера и с первым входом блока управления, второй зыход которого подключен к управляющему входу второго ключа, выход которого непосредственно и через элемент задержки соединен соответственно с управляющим входом первого блока сравнения и со счетным входом счетчика, вход установки в нуль которого подключен к третьему выходу блока управления, выходы счетчика соединены с первой группой инфор мационных входов первого блока сравнения, вторая группа информационных входов которого подключена к выходам первого регистра, управляющий вход которого соединен с четвертым выходом блока управления., пятый и шестой выходы которого подключены соответственно к управляющим входам сложения и вычитания реверсивного счетчика, счетный вход, которого соединен с выходом элемента задержки, седьмой выход блока управления подключен к входу установки в нуль первого регистра, отличающийся тем, что, с целью повышения быстродействия, вычислитель содержит второй, и третий регист ры и второй блок сравнения, при этом выходы счетчика подключены к первой группе информационных входов Btoporo блока сравнения, выход которого соединен с третьим входом блока управления, восьмой выход которого подключен к управляющему входу второго регистра,информационный выходы которого соединены с второй группой информационных входов второго блока сравнения, управляющий вход которого подключен к выходу вто рого ключа, девятый выход блока управления соединен с входом установки в нуль второго регистра, информацион ные входы которого подключены к ин формационным выходам третьего регистра, информационные входы которог соединены с выходами счетчика, управ ляющий вход третьего регистра подключен к десятому выходу блока управления, одиннадцатый выход которог соединен с входом установки в нуль третьего регистра. 2. Вычислитель по п. 1, отли чающийся тем, что блок управ ления содержит генератор импульсов, четыре триггера, счетчик импульсов, восемь клю14ей, четыре элемента ИЛИ, два элемента И и шесть элементов задержки, при этом выход генератора им пульсов подключен к первому входу первого элемента ИЛИ, выход которого соединен с входом установки в единицу первого триггера и является первым выходом блока, вход установки в нуль первого триггера подклю чен к выходу второго элемента ИЛИ, первый вход которого соединен с выходом первого ключа, первый вход которого объединен с первым входом вто рого ключа и является первым входом блока, выход второго ключа соединен с первым входом третьего ключа, выход которого подключен к входу установки в единицу второго триггера, единичный выход которого соединен с первым входом четвертого ключа и является шестым выходом блока, выход первого элемента И соединен с первым входом пятого ключа, второй вход которого подключен к выхйду шестого ключа, первый вход которого объединен с выходом первого элемента задержки и соединен с выходом второго эпймента ИЛИ, первые входы седьмого и восьмого ключей объедииены и подключены к выходу второго элемента И, первый и второй входы которого подключены соответственно к первому и второму выходам счетчика импульсов, третий выход которого соединен с первым входом первого элемента И, второй вход которого объединен с первыми входами девятого ключа и третьего элемента ИЛИ и подключен к четвертому выходу счетчика импульсов, пятый выход которого соединен с вторым входом третьего ключа, входы установки в нуль третьего и четвертого триггеров объединены и подключены к выходу первого элемента ИЛИ, единичный выход третьего триггера соединен с вторыми входами третьего элемента ИЛИ и шестого ключа, выход которого соединен с входом второго элемента задержки и является четвертым выходом блока, первый вход четвертого элемента ИЛИ объединен с вторым входом второго элемента ИЛИ, с входом установки в нуль второго триггера и подключен к выходу четвертого ключа, второй вход которого объединен с входом установки в единицу четвертого триггера и является третьим входом блока, выход пятого элемента ИЛИ соединен с входом третьего элемента задержки и является десятым выходом блока, первый вход пятого элемента ИЛИ объединен с входом четвертого элемента задержки, с вторым входом восьмого ключа и соединен с выходом второго ключа, второй вход которого подключен к нулевому выходу четвертого триггера, единичный выход которого соединен с вторым входом первого ключа, выход четвертого элемента задержки подключен к второму входу седьмого кдюча, выход которого соединен с вторым входом четвертого элемента ИЛИ, третий вход которого соединен с выходом пятого элемента задержки, вход которого объединен с вторым входом пятого элемента ИЛИ и подключен к выходу пятого ключа, выход четвертого элемента ИЛИ подключен к входу шестого элемента задержки и является восьмым выходом блока, счетный вход счетчика импульсов соединен с выходом девятого кЛюча, второй вход которого объединен с вторым входом первого элемента ИЛИ и подключен к выходу седьмого элемента задержки, вход которого объединен с выходом первот г лемр|пл

задержки и является третьим выходом блока, вход установки в единицу третьего триггера является вторым входо блока, выход первого триггера является вторым выходом блока, выходы второго,третьего и шестого элементов задержки являются соответственно вторым, седьмым, одиннадцатым и девятым выходами блока, а выход восьмого ключа соединен с третьим входом второго элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

с. З.

кл, G Об F 15/36, 1978 (прототип).

fb-J

Авторы

Даты

1982-05-30—Публикация

1980-05-22—Подача