(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗНАНИЙ ОБУЧАЕМЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля знаний обучаемых | 1981 |

|

SU976469A1 |

| Обучающее устройство | 1982 |

|

SU1024963A2 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Тренажер радиотелеграфистов | 1989 |

|

SU1601622A1 |

| Обучающее устройство | 1980 |

|

SU875434A1 |

| Обучающее устройство | 1981 |

|

SU960901A1 |

| Обучающее устройство | 1981 |

|

SU964701A2 |

| Устройство для контроля знаний обучаемых | 1980 |

|

SU896660A1 |

Изобретение относится к aвтoмaти ке и вычислительной технике, в частности к техническим средствам обучения и контроля знаний, и может быть использовано для контроля знаний обучаемого, оценки сложности и качества пpeдпoлaгae aax тестов.

ИЗвестно устройство, содержащее пульты учащихся, блок оценки, коммутатор, счетчик правильных ответов и счетчик количества учащихся, блок определения веса вопросов 1.

Недостатком данного устройства является низкая точность оценки знаний учащихся.

Известно устройство, содержащее пульты обучаемых, каждый из которых содержит последовательно соединеннь блок .ввода|г логический блок, блок 2 индикации 2.

Недостатком этого устройства является невозможность определения сложности учебных заданий.

Наиболее близким к изобретению является устройство, содержащее пульты обучаемых, блок отсчета времени,блок подсчета общего числа ответов, блок подсчета неверных ответов и блок па-1 мяти 3 .

Устройство позволяет определять параметры учебных заданий, однако оО ладает значительной сложностью и ограниченными дидактическими возможностями, так как не позволяет присвоить объективный вес т.есту в системе контрольных заданий.

Цель изобретения - расширение дидактических возможностей устройства

10 за счет вычисления веса теста в системе контрольных заданий и определения сравнительного уровня обученности.

Поставленная цель достигается тем,

15 что в устройство,содержащее последовательно включенные пульт преподавателя, первый блок , пульты обучаемых, коммутатор пультов, первый счетчик и блок предъявления учебной ин20формации, второй вход которого соединен с выходом первого блока памяти, второй счетчик, первый вход которого соединен с вторым выходом коммутатора пультов, а второй вход - с первым

25 выходом формирователя импульсов, подключенным к второму входу первого счетчика, третьему входу блока предъявления учебной информации и второму входу первого блока па1мяти, четвертый вход

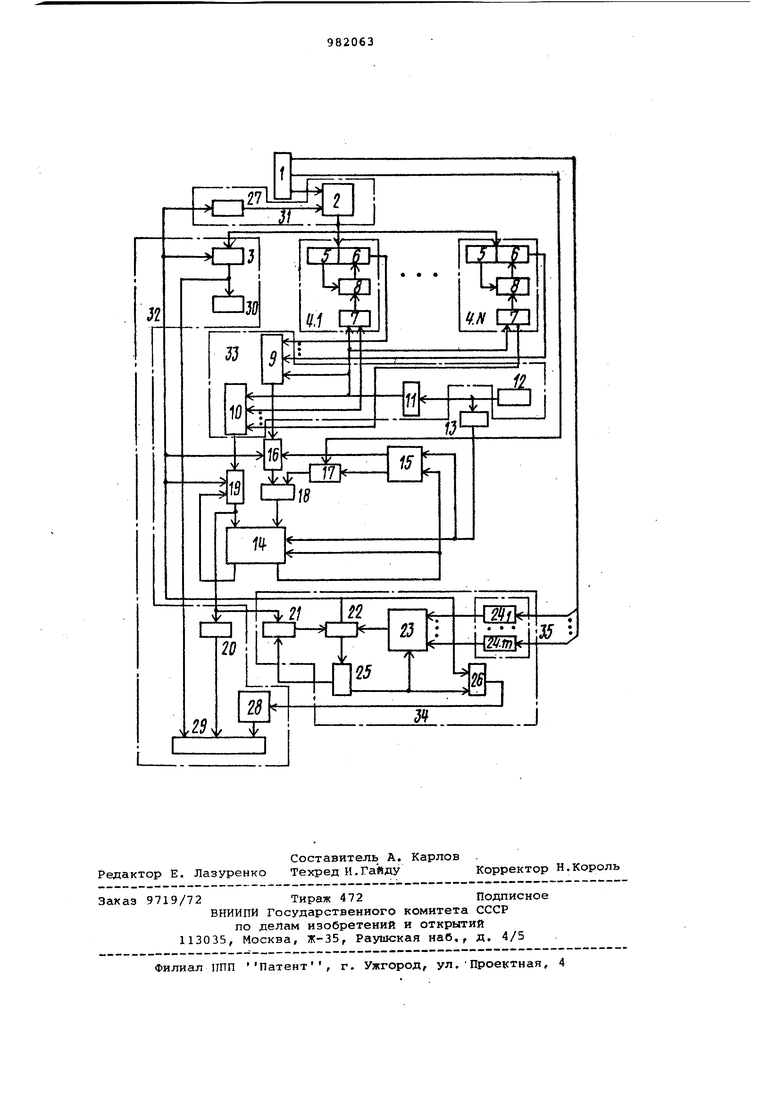

30 блока предъявления учебной йнформации соединен с вторым выходом; формирователя импульсов, первый вход которого подключен к второму выходу пульта преподавателя, третий счетчик вход которого соединен с третьим выходом коммутатора пультов, четвертый выход которого подключен к вторым 1входам пультов обучаег шх, введены последовательно соединенные триггер, регистр, элемент ИЛИ и блок умножения и деления кодов, второй и третий входы которого подключены соответственно к выходам первого и третьего счетчиков, первый выход - к третьему входу первого счетчика, а второй выход - к первому входу триггера, второй вход которого соединен с выходом третьего счетчика, а второй выход с третьим входом второго счетчика, выход которого подключен к второму входу элемента ИЛИ, второй вход формирователя импульсов соединен с выхо дом первого счетчика, второй вход регистра подключен к третьему выходу пульта преподавателя. Кроме того, коммутатор пультов со держит последовательно соединенные генератор, сдвигающий регистр и первый и второй блоки элементов И, выходы которых являются соответственно первым и вторым выходами коммутатора выход генератора является третьим вы ходом коммутатора, выход сдвигающего регистра является четвертым выходом коммутатора, входы блоков элементов И являются соответствующими входами коммутатора. При этом формирователь импульсов содержит четвертый счетчик и последо вательно включенные второй блок памя ти, блок коммутации, третий блок эле ментов И, пятый счетчик и элемент И, выход которого является вторым выходом формирователя, а второй вход сое дивен с вторым выходом третьего блока элементов И, являющимся первым вь1ходом формирователя, вход второго блока памяти является первым входом формирователя/ первый вход четвертого счетчика является вторым входом формирователя, второй вход соединен с вторым выходом пятого счетчика, а выход - с вторым входом третьего бло ка элементов И. На чертеже изображена структура устройства. Устройство содержит пульт 1 препо давателя, выход которого подключен к входу накопителя 2 (тестов). Выход накопителя 2 соединен с входом регистра 3 (информации) и с входами пультов 4 обучаемых, которые состоят из узла 5 памяти эталонов, триггера 6 (ответа обучаемого), узла 7 ввода ответов и узла 3 совпадения. Первый вход узла 8 подключен к выходу узла 5, а второй вход - к выходу узла 7, Выход узла 8 соединен с входом триггера б, а выходы триггеров б подключены к блоку 9 элементов И. Выход готовности узла 7 всех пультов 4 соединен с первым входом блока 10 элементов И. Выходы блокировки блоков 9 и 10 и узла 7 подключены к выХОДУ сдвигающего регистра 11, вход которого подключен к выходу генератора 12 (пакетов). Выход генератора 12соединен также с входом счетчика 13(времени), выход которого подключен к входу Начало операции блока 1 4 умножения и деления кодов и к единичному входу триггера 15. Прямой выход триггера 15 подключен к управляющему входу счетчика 16 (правильных ответов), а нулевой выход - к управляющему входу регистра 17 (максимального балла). Другой вход регист.ра 17 соединен с выходом пульта 1, а выход - с входом элемента ИЛИ 18. Другой вход элемента ИЛИ 18 подключен к выходу счетчика 16, счетный вход которого соединен с выходом блока 9. Выход элемента ИЛИ 18 соединен с входом первого операнда Ьлока 14. Вход второго операнда блока 14 подключен к выходу счетчика 19 (числа обучаемых) . Вьлход Конец операции блока 14 соединен с его управляющим входом Начало второй операции и с нулевым входом триггера 15. Другой выход блока 14 подключен к управляющему входу счетчика 19. Другой вход счетчика 19 соединен с блоком 10,а выход подключен также к входу регистра 20 (среднего балла группы по данному тесту) и к входу счетчика 21 (среднего балла). Выход счетчика 21 соединен с входом блока 22 элементов И, второй вход которого подключен к выходу блока 23 коммутации. Информационные входы блока 23 соединены с выходами m регистров 24 (правых границ зон), входы которых подключены к третьему входу пульта 1. Управляющий вход блока 23 соединен с выходом счетчика 25 (номера зоны). Этот же выход счетчика 25 подключен к элементу И 26, а его последовательный выход соединен с счетным входом счетчика 21. Счетный вход счетчика 2 подключен к выходу По несовпадению блока 22. Выход блока 22 По совпадению подключен к входу сброса счетчиков 16 и 19 регистра 3, к входу счетчика 27 (адреса теста) , выход которого соединен с накопителем 2 и с вторым входом элемента И 26. Выход элемента И 26 подключен к входу постоянного запоминающего узла 28, выход которого подключен к первому входу узла 29 вывода. Второй вход узла 29 соединен с выходом регистра 20, а третий - с выходом регистра 3. Этот же выход регистра 3 подключен к информационному .табло 30. В качества блока 14 может быть использован -микропроцессор, содержащий арифметико-логическое устройство, регистры общего назначения, микропрограммный автомат, устройство управления, шины ввода операндов и .управляющие шины. Микропроцессор вы- полняет арифметические и логические операции согласно программе, реаи1изуемой внешними сигналами управления. Счетчик 27 и накопитель 2 представляют собой блок 31 памяти, регистр 3, регистр 20, информационное табло 30, узел 28 и узел 29 - блок 32 предъявления учебной информации, генератор 12, счетчик 13, блоки 9 и 10 - комму татор 33 пультов, счетчик 21, блок 22, блок 23, регистры 24, счетчик 25 иэлемент 26 - формирователь 34 импульсов, регистры 24 объединены в блок 35 памяти.

Устройство работает следующим образом.

С пульта 1 в блок 31 заносится информация, включающая тесты и ответы на них. С блока 31 содержание теста, номер которого определяется с помощью счетчика 27, поступает на регистр 3, а оттуда поступает на узел 29 и табло 30, где предъявляется обучаемым. Эталон ответа с блока 31 поступает на пульты 4 и в узел 5. Обучаемый вводит ответ с пульта 4 в узел 7. Содержимое узла 5 и узла 7 сравнивается на узле 8, и результат сравнения поступает в триггер 6.

При правильном ответе сигнал из триггера 6 поступает на блок 9, а сигналы готовности с пультов 4 поступают на блок 10. С помощью генератора 12 и регистра 11 блокируется ввод информации с пультов 4, и сигналы, поступившие на блоки 9 и 10, разделяются во времени. Через блок 9 в счетчике 16 накапливается число правильных ответов (п), а через блок 10 в счетчике 19 - число обучаемых (N) по данному тесту. С генератора 12 через счетчик 13 в момент конца опроса на блок 14 поступает сигнал Начало операции определенный как операции деления. Этот же сигнал от счетчика 13 проходит через триггер 15 и разрешает прохождение содержимого счетчика 16 через элемент ИЛИ 18 на блок 14. Туда же поступает содержимое счетчика 19. Происходит операция деления (n/N), результат которой записывается в счетчик 19. Сигнал Конец операции , пройдя через триггер 15, разрешает прохождение содержимого регистра 17, которое туда поступает с пульта 1 и представляет собой максимальный балл. Это число через элемент ИЛИ 18 поступает на вход блока 14. Сигнал Конец операции в этом случае является одновременно и сигналом начала второй операции умножения. в микропроцессоре происходит

перемножение содержимого счетчика 19 и регистра 17t ) , где W - средний балл группы/ полученный по данноjMy тесту,

Результат перемножения с блока 14 переписывается в счетчик 19, а оттуда поступает в регистр 20 и счетчик 21. С пульта 1 в регистры 24 записывгоотся правые границы зон попадания W н,а интервале (О; В). Например, если

0 WCP- средний балл группы; Wn,- минимальный личный балл учащегося в группе; максимальный личный балл учащегося в группе k - коэффициент сложности вопроса, то границы зон и соот5ветствующие им весовые коэффициенты тестов k могут находиться из соответ- ствующих соотношений:

О W Wp,n- тест следует отбросить

0 как слишком сложный;

W

W

-тест повышенной сложП11Пности ();

W тест сложный (0,);

min -r

wniin „

-тест оптимальный, по ср- сложности (,5);

5

W w ,x- тест пониженной

сложности (,5);

W - тест легкий () ;

W

ma

- тест следует отбросить

0 как слишком легкий.

В блоке 22 сравнивается содержи- мое счетчика 21 и выбранного через блок 23 одного из m регистров 24 в порядке возрастания номера регистра. Номер i подключаемого регистра 24

5 определяется содержимым счетчика 25, При несовпадении добавляется 1 в счетчик 25, и содержимое следующего регистра сравнивается с тем же содержимым счетчика 21. По сигналу пере0полнения со счетчика 25 в счетчик 21 прибавляется приращение Д, и происходит сравнение нового числа с содержимым всех регистров 24, как описано. По сигналу совпадения блока 22 со

5 счетчика 25 через элемент И 26 на узел 28 поступает номер зоны, в которую попало W. Из узла 28 по номеру зоны выбирается соответствующий коэффициент k, который выводится на узел

0 29. Сюда же поступает содержимое регистров 20 и 3.

Таким образом, устройство для контроля знаний обучаемого позволяет вычислять вес теста в системе контроль5ных заданий, а также определять его качество. Устройство позволяет определять средний балл группы по данному тесту в зависимости от выбранной системы оценки. А зто, в свою очередь,

0 позволяет сравнивать уровень обученности различных групп по данному предмету.

Формула изобретения

5 обучаемых, содержащее последовательно включенные пульт преподавателя, первый блок памяти, пульты обучаемых, коммутатор пультов, первый счетчик и блок предъявления учебной информации, второй вход которого соединен с выходом первого блока памяти, второй первый вход которого сое динен с в-горым выходом коммутатора пультов, а второй вход - с первым выходом формирователя импульсов, подключенным к второму входу первого счетчика, третьему входу блока предъявления учебной информации и второму входу первого блока памяти, четвертый вход блока предъявления учебной информации соединен с вторым выходом формирователя импульсов, первый вход которого подключен к второму выходу пульта преподавателя, третий счетчий, вход которого соединен с третьим вы- ходом коммутатора пультов, четвертый выход которого подключен к вторым входам пультов обучаемых, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены последовательно соединенные триггер, регистр, элемент ИЛИ и блок умножения : и деления кодов, второй и третий входы которого подключены соответственно к выходам первого и третьего счетчиков, первый выход - к третьему входу первого счетчика, а второй выход к первому входу триггера, второй вход которого соединен с выходом третьего счетчика, а второй выход - с третьим входом второго счетчика, выход кото- рого подключен к второму входу элемента ИЛИ, второй вход формирователя импульсов соединен с выходом первого счетчика, второй вход регистра подключен к третьему выходу пульта преподавателя . 2,Устройство по п. 1, отличающееся тем, что в нем коммутатор пультов содержит последовательно соединенные генератор, сдвигающийся регистр и первый и второй блоки элементов И, выходы которых являются соответственно первым и вторым выходами коммутатора, выход генератора является третьим выходом коммутатора, выход сдвигающего регистра является .четвертым выходом коммутатора, входы блоков элементов И являются соответствующими входами коммутатора, : 3, Устройство по П, If ОТЛИч а ю щ е е с я тем, что в нем формирователь импульсов содержит четвертый счетчик и последовательно включенные второй блок памяти,блок коммутации, третий блок элементов И,пятыЯ счетчик и элемент И,выход которого является вторым выходом фррмирователя, а второй вход соединен с вторым выходом третьего блока элементов И,являющимся первым выходом формирователя, вход второго блока памяти является первым входом формирователя, первый вход четвертого счетчика является вторым входом формирователя,второй вход соединен с вторым выходом пятого счетчика, а выход - с вторым входом третьего блока элементов И. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № 562848, кл. G 09 В 7/07, 1978, 2 Авторское свидетельство СССР № 579653, кл, G 09 В 7/06, 1977. 3.Авторское свидетельство СССР 75823.3, кл. G 09 В 7/02, 1980 (про

Авторы

Даты

1982-12-15—Публикация

1981-06-03—Подача