(З) ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1980 |

|

SU957210A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство обработки данных процессора | 1988 |

|

SU1647584A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для программирования микросхем постоянной памяти | 1985 |

|

SU1285535A1 |

t

Изобретение относится к вычисли.тельной технике и может быть испольг зовано при разработке устройств микропрограммного управления.

Известно устройство микропрограммного управления, шолненное на программируемых логических матрицах

(плм) т.

Недостатком этого устройства является малая плотность занесения информации за счет невозможно :ти использования ячеек памяти при определенном кодировании между соседними выходными шинами. Это приводит к увеличению площади интегральной схемы устройства при заданном об-ьеме исходной HHfdpMauHwt

Наиболее близким техническим ре аюнием к изс ретению является усТ ройство, состоящее из нескольких ПЛМ, и соответствующих им сдвиговых регистров адреса. Управляющие и адресные входы регистров соединены соответственно с шиной синхронизации и

- адресной шиной, а разрядные выходы .регистров - с входами соответствующих блоков памяти 2.

Недостатками данного устройства.. ябляются большая площадь кристалла и соответственно стоимость интегральной схемы из-за наличия значительного числа неиспользуемых ячеек памяти, поскольку запись информации (в процессе технологического изготовления) каждого блока памяти выполнена независимо от остальных блоков.

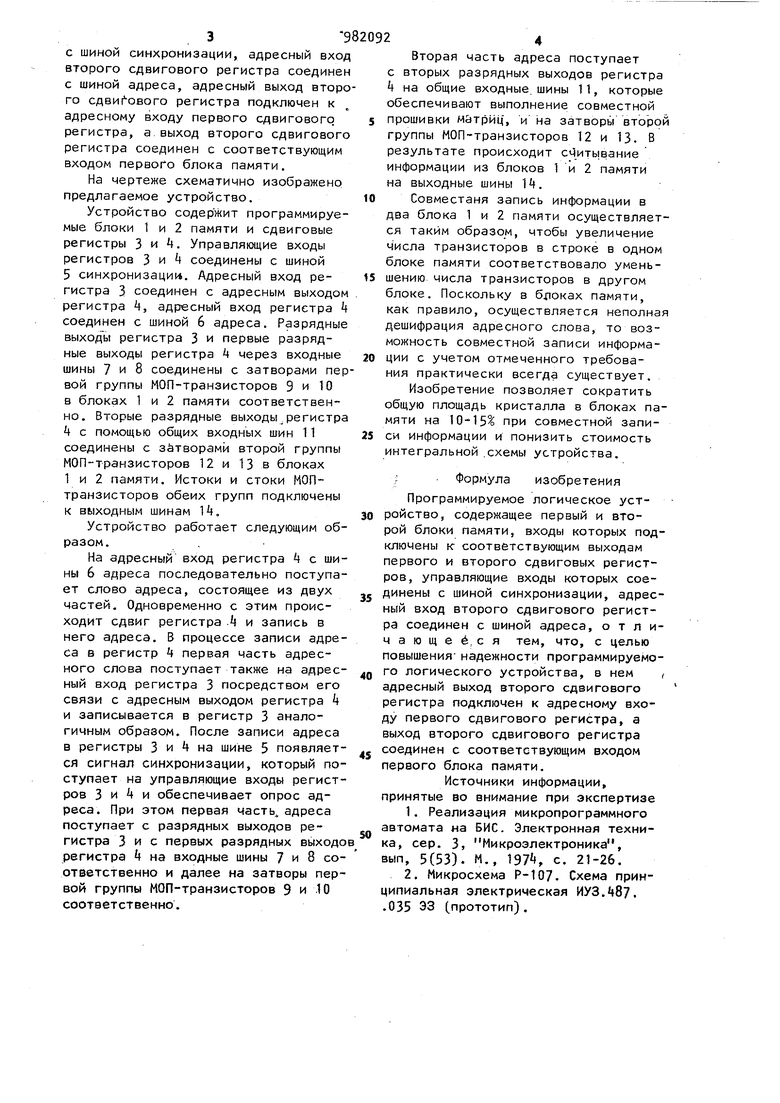

Цель изобретения - повышение надежности программируемого логического устройства за счет уменьшения площади кристалла и снижения стоимости интегральной схемы устройства. Поставленная цель достигается тем, что в программируемом логическом устройстве содержащем первый и второй блоки памяти, входы которых подключены к соответствующим выходам первого и второго сдвиговых регистров, |управляющие входы которых соединены . с шиной синхронизации, адресный вход второго сдвигового регистра соединен с шиной адреса, адресный выход второ го сдвиг ового регистра подключен к адресному входу первого сдвигового регистра, а выход второго сдвигового регистра соединен с соответствующим входом первого блока памяти. На чертеже схематично изображено предлагаемое устройство. Устройство содержит программируемые блоки 1 и 2 памяти и сдвиговые регистры 3 и 4. Управляющие входы регистров 3 и 4 соединены с шиной 5 синхронизации. Адресный вход регистра 3 соединен с адресным выходом регистра , адресный вход регистра k соединен с шиной 6 адреса. Разрядные выходЪ регистра 3 и первые разрядные выходы регистра 4 через входные шины 7 и 8 соединены с затворами пер вой группы МОП-транзисторов 9 и 10 в блоках 1 и 2 памяти соответственно. Вторые разрядные выходы регистра k с помощью общих входных шин 11 соединены с зётворамй второй группы МОП-транзисторов 12 и 13 в блоках 1 и 2 памяти. Истоки и стоки МОПтранзисторов обеих групп подключены к выходным шинам 1. Устройство работает следующим образом. На адресный вход регистра Ц с шины 6 адреса последовательно поступает слово адреса, состоящее из двух частей. Одновременно с этим происходит сдвиг регистра Ц и запись в него адреса. В процессе записи адреса в регистр Ч первая часть адресного слова поступает также на адресный вход регистра 3 посредством его связи с адресным выходом регистра k и записывается в регистр 3 аналогичным образом. После записи адреса в регистры 3 и it на шине 5 появляется сигнал синхронизации, который поступает на управляющие входы регистров 3 и и обеспечивает опрос адреса. При этом первая часть, адреса поступает с разрядных выходов регистра 3 и с первых разрядных выходо регистра на входные шины 7 и 8 соответственно и далее на затворы первой группы МОП-транзисторов Э и 10 соответственно. Вторая часть адреса поступает с вторых разрядных выходов регистра на общие входные, шины 11, которые обеспечивают выполнение совместной прошивки м&триЦ, и на затворы второй группы МОП-транзисторов 12 и 13. В результате происходит считывание информации из блоков 1 и 2 памяти на выходные шины Ц. Совместаня запись информации в два блока 1 и 2 памяти осуществляется таким образом, чтобы увеличение числа транзисторов в строке в одном блоке памяти соответствовало уменьшению числа транзисторов в другом блоке. Поскольку в блоках памяти, как правило, осуществляется неполная дешифрация адресного слова, то возможность совместной записи информации с учетом отмеченного требования практически всегда существует. Изобретение позволяет сократить общую площадь кристалла в блоках памяти на при совместной записи информации и понизить стоимость интегральной .схемы устройства. ; Формула изобретения Программируемое логическое устройство, содержащее первый и второй блоки памяти, входы которых подключены к соответствующим выходам первого и второго сдвиговых регистров, управляющие входы которых соединены с шиной синхронизации, адресный вход второго сдвигового регистра соединен с шиной адреса, о т л ичающеё,ся тем, что, с целью повышения надежности программируемого логического устройства, в нем ( адресный выход второго сдвигового регистра подключен к адресному входу первого сдвигового регистра, а выход второго сдвигового регистра соединен с соответствующим входом первого блока памяти. Источники информации, принятые во внимание при экспертизе 1.Реализация микропрограммного автомата на БИС. Электронная техника, сер. 3, Микроэлектроника, вып, 5(53). М., 197, с. 21-26, 2,Микросхема Р-107. Схема принципиальная электрическая ИУЗ.87. .035 ЭЗ (прототип),

L f t I ... I I 1. о 0 in е

Авторы

Даты

1982-12-15—Публикация

1980-12-25—Подача