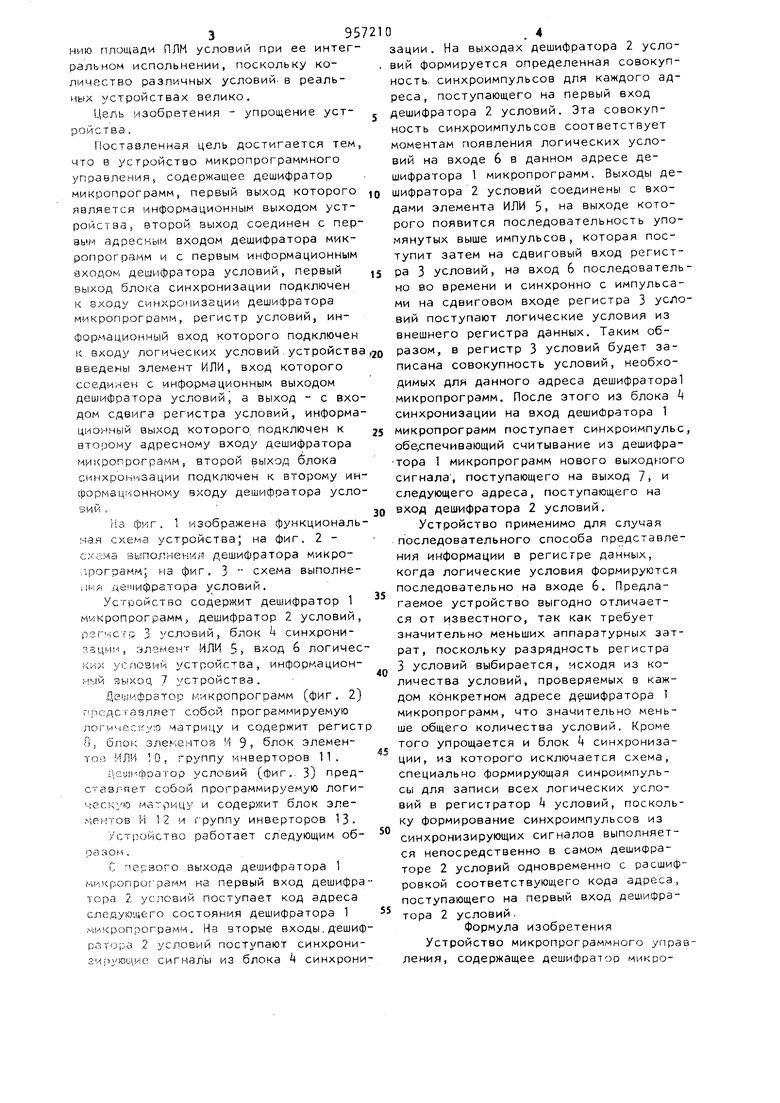

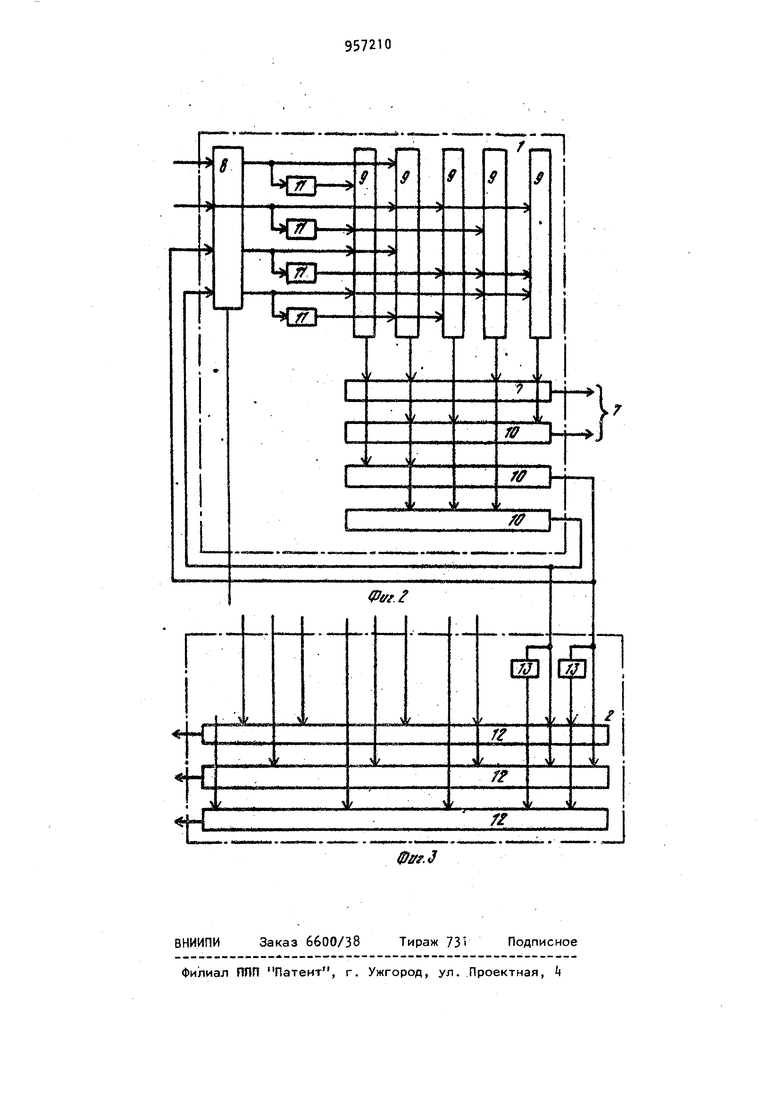

(5) УСТРОЙСТВО МИКРОПРОГРАММНОГО Изобретение относится к вычислительной технике и может найти применен/;е при построении вычислительных устройств с последовательным способом представления информации, в частности микрокалькуляторов. Изеестно устройство микропрограммного упрйвления, выполненное на про граммируемой логической матрице (ПЛМ содержащее ПЛМ микропрограмм, первые входы которой соединены с выходом ПЛМ микропрограмм, а вторые - с шина ми входных логических условий Cl 3Недостатком такого устройства микропрограммного управления являются большие размеры матрицы при большом количестве различных входных логичоских условий. Это приводит к усложнению устройства, особенно при ег интегральном исполнении. Известно устройство микропрограммного управления, содержащее ПЛМ мик ропрограмм, ПЛМ условий, регистр условий и блок синхронизации. Выход УПРАВЛЕНИЯ ПЛМ микропрограмм соединен с первым входом ПЛМ условий и входом ПЛМ микропрограмм, внешний информационный вход устройства соединен с информационным входом регистра условий, выход блока синхронизации соединен с входом регистра условий, выходы которого соединены с входами ПЛМ условий 2. Недостатком этого устройства является его сложность, так как содержащийся в нем регистр условий - многоразрядный, поскольку на нем должны быть запомнены все логические условия, которые могут воздействовать на входы ПЛМ микропрограмм. Кроме того, блок синхронизации должен содержать довольно сложную схему, вырабатывающую последовательность синхроимпульсов для занесения всех условий на регистр условий. А связь блока синхронизации через регистр условий с ПЛМ условий усложняет устройтсво, приводит к увеличе395нию плсацади ПЛМ условий при ее интегральном испольнении, поскольку количество различных условий, в реальных устройствах велико. Цель изобретения - упрощение устройства, Поставленная цель достигается тем что в устройство микропрограммного управления, содержащее дешифратор микропрограмм, первый выход которого является информационным выходом устройства, второй выход соединен с первым адресным входом дешифратора микропрограмм и с первым информационным входом дешифратора условий, первый выход блока синхронизации подключен к входу синхрояизации дешифратора микропрограмм, регистр условий, информационный вход которого подключен к входу логических условий , устройства введены элемент ИЛИ, вход которого соединен с информационным выходом дешифратора условийi а выход - с вхо дом сдвига регистра условий, информа ционный выход которого подключен к второму адресному входу дешифратора микропрограмм, второй выход блока синхронизации подключен к второму ин формзц гонноку входу дешифратора усло вий , па фиг. 1 изображена функциональ ная схема устройства; на фиг. 2 схема выполнения дешифратора микрогфограмм; на фиг, 3 схема выполнения ме 11ифратора условий. Устройство содержит дешифратор 1 микропрограмм, дешифратор 2 условий, рэгчстр 3 условий, блок 4 синхрониззци -1, элемент ИЛИ 5, вход 6 логичес ких услозий устройства, информационный выход 7 устройства. Дешифратор млчкропрограмм (фиг. 2} г р:едс таэляет собой программируемую логи-1еску;о матрицу и содержит регист О, блок элементов И 9 блок элеменTOQ 1ЛИ 10, группу инверторов 11. |1еип-:фратор условий (фиг., 3) представляет собой программируемую логическую матрицу и содержит блок элементов И 12 и группу инверторов 13. Устройство работает следующим образом , С перзого выхода дешифратора 1 микропрограмм на первый вход дешифра тора 2 условий поступает код адреса следующего состояния дешифратора 1 микропрограмм. На вторые входы.дешиф ратора 2 условий поступают синхронигирукэщие сигналы из блока А синхрони 4 зации. На выходах дешифратора 2 условий формируется определенная совокупность, синхроимпульсов для каждого адреса, поступающего на первый вход дешифратора 2 условий. Эта совокупность синхроимпульсов соответствует моментам появления логических условий на входе 6 в данном адресе дешифратора 1 микропрограмм. Выходы дешифратора 2 условий соединены с входами элемента ИЛИ 5, на выходе которого появится последовательность упомянутых выше импульсов, которая поступит затем на сдвиговый вход регистра 3 условий, на вход 6 последовательно во времени и синхронно с импульсами на сдвиговом входе регистра 3 условий поступают логические условия из внешнего регистра данных. Таким образом, в регистр 3 условий будет записана совокупность условий, необходимых для данного адреса дешифратора микропрограмм. После этого из блока i синхронизации на вход дешифратора 1 микропрограмм поступает синхроимпульс, обе спечивающий считывание из дешифратора 1 микропрограмм нового выходного сигнала , поступающего на выход 7, и следующего адреса, поступающего на вход дешифратора 2 условий. Устройство применимо для случая последовательного способа представления информации в регистре данных, когда логические условия формируются последовательно на входе 6. Предлагаемое устройство выгодно отличается от известного, так как требует значительно меньших аппаратурных затрат, поскольку разрядность регистра 3 условий выбирается, исходя из количества условий, проверяемых в каждом конкретном адресе дешифратора 1 микропрограмм, что значительно меньше общего количества условий. Кроме того упрощается и блок k синхронизации, из которого исключается схема, специально формирующая синроимпульсы для записи всех логических условий в регистратор 4 условий, поскольку формирование синхроимпульсов из синхронизирующих сигналов выполняется непосредственно в самом дешифраторе 2 услорий одновременно с расшифровкой соответствующего кода адреса, поступающего на первый вход дешифратора 2 условий. Формула изобретения Устройство микропрограммного управления, содержащее дешифратор микро595

программ, первый выход которого является информационным выходом устройства, второй выход соединен с первым адресным входом дешифратора микропрограмм и с первым информационным входом дешифратора условий, первый выход блока синхронизации подключен к входу синхронизации дешифратора микропрограмм, регистр условий, информационный вход которого подключен к входу логических условий устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ, вход которого соединен с информационным выходом дешифратора условий, а вы06

ход - с входом сдвига регистра условий, информационный выход которого подключен к второму адресному входу дешифратора микропрограмм, при этом второй выход блока синхронизации подключен к второму информационному входу дешифратора условий.

Источники информации, принятые во внимание при экспертизе

1.Микроэлектроника. М., Электронная техника. Э7,свр. 3, вып. 5 с. 22-26.

2.Микросхема К U5 ИКб, HyS.tSy.Oie 33 схема принципиальная (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммное устройство управления с контролем переходов | 1987 |

|

SU1411743A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство для обработки изображений | 1985 |

|

SU1309044A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

J

Ж

/

/

. /

Авторы

Даты

1982-09-07—Публикация

1980-12-25—Подача