Признаки

Изобретение относится к вычислительной технике, а именно к устройствам программного управления, и может быть использовано в ЭВМ в качестве контроллера памяти команд.

Функциями контроллера памяти команд в процессоре являются выборка команды, часть декодкрования, изменение содержимого расположенного в контроллере памяти программного счетчика и некоторые другие.

Цель изобретения - повышение быстродействия.

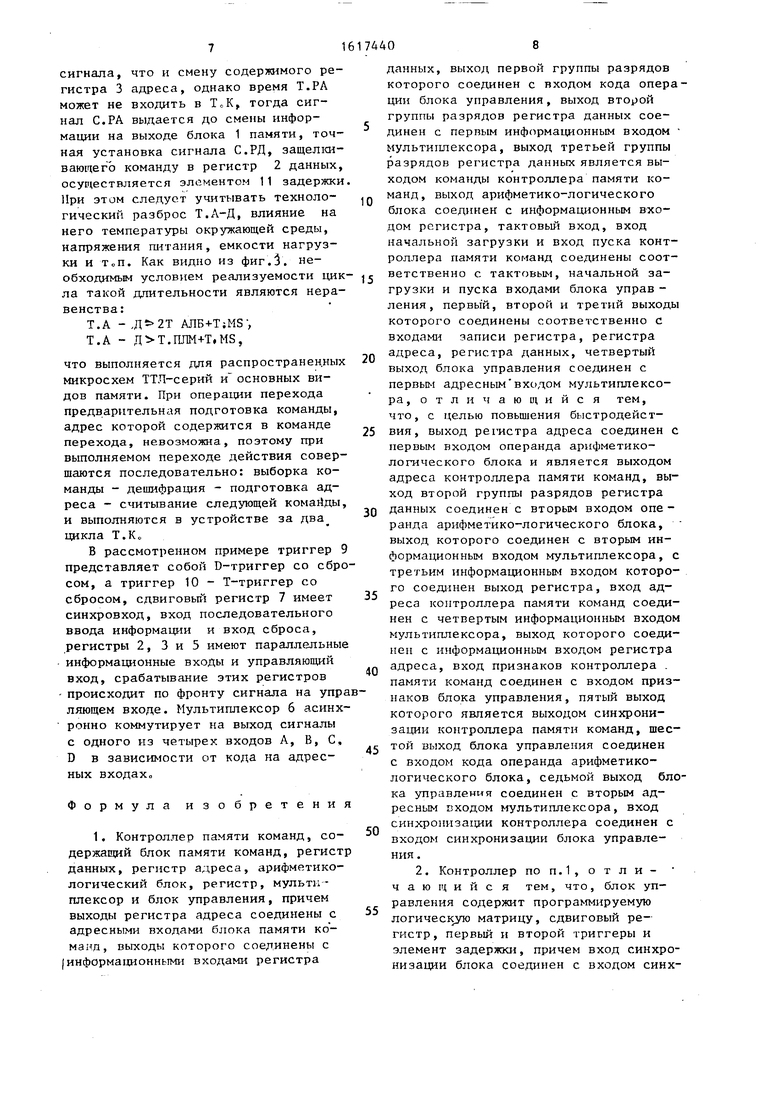

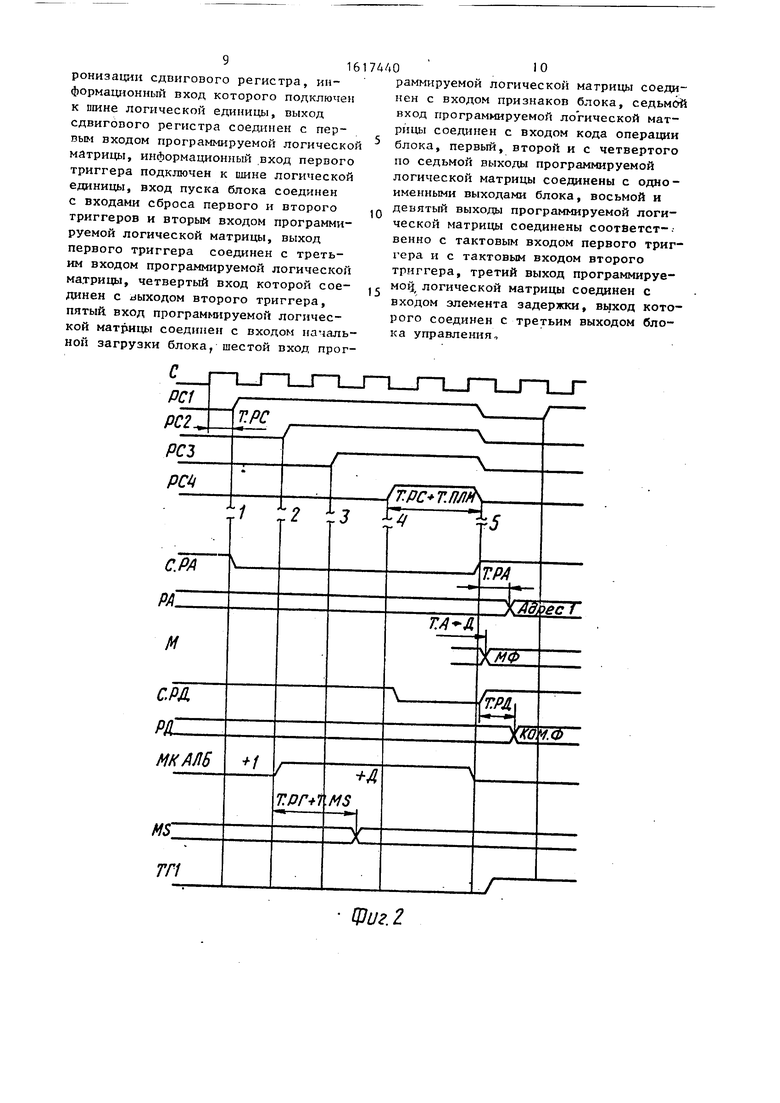

На фиг.1 приведена функциональная схема контроллера; на фиг.2 и 3 - временные диаграммы его работы.

Контроллер памяти команд состоит из блока 1 памяти команд (М), регистра 2 данных (РД), регистра 3 адреса (РА), арифметико-логического блока (АЛБ) 4, регистра (РГ) 5, мультиплексора (MS) 6, а также блока управления, содержащего сдвиговый регистр (PC) 7. программируемую логическую матрицу (ПЛМ) 8, триггеры 9 и 10 и элемент 11 задержки. Входами устройства являются шины начальной загрузки, пуска, синхронизации (с), многоразрядная шина признаков, которые подаются на блок управления, а также шина адреса, соединенная с четвертыми входами мультиплексора 6. Выходами контроллера являются многоразрядные шины команды, программного счетчика и синхронизации, подключенные к выходам регистра данных 2, регистра адреса 3, блока управления -соответственно. Выходы блока управления соединены с управляющими входами АЛБ 4, регистра 2 данных, регистра 3 адреса, регистра 5 и адресными входами мультиплексора 6. Все выходы блока управления являются различными выходами ПЛМ 8, при этом сигнал на регистр 2 данных проходит в блоке управления с выхода ПЛМ 8 через элемент 11 задержки. Выходы мультиплексора 6 соединены с входами регистра 3 адреса, выходы которого соединены с первыми входами АЛБ 4 и с адресными входами блока 1 памяти. Вькоды блока 1 памяти соединены с входами регистра 2 данных, выходы которого разделены на поля кода операции, перехода и команды, подключенные со ответственно к входам ПЛМ 8 в блоке управления, вторым входам АЛБ 4, первым входам мультиплексора 6 и

тя-

ье, . 16174404

выходам команды устройства. Выходы АПБ 4 соединены с входами регистра 5 и вторыми входами мультиплексора 6, третьи входы которого соединены с вы}:одами регистра 5. В блоке управления сигнал синхронизации подается на тактовый вход сдвигового регистра 7, сигнал пуска - на входы сброса триг- д геров 9 и 10 и на вход ПЛМ 8, на

другие входы ПЛМ 8 поступают сигналы с выходов триггеров 9 и 10, сигнал начальной загрузки, а также сигналы с выходов сдвигового регистра 7 и шиJ5 ны признаков. В блоке управления различные выходы ПЛМ В соединены с входом сброса сдвигового регистра 7, тактовыми входами триггеров 9 и 10, информационные входы сдвигового регист- 20 ра 7 и триггера 9 подключены к уровню 1.

Устройство работает следующим образом.

Начальный адрес выполняемой прог25 раммы подается на шину Адрес и записывается в регистр адреса 3 сигналом Начальная загрузка, поступающим на вход ПЛМ 8, при этом обеспечивается наличие на адресном входе муль.JQ типлексора 6 адреса,соответствующего

ПТТ-ТПаАгТПОГ ТТт Т тт -1ттотгл чт .м-.

40

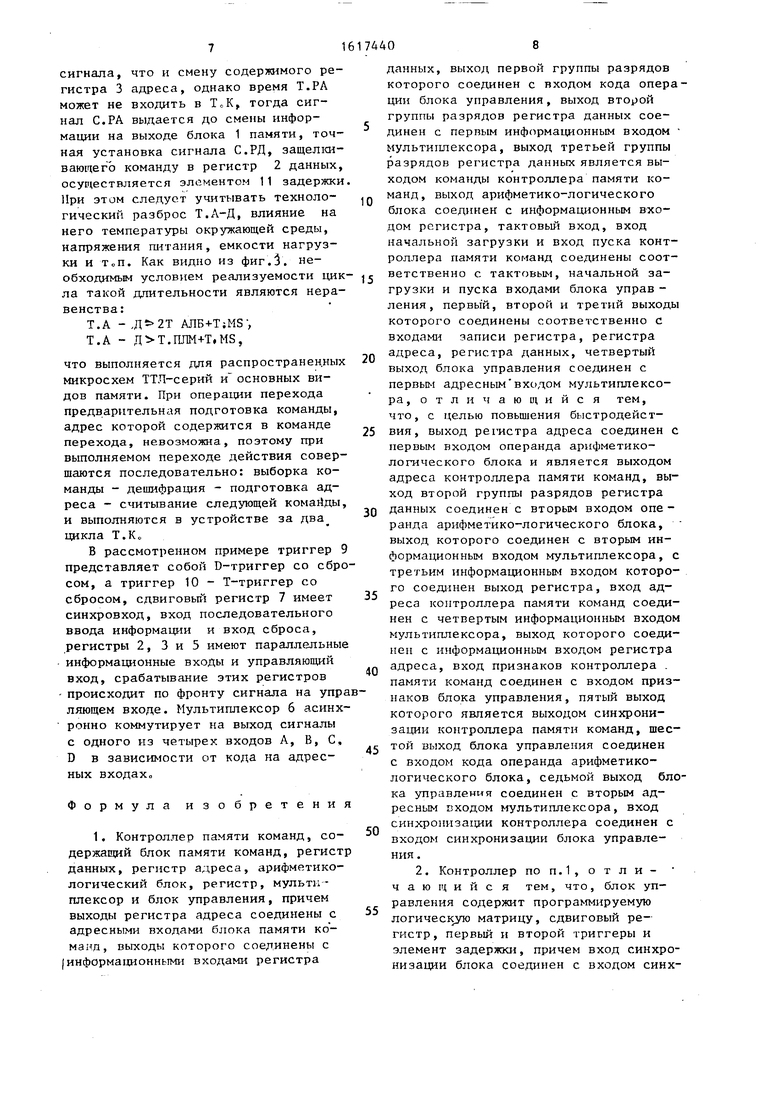

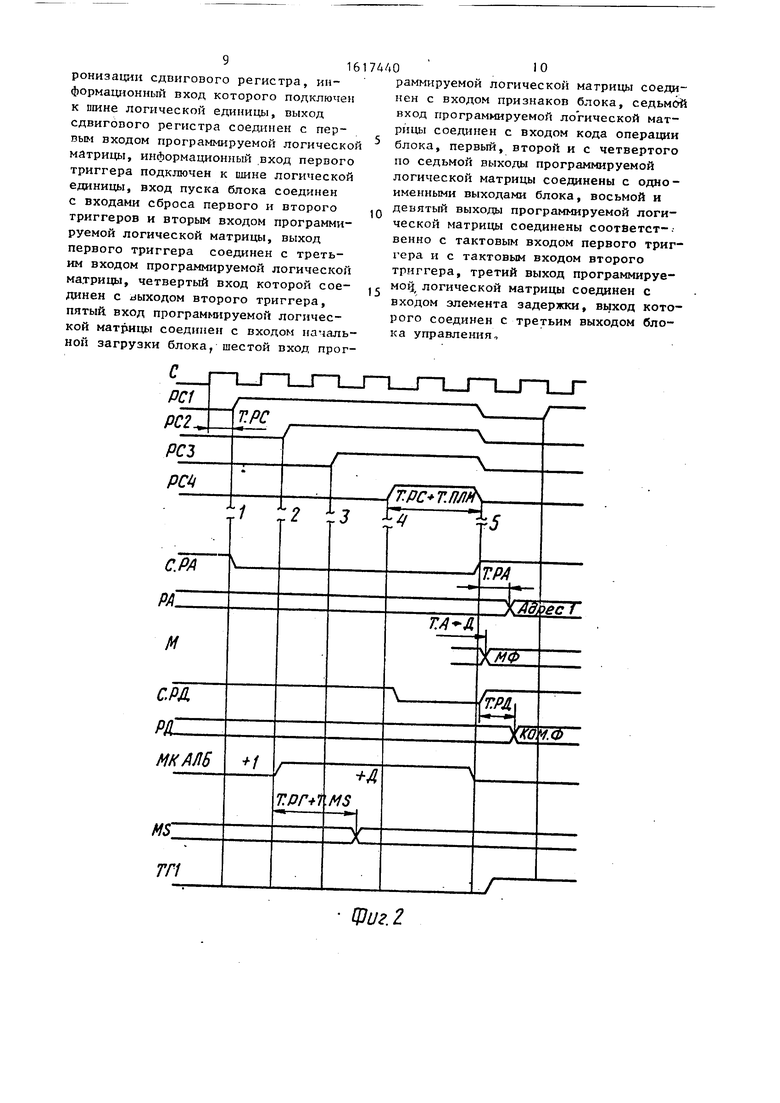

шине Адрес. При подаче на устрой- ство статического сигнала Пуск на рыходе ПЛМ 8, поступающем на вход дброса сдвигового регистра 7, появляется разрешающий уровень и сдвиговый регистр 7 начинает выдавать периодическую последовательность сигналов (фиг.2,3, сигналы PC 1-тРС4). Период этой последовательности определяется временем считывания из блока 1 памяти. Периодический сброс сдвигового регистра осуществляется от одного из его разрядов, определяемого сигналами на входе ПЛМ 8, д5 например,кодом операции, таким образом период сигналов сдвигового регистра может быть переменным, что позволяет менять темп выдачи команд на внешнее устройство. На фиг.2, 3 использованы обозначения:С.РА - сигнал записи в регистр 3 адреса; РА - вьгходы регистра адреса 3; М - выхо- ( ды блока памяти 1; С.РД - сигнал записи в регистр 2 данных; РД - выходы регистра 2 дан21Ых; МК.АЛБ - микрокоманда АЛБ 4; ТГ1 - выход триггера 9; ТГ2 - выход триггера 10; MS - выходы мультиплексора 6; Т.А-Д - время выборки из блока 1 памяти от

50

5

момента полачи адреса до появления данных; Т.РА - время срабатывания ргистра 3 адреса; Т.РД - время срабатывания регистра 2 данных; Т.З - время распространения сигнала через элемент 11 задержки; Т.АЛБ - время срабатывания АЛУ 4; Т.MS - время срабатывания мультиплексора 6 от адресных входов до информационных выходов; Т.PC - время срабатывания сдвигового регистра 7, Т.ПЛМ - время распространения сигнала через ПЛИ 8.

Все управляющие сигналы в устройстве образуются в ПЛМ 8 как комбинация входных сиг 1алов, сигналы с выходов сдвигового регистра 7 используются для стробирования внутри ПЛМ 8 конъюнкций прямых или инверсных значений всех или части входных сигналов (на фиг.2,3 сдвиг влево на l.um сигналов С,РГ1-РГ4 относительно остальных сигналов не показан) .

Пусть счет циклов сдвигового ре- гистра 7 и команд начинается с нуля. Во время нулевого цикла, заканчивающегося выдачей нулевой команды, происходит инициализация конвейера. Отличие выполнения эт.ого цикла от остальных заключается в том, что адрес следующей команды выбирается из регистра 5, что обеспечивается сигналом с выхода триггера9,который предварительно сброшен сигналом и взводится по окончании нулевого цикла сдвигового регистра 7. На фиг.2 рассмотрен нулевой цикл сдвигового регистра, на фиг.З - первьш. Во время выполнения любого 1щкла АЛБ А выполняет сначала операцию сложения кода на входе, соединенном с выходом регистра 3 адреса, с единицей, затем сигналом со сдвигового регистра 7 (пропущенным через ПЛМ 8 для достижения синфазности) происходит переключение микрокоманды АЛБ 4 на сложение данных на его входах. Фиксация увеличенного на единицу значения адреса происходит в регистре 5 по фронту сигнала МК.АЛБ. При ,выполнении первого цикла происходит следующее: на.выходе устройства присутствует команда О, происходит выборка из блока 1 памяти команды, при этом Адрес 1 есть увеличенный на единицу Адрес О, последовательно вычисляются в АЛБ 4

74406

Адрес 1-И, Адрес 1 + смещение , где код смещения содержится в поле - команд переходов, увеличенное на единицу значение адреса фиксируется в регистре 5. Сигналы, образующие поле кода операции.в команде, содержащейся в РД2, поступают на входы ПЛМ 8, дещифрируются за время Т.ПЛМ, Q после чего на выходах ПЛМ появляются сигналы, переключаюпще мультиплексор 6. При этом, если код операции соответствует условному переходу, про-- исходит также дешифрация внещних 15 прд1знакоп Условие (например, выходов регистра состояния центрального процессора). Возможны переходы на команду со следующим адресом на адрес, передаваемый по внещней щине Адрес, 0 на команду, смещенную относительно сс- содержимого регистра адреса 3 (программного счетчика) или на адрес, заданный в команде. Если переход выполняемый, то из ПЛМ 8 на мультиплексор 5 б выдается адрес канала, в котором установлен адрес перехода, запрещается вьщача сигнала С.РД, предварительно выбранная команда Ml оказывается ненужной и теряется, сигналом 0 С.РА в р€;гистре адреса 3 устанавливается адрес перехода, по тому же фронту сигналом из ПЛМ 8 взводится трш гер 10. Последнее обеспечивает завери1ение операции перехода в сле- дующем цикле, а именно: на мул.ти- плексор выдается адрес канала С, к которому подключен регистр 5, таким образом из памяти после команды, на которую совершается переход, начнет 0 предварительно выбираться следующая по порядку команда; разрешается про- хо)эдение сигнала С.РД, записьшающе- го команду, на которую совершен переход в РД2 по фронту сбрасывается 5 триггер 10, сигналом С,РА устанавливается новый адрес. При последовательном выполнении расположенных одна за другой команд процессы выбор- lai команды из памяти и подготовки - Q следующего адреса в устройстве происходят параллельно, темп выдачи таких команд Т.К приближается к времени выборки, из памяти Т.А-Д: если Т.РЛ «Т.А-Д, что выполняется, на- с пример, при использовании широко распространенных регистра серии 530 и памяти серии 537, то защелкивание считанной команды спедует производить по тому же фронту управляющего

сигнала, что и смену содержимого регистра 3 адреса, однако время Т.РА может не входить в ТоК, тогда сигнал С.РА выдается до смены информации на выходе блока 1 памяти, точная установка сигнала С.РД, защелкивающего команду в регистр 2 данных, осуществляется элементом 11 задержки При этом следует учитывать технологический разброс Т.А-Д, влияние на него температуры окружающей среды, напряжения питания, емкости нагрузки и ТоП. Как видно из фиг.З. необходимым условием реализуемости цикла такой длительности являются неравенства:

Т.А - , АЛБ-+-Т;МЗ-,

Т.А - .ГШМ+Т,М8,

что выполняется для распространенных микросхем ТТЛ-серий и основных видов памяти. При операции перехода предварительная подготовка команды, адрес которой содержится в команде перехода, невозможна, поэтому при выполняемом переходе действия совершаются последовательно: выборка команды - дешифрация - подготовка адреса - считывание следующей комайды и выполняются в устройстве за два цикла Т.Ко

В рассмотренном примере триггер 9 представляет собой D-триггер со сбросом, а триггер 10 - Т-триггер со сбросом, сдвиговьй регистр 7 имеет синхровход, вход последовательного ввода информации и вход сброса, регистры 2, 3 и 5 имеют параллельные

. информационные входы и управляющий вход, срабатывание этих регистров

происходит по фронту сигнала на упр ляющем входе. Мультиплексор б асинхронно коммутирует на выход сигналы с одного из четырех входов А, В, С, D в зависимости от кода на адресных входахо

Формула изобретени

1. Контроллер памяти команд, содержащий блок памяти команд, регист данных, регистр адреса, арифметико- логический блок, регистр, мультиплексор и блок управления, причем выходы регистра адреса соединены с адресными входами блока памяти команд, выходы которого соединены с (информационными входами регистра

5

0

5

0

5

0

5

0

5

данных, выход первой группы разрядов которого соединен с входом кода операции блока управления, выход второй группы разрядов регистра данных соединен с первым информа1Ц1онным входом мультиплексора, выход третьей группы разрядов регистра данных является выходом команды контроллера памяти команд, выход арифметико-логического блока соединен с информационным входом регистра, тактовый вход, вход начальной загрузки и вход пуска контроллера памяти команд соединены соответственно с тактовым, начальной загрузки и пуска входами блока управ - ления, первый, второй и третий выходы которого соединены соответственно с входами записи регистра, регистра адреса, регистра данных, четвертый выход блока управления соединен с первым адресным входом мультиплексора, отличающийся тем, что, с целью повышения быстродействия, выход регистра адреса соединен с первыь входом операнда арифметико- логического блока и является выходом адреса контроллера памяти команд, выход второй группы разрядов регистра данных соединен с вторым входом операнда арифметико-логического блока, выход которого соединен с вторым информационным входом мультиплексора, с третьим информационным входом которого соединен выход регистра, вход адреса контроллера памяти команд соединен с четвертым информационным входом мультиплексора, выход которого соединен с информационным входом регистра адреса, вход признаков контроллера . памяти команд соединен с входом признаков блока управления, пятый выход которого является выходом синхронизации контроллера памяти команд, шестой выход блока управления соединен с входом кода операнда арифметико- логического блока, седьмой выход блока управления соединен с вторым адресным входом мультиплексора, вход синхрониза1даи контроллера соединен с входом синхронизации блока управления.

2. Контроллер по п.1, отличаю щ и и с я тем, что, блок управления содержит программируемую логическую матрицу, сдвиговый регистр, первый и второй триггеры и элемент задержки, причем вход синхронизации блока соединен с входом синхМ

Т.

Е

МФ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор | 1989 |

|

SU1725224A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

Устройство относится к вычислительной технике и может быть использовано в высокопроизводительных процессорах. Цель изобретения - повышение быстродействия. Контроллер памяти команд состоит из блока памяти 1, регистра данных 2, регистра адреса 3, арифметико-логического блока 4, регистра 5, мультиплексора 6, а также блока управления, содержащего сдвиговый регистр 7, программируемую логическую матрицу 8, триггеры 9 и 10, элемент задержки 11. Повышение быстродействия достигается за счет того, что в контроллере процессы считывания команды, выдачи предыдущей команды, подготовка адреса следующей команды происходят параллельно, таким образом, цикл работы контроллера приближается к времени выборки из памяти. 1 з.п. ф-лы, 3 ил.

МНАЛ6

pr

MS

Фиг. 2

+л

(Риг.3

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР f 1206781, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-01—Подача