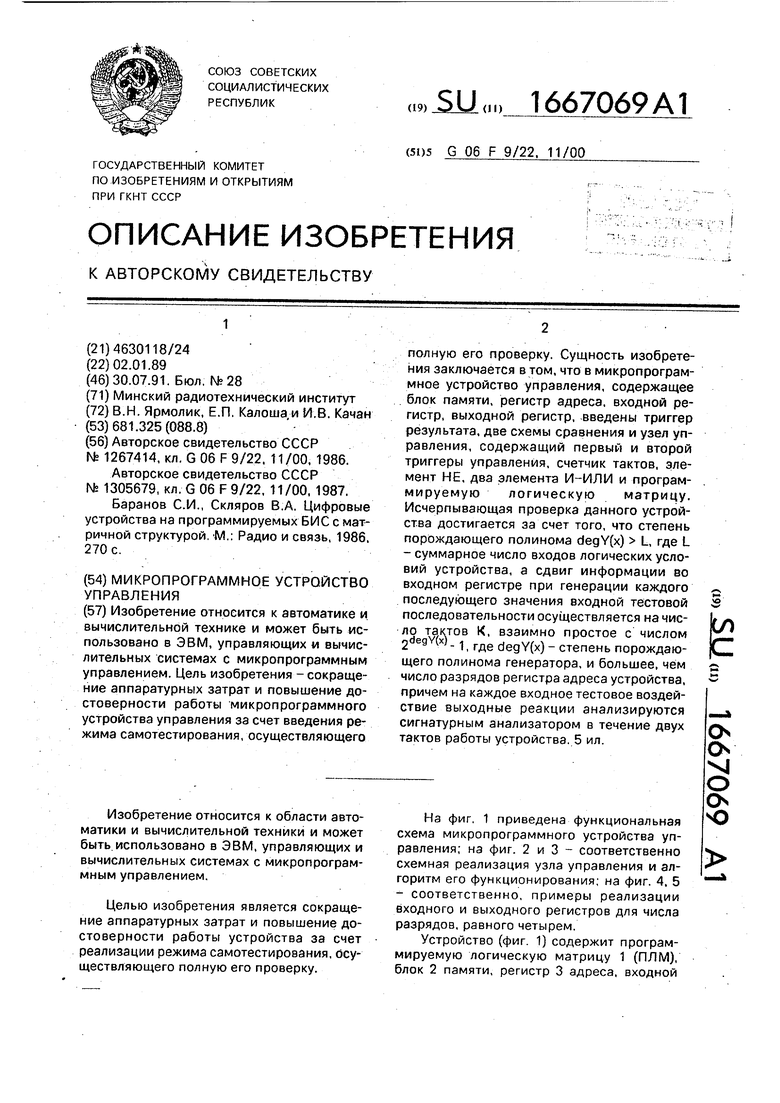

регистр 4, выходной регистр 5, узел 6 управления, первую 7 и вторую 8 схемы сравнения, триггер 9 результата.

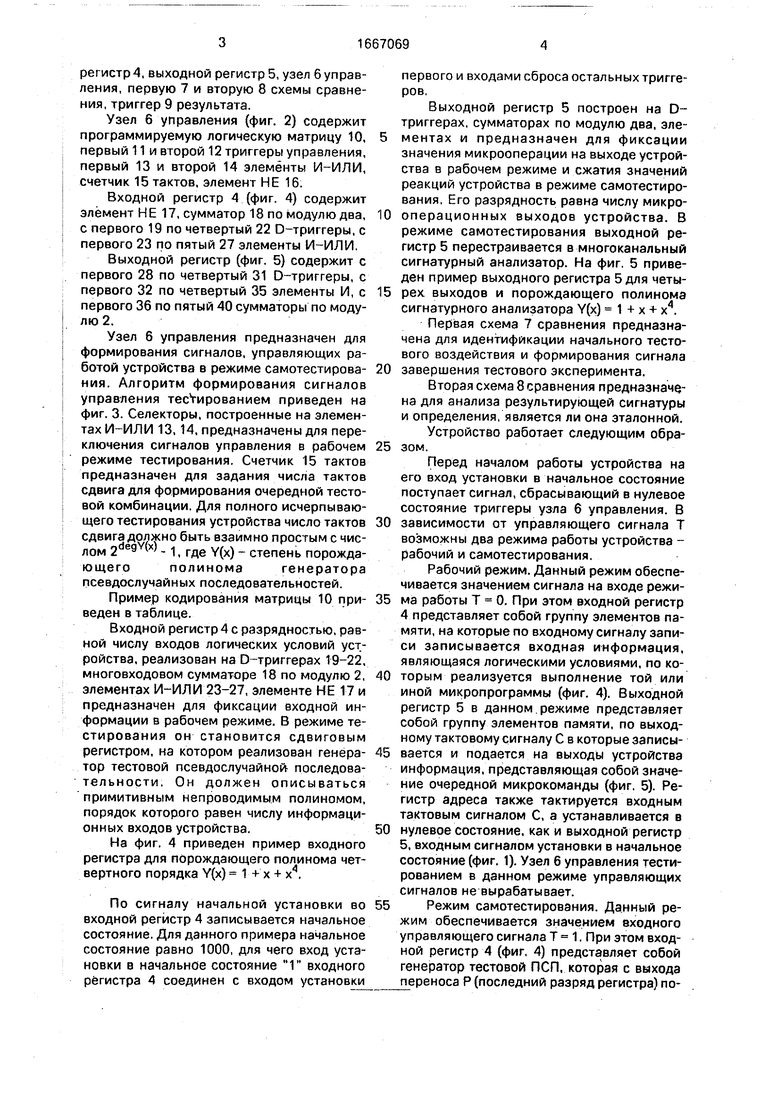

Узел 6 управления (фиг. 2) содержит программируемую логическую матрицу 10, первый 11 и второй 12 триггеры управления, первый 13 и второй 14 элементы И-ИЛИ, счетчик 15 тактов, элемент НЕ 16.

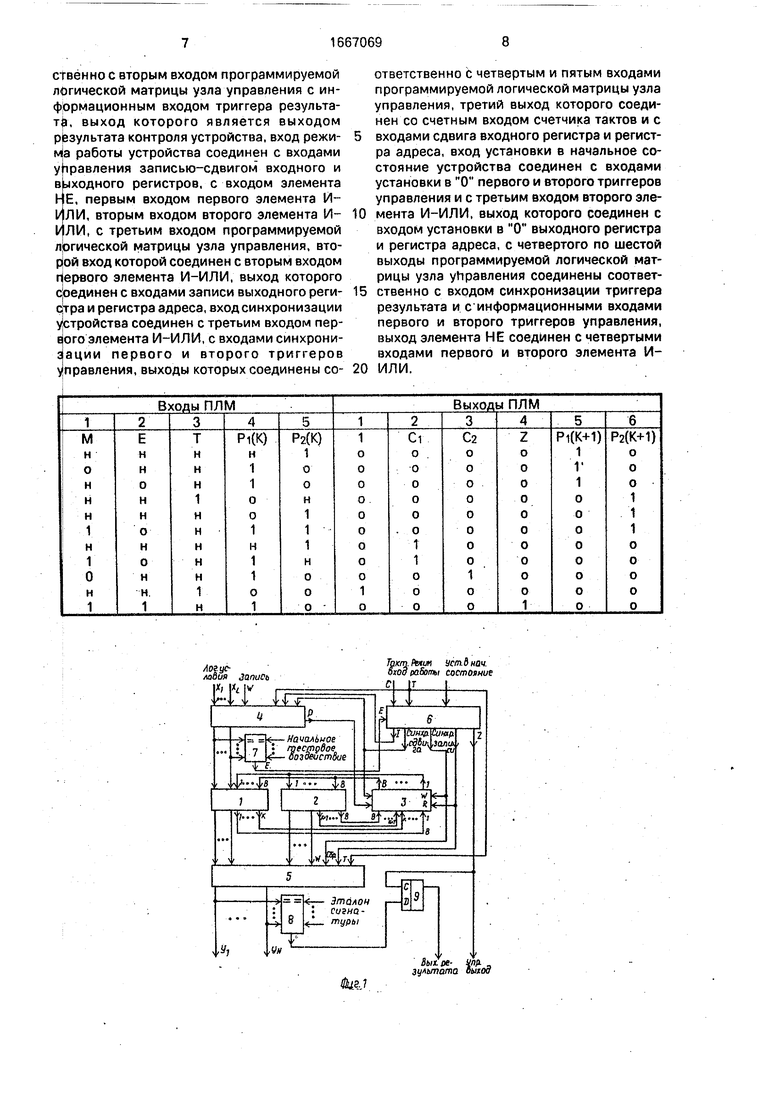

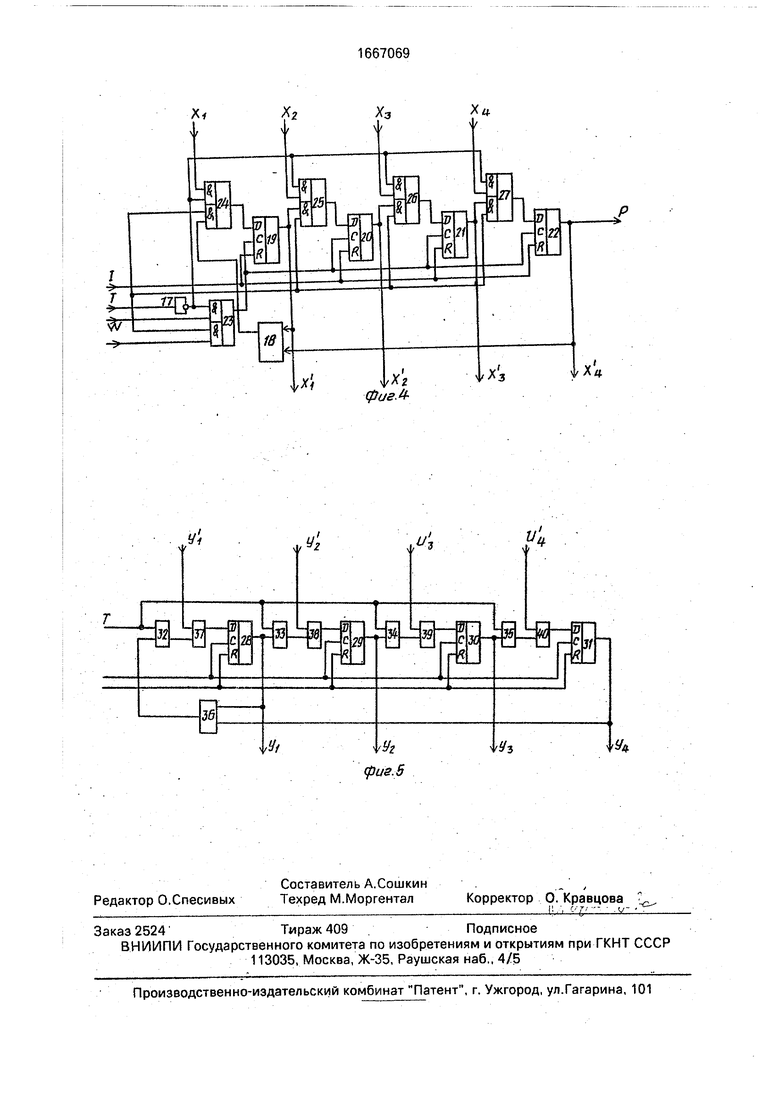

Входной регистр 4 (фиг. 4) содержит элемент НЕ 17, сумматор 18 по модулю два, с первого 19 по четвертый 22 D-триггеры, с первого 23 по пятый 27 элементы И-ИЛИ.

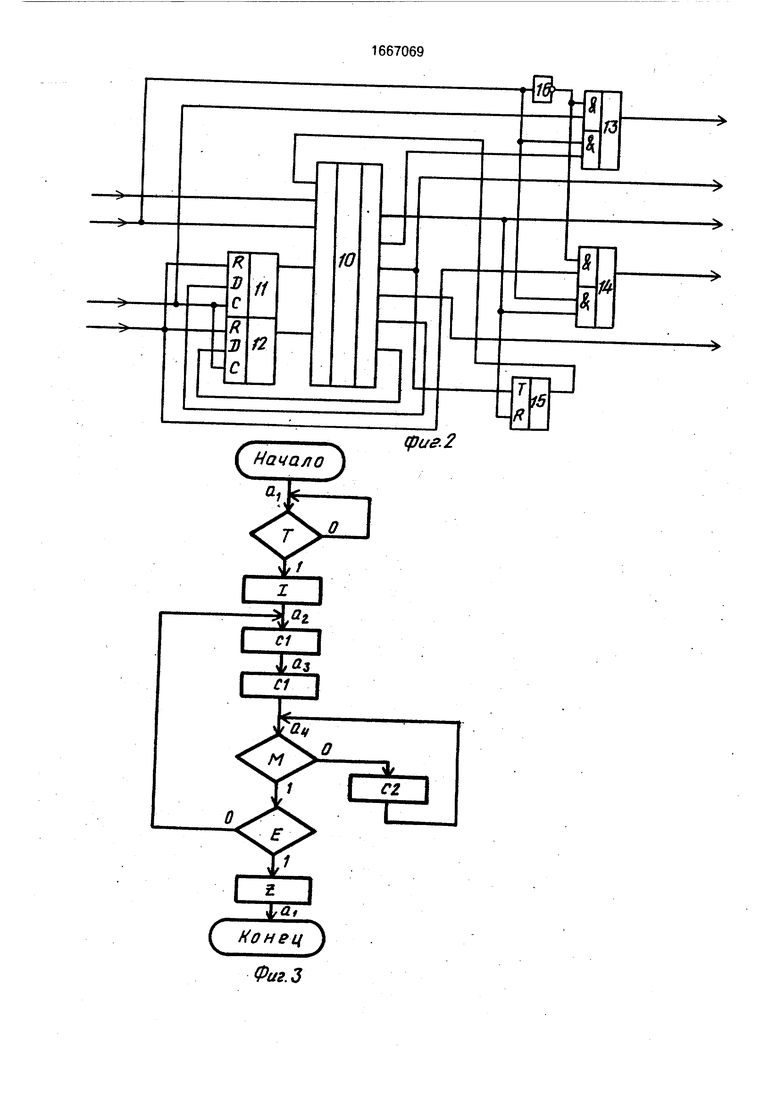

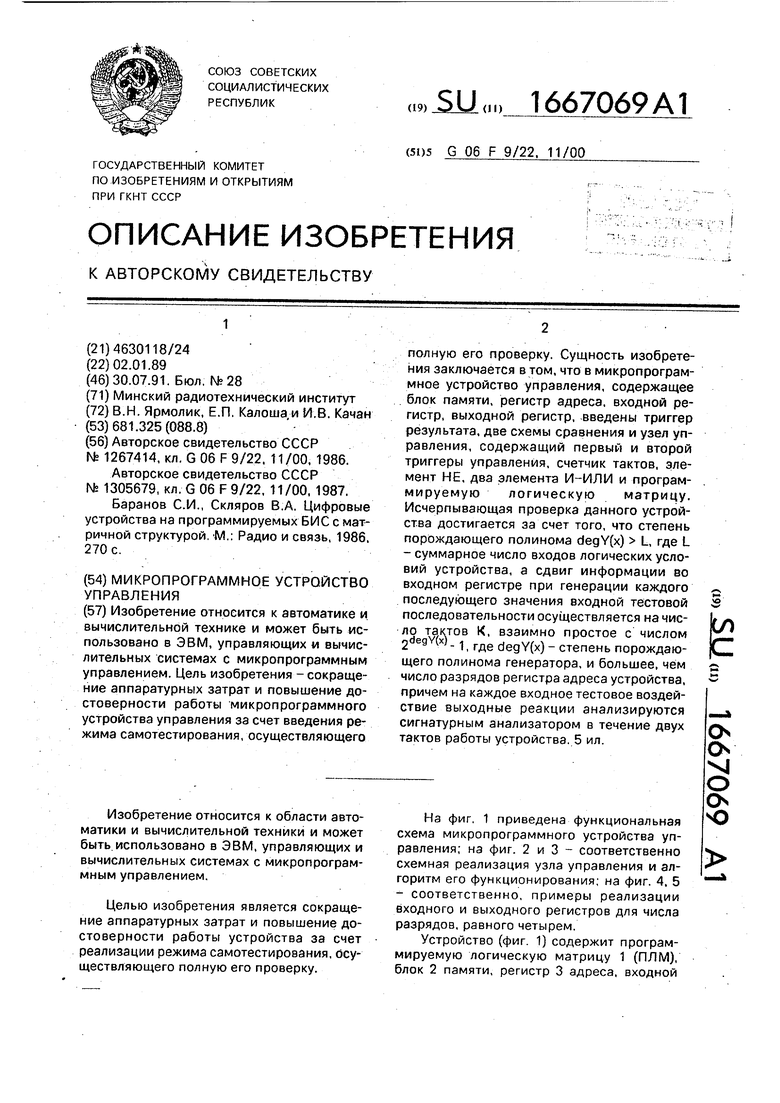

Выходной регистр (фиг. 5) содержит с первого 28 по четвертый 31 D-триггеры, с первого 32 по четвертый 35 элементы И, с первого 36 по пятый 40 сумматоры по модулю 2.

Узел 6 управления предназначен для формирования сигналов, управляющих работой устройства в режиме самотестирования. Алгоритм формирования сигналов управления тестированием приведен на фиг. 3. Селекторы, построенные на элементах И-ИЛИ 13,14, предназначены для переключения сигналов управления в рабочем режиме тестирования. Счетчик 15 тактов предназначен для задания числа тактов сдвига для формирования очередной тестовой комбинации. Для полного исчерпывающего тестирования устройства число тактов сдвига должно быть взаимно простым с числом 2degY - 1, где Y(x) - степень порожда- ющегополиномагенератора

псевдослучайных последовательностей.

Пример кодирования матрицы 10 приведен в таблице.

Входной регистр 4 с разрядностью, равной числу входов логических условий устройства, реализован на D-триггерах 19-22, многовходовом сумматоре 18 по модулю 2, элементах И-ИЛИ 23-27, элементе НЕ 17 и предназначен для фиксации входной информации в рабочем режиме. В режиме тестирования он становится сдвиговым регистром, на котором реализован генератор тестовой псевдослучайной последовательности. Он должен описываться примитивным непроводимым полиномом, порядок которого равен числу информационных входов устройства.

На фиг. 4 приведен пример входного регистра для порождающего полинома четвертного порядка Y(x) 1 + х + х .

По сигналу начальной установки во входной регистр 4 записывается начальное состояние. Для данного примера начальное состояние равно 1000, для чего вход установки в начальное состояние 1 входного регистра 4 соединен с входом установки

первого и входами сброса остальных триггеров.

Выходной регистр 5 построен на D- триггерах, сумматорах по модулю два, элементах и предназначен для фиксации значения микрооперации на выходе устройства в рабочем режиме и сжатия значений реакций устройства в режиме самотестирования. Его разрядность равна числу микро0 операционных выходов устройства. В режиме самотестирования выходной регистр 5 перестраивается в многоканальный сигнатурный анализатор. На фиг. 5 приведен пример выходного регистра 5 для четы5 рех выходов и порождающего полинома сигнатурного анализатора Y(x) 1 + х + х4.

Первая схема 7 сравнения предназначена для идентификации начального тестового воздействия и формирования сигнала

0 завершения тестового эксперимента.

Вторая схема 8 сравнения предназначена для анализа результирующей сигнатуры и определения, является ли она эталонной. Устройство работает следующим обра5 зом.

Перед началом работы устройства на его вход установки в начальное состояние поступает сигнал, сбрасывающий в нулевое состояние триггеры узла 6 управления. В

0 зависимости от управляющего сигнала Т возможны два режима работы устройства - рабочий и самотестирования.

Рабочий режим. Данный режим обеспечивается значением сигнала на входе режи5 ма работы Т 0. При этом входной регистр 4 представляет собой группу элементов памяти, на которые по входному сигналу записи записывается входная информация, являющаяся логическими условиями, по ко0 торым реализуется выполнение той или иной микропрограммы (фиг. 4). Выходной регистр 5 в данном режиме представляет собой группу элементов памяти, по выходному тактовому сигналу С в которые записы5 вается и подается на выходы устройства информация, представляющая собой значение очередной микрокоманды (фиг. 5). Регистр адреса также тактируется входным тактовым сигналом С. а устанавливается в

0 нулевое состояние, как и выходной регистр 5, входным сигналом установки в начальное состояние (фиг. 1). Узел 6 управления тестированием в данном режиме управляющих сигналов не вырабатывает.

5 Режим самотестирования. Данный режим обеспечивается значением входного управляющего сигнала Т 1. При этом входной регистр 4 (фиг, 4) представляет собой генератор тестовой ПСП, которая с выхода переноса Р (последний разряд регистра) поступает на соответствующий вход регистра адреса (фиг. 1). Управляющий сигнал записи блокируется во входном регистре 4, а внешний сигнал установки в начальное состояние блокируется вторым селектором 14 узла 6 управления (фиг. 3).5

Узел 6 управления самотестированием функционирует по алгоритму, представленному на фиг. 2. При поступлении на вход устройства сигнала Т 1 формируется сигнал установки узлов устройства в начальное 10 состояние 1, по которому во входной регистр 4 записывается начальное состояние генератора ПСП, а регистр 3 адреса, выходной регистр 5 устройства, а также счетчик 15 тактов устанавливаются в нулевое состоя- 15 ние. Затем узел 6 управления дважды формирует сигнал синхронизации записи устройства (С1), выполняя в первом такте запись реакции ПЛМ 1 и блока 2 памяти на входную тестовую комбинацию в регистр 3 20 адреса и сигнатурный анализатор, реализованный на выходном регистре 5, а во втором такте, используя эту реакцию в качестве входной тестовой комбинации - запись значений выходов ПЛМ 1 и блока 2 памяти 25

в сигнатурный анализатор. Затем по сигналам синхронизации сдвига (С2) происходит формирование очередной тестовой комбинации. Число тактов сдвига при формирова- нии тестовой последовательности 30 определяется счетчиком 15 тактов (фиг. 3). После необходимого числа тактов сдвига счетчик 15 тактов вырабатывает сигнал М 1, и выполняется очередной цикл анализа реакций сигнатурным анализатором по сиг- 35 налам синхронизации записи С1. В случае, когда очередная сформированная тестовая последовательность будет равна начальной, первая схема 7 сравнения вырабатывает сигнал Е 1 и узел б управления 40 сформирует сигнал записи результата тестирования, полученного второй схемой 8 сравнения, в триггер 9 результата. Этот сигнал поступает на вход устройства, сигнализируя о том, что процесс самотестирования 45 закончен и значение результата подается на выход устройства. Затем, если в узле 6 управления на входе Т будет установлен ноль, устройство перейдет в рабочий режим. В противном случае цикл самотестиро- 50 вания повторится.

В устройстве организовано самотестирование в произвольные моменты времени методами тестирования комбинационных схем.55

Полнота проверки микропрограммного стройства управления достигается за счет исчерпывающего тестирования ПЛМ и блока памяти (комбинационной части устройства) путем формирования тестовой псевдослучайной комбинации на их входах, прямого анализа реакции на входные воздействия, формируемых на выходах устройства, и косвенного анализа реакции ПЛМ и блока памяти, формируемых в цепях обратных связей, при одновременной проверке регистра адреса устройства. Формула изобретения Микропрограммное устройство управления, содержащее программируемую логическую матрицу, блок памяти, регистр адреса, входной регистр, выходной регистр, причем вход логических условий устройства соединен с информационным входом входного регистра, выход которого соединен с первым входом программируемой логической матрицы, выход которой соединен с первым информационным входом выходного регистра, выходы которого являются выходами микроопераций устройства, выход поля микроопераций блока памяти соединен с вторым информационным входом выходного регистра, второй выход программируемой логической матрицы и выход поля адреса блока памяти соединены соответственно с первым и вторым информационными входами регистра адреса, выход которого соединен с вторым входом программируемой логической матрицы и с адресным входом блока памяти, вход записи входного регистра является входом записи устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат и повышения достоверности работы устройства за счет реализации режима самотестирования, в устройство дополнительно введены первая и вторая схемы сравнения, триггер результата, узел управления, содержащий первый и второй триггеры управления, счетчик тактов, элемент НЕ, первый и второй элементы И-ИЛИ, программируемую логическую матрицу, причем входы начального тестового воздействия и эталонной сигнатуры устройства соединены с первыми входами соответственно первой и второй схем сравнения, первый выход программируемой логической матрицы узла управления соединен с первым входом второго элемента И-ИЛИ, с входом установки в О счетчика тактов и входного регистра, выход старшего разряда которого соединен с последовательным информационным входом регистра адреса переполнения счетчика тактов, соединен с первым входом программируемой логической матрицы узла управления, выходы входного и выходного регистров соединены с вторыми входами соответственно первой и второй схем сравнения, выходы которых соединены соответственнос вторым входом программируемой логической матрицы узла управления с информационным входом триггера результата, выход которого является выходом результата контроля устройства, вход режи- ма работы устройства соединен с входами управления записью-сдвигом входного и выходного регистров, с входом элемента НЕ, первым входом первого элемента И- ИЛИ, вторым входом второго элемента И- ИЛИ, с третьим входом программируемой логической матрицы узла управления, второй вход которой соединен с вторым входом первого элемента И-ИЛИ, выход которого соединен с входами записи выходного реги- стра и регистра адреса, вход синхронизации устройства соединен с третьим входом первого элемента И-ИЛИ, с входами синхронизации первого и второго триггеров управления, выходы которых соединены со-

ответственно с четвертым и пятым входами программируемой логической матрицы узла управления, третий выход которого соединен со счетным входом счетчика тактов и с входами сдвига входного регистра и регистра адреса, вход установки в начальное состояние устройства соединен с входами установки в О первого и второго триггеров управления и с третьим входом второго элемента И-ИЛИ, выход которого соединен с входом установки в О выходного регистра и регистра адреса, с четвертого по шестой выходы программируемой логической матрицы узла управления соединены соответственно с входом синхронизации триггера результата и с информационными входами первого и второго триггеров управления, выход элемента НЕ соединен с четвертыми входами первого и второго элемента И- ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Программируемая логическая матрица | 1988 |

|

SU1621020A1 |

| Устройство анализа результатов тестирования для локализации двукратных неисправностей | 2016 |

|

RU2633908C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| УСТРОЙСТВО АНАЛИЗА РЕЗУЛЬТАТОВ ТЕСТИРОВАНИЯ ДЛЯ ПОИСКА НЕИСПРАВНЫХ БЛОКОВ | 2013 |

|

RU2540805C2 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ, управляющих и вычислительных системах с микропрограммным управлением. Цель изобретения - сокращение аппаратурных затрат и повышение достоверности работы микропрограммного устройства управления за счет введения режима самотестирования, осуществляющего полную его проверку. Сущность изобретения заключается в том, что в микропрограммное устройство управления, содержащее блок памяти, регистр адреса, входной регистр, выходной регистр, введены триггер результата, две схемы сравнения и узел управления, содержащий первый и второй триггеры управления, счетчик тактов, элемент НЕ, два элемента И - ИЛИ и программируемую логическую матрицу. Исчерпывающая проверка данного устройства достигается за счет того, что степень порождающего полинома DEG Y(X)Λ, где L - суммарное число входов логических условий устройства, а сдвиг информации во входном регистре при генерации каждого последующего значения входной тестовой последовательности осуществляется на число тактов K, взаимно простое с числом 2DEGY(X) - 1, где DEGY(X) - степень порождающего полинома генератора, и большее, чем число разрядов регистра адреса устройства, причем на каждое входное тестовое воздействие выходные реакции анализируются сигнатурным анализатором в течение двух тактов работы устройства. 5 ил.

лог усЛОв januCb

;r4 i |чЕ

i-Начальное

тестубое

4- ооздеистоие

. )

Тахт ист6нач вюд paSomu состояние

С

tfct

амфршд ,сдйи-л)

f

у

№1

tut ре- ЦЛА

зультота

Сначал(Г

( КонУц } Фиг.З

Xf

Л2

X3

Хд

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Баранов С.И., Скляров В.А | |||

| Цифровые устройства на программируемых БИС с матричной структурой | |||

| М.: Радио и связь, 1986, 270с. | |||

Авторы

Даты

1991-07-30—Публикация

1989-01-02—Подача