(5) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1976 |

|

SU750565A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Регистр сдвига | 1976 |

|

SU682950A1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Передатчик последовательного кода | 1988 |

|

SU1683177A1 |

| Ячейка памяти для регистра сдвига | 1978 |

|

SU752491A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

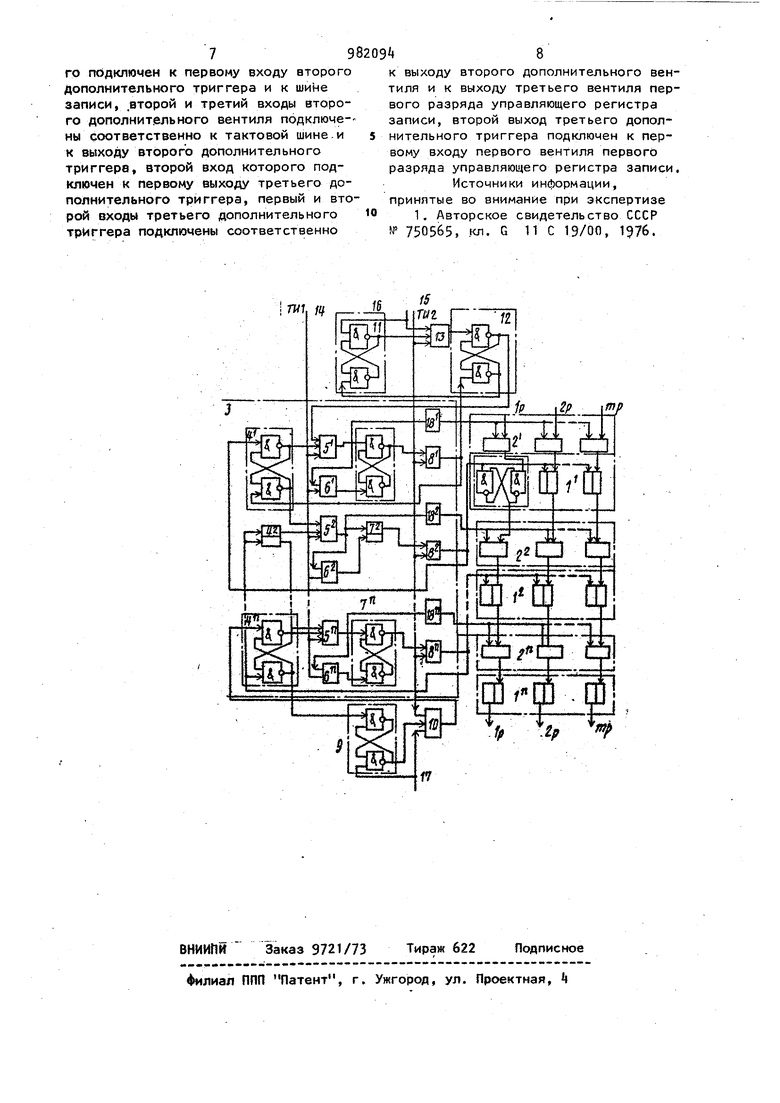

Изобретение относится к вычислительной технике и может быть и-спользовано в технике связи и вычислительной технике, в маетности для сопряжения асинхронных источника и приемника информации. По основному авт.св. № 750565 известно буферное запоминающее устройство ( ВЗУ), допускающее независимые запись и считывание информации, импульсы считывания и тактовые импульсы БЗУ могут быть асинхронны. Это устройство содержит регистры чисел, информационные входы и выходы который подключены к входам данных и пер вым входам последующих вентилей пере записи, управляющий регистр записи каждый разряд которого состоит из трех вентилей, первые входы которых подключены к соответствующим тактовым шинам вспомогательного триггера .и основного триггера, триггера считывания и вентиля считывания, первые входы ко торых соединены с шиной считывания. Первый выход основного триггера управляющего регистра подключен к второму входу первого вентиля, выход которого соединен с вторыми входами соответствующих вентилей перезаписи и первым входом вспомогательного триггеа, выход которого подключен к второму входу третьего вентиля, выход которого подключен к входу сброса соответствующего регистра числа и к второму входу основного триггера, выход вентиля считывания через основной триггер последнего разряда управляющего регистра соединен с другим входом дополнительного триггера, выход которого подключен к второму входу вентиля считывания , третий вход которого соединен с тактовой шиной, второй выход основного триггера каждого разряда управляющего регистра записи подключен к третье входу первого вентиля последующего разряда, выход которого соединен с входом второго вентиля, выхбд по98следивго подключен к второму входу вспомогательного триггера, а выход третьего вентиля каждого разряда подключен к первому входу основного триггера предадущего разряда управляющего регистра записи 11 }, Недостаток этого устройства тактовая частота поступления информации ограничивает скорость продвижения информации по регистрам чисел БЗУ так как тактовая частота ВЗУ должна быть синхронна импульсам записи, что вызывает задержку информации БЗУ, которая тем больше, чем ниже тактовая частота поступления информации и боль ше регистров чисел в БЗУ. Цель изобретения - повышение быстродействия буферного запоминающего устройства. Поставленная цель достигается тем, что в устройство введены второй и тре тий дополнительные триггеры и второй дополнительный вентиль, первый вход которого подключен к первому входу второго дополнительного триггера и к шине записи, второй и третий входы второго дополнительного вентиля подключены соответственно к тактовой шине и к выходу второго дополнительного триггера, второй вход которого под ключен к первому выходу третьего дополнительного триггера, первый и второй входы третьего дополнительного триггера подключены соответственно к выходу второго дополнительного вентиля и к выходу третьего вентиля пер,вого разряда управляющего регистра за писи , второй выход третьего дополнительного триггера подключен к первому входу первого вентиля первого разряда управляющего регистра записи. На чертеже изображенафункциональная схема предлагаемого устройства. Устройство содержитт-разрядные регистры T-l чисел, соединенные.через вентили перезаписи, управля ющий регистр 3 записи,; включающий основные триггеры , подключенные к входам первых вентилей выход которых подключены к входам вторых вентилей 6 -б, вспомогательные триггеры входы которых подключены к выходам вентилей и 6-6, а выходы подключены к входам третьих вентилей 8-8, триггер 9 считывания, выход которого подключен к входу вентиля 10 считывания, выход которого 4 подключен к входу основного триггера Ц, а выход основного триггера подключен к второму входу триггера 9 считывания, и второй дополнительный триггер 11 блокировки, третий дополнительный триггер 12 записи, второй дополнительный вентиль 13 записи, выход которого подключен к входу третьего дополнительного триггера 12 запи выводы которого подключены к вхоДУ первого вентиля S ду первого вентиля 5 первого разряда управляющего регистра и к входу второго дополнительного триггера 11 блокировки, выход которого соединен с входом второго дополнительного вентиля 13 записи. К входам вентилей 5 и 6 подключена шина l4 тактовых .импульсов ТИ1. К входам вентилей 13, 8 и 10 подключена шина 15 тактовых импульсов ТИ2, К входу вентиля 13 и входу дополнительного триггера 11 подключена шина 16 записи информации. К входу триггера 9 Ийентиля 10 подключена шина 17 считывания информации, а выходы вентилей S -S соединены с входами вентилей 2-2 перезаписи через инверторы 18 -18 . Выходы вентилей подключены к регистрам f - числа И-к вторым входам основных триггеров k -k соответствующего разряда и к першзму входу основных триггеров f- предшествующего разряда управляющего регистра. Выход вентиля 8 подключен к второму входу основного триггера . Устройство работает следующим образом. На шины 1 if и 15 тактовых импульсов постоянно поступают серии тактовых импульсов ТИ1 и ТИ2 соответственно, сдвинутые по фазе одна относительно другой. В исходном состоянии с триггера 11 на вентиль 13, с триггера 12 на триггер 11, с триггера 4 на вентиль 5 и с триггера 9 на вентиль 10 поступает высокий потенциал. Для записи информации на шину 16 поступает импульс, который подтверждает состояние триггера 11 и вместе с первым импульсом ТИ2 через вентиль 13 переключает триггер 12, который выдает высокий потенциал на вентиль 5 и переключает триггер 11, который снимает с вентиля 13 высокий потенциал и тем сашм блокирует импульс записи. Первый же после переключения триггера 12 импульс ТИ1 через вентиль 5 и вентиль 2 записывает в регистр 1 первоеуя-разрядное слово, одновременно вспомогательный триггер Т управля емого регистра перею1юча ется и подает высокий потенциал на вентиль 8. Второй импульс ТИ2 через вентиль 8 переключает триггер 12, который снимает высокий потенциал с вентиля 5 и подает высокий потенциал на триггер 1 Этот же импульс ТИ2 через вентиль 8 переключает триггер . Триггер также снимает высокий потенциал с вен тиля 5 и подает высокий потенциал на вентиль 5. Пауза между импульсами за писи переключает триггер 11, который подает высокий потенциал на вентиль 13. Второй импульс TMt через вентиль 5 и вентиль 7 записывает слово в регистр 1, одновременно триггер 7 управляющего регистра переключается и подает высокий потенциал на вентиль 8 . Третий импульс ТИ2 через вентиль 8 сбрасывает регистр 1, переключает ( и Г триггеры (- и так, что на вентили 5 и 5 поступают соответственно высокий и низкий потенциал. Этим же третьим импульсом itH2, если поступит следующий импульс записи, через вентиль- 13 переключается триггер 12, который выдает высокий по тенциал на вентиль 5 Четвертый импульс ТИ1 через вентиль S и В записывает новое слово в регистр И, Если импульс записи не приходит или длител ность импульса записи много больше длительности импульсов Till (ТИ2, то новые слова на регистр 1 не записываются, а под действием тактовых сигналов ТН1 и ТИ2 слово передвигается по регистрам 1-1 и фиксируется в h-разряде. Запись нового слова начина ется при приходе следующего импульса записи. В случае, когда из-за асинхронности импульсов записи и такг товых импульсов импульс записи Перекрывает тактовый импульс частично, на выход вентиля 13 пЬступает импульс с длительностью (и амплитудой) недостаточной для переключения триггера 12, и описанный цикл записи осуществляется следующим тактовым импульсом ТИ2. Считывание информации, т.е. обновление ее в выходном регистре, осущест вляется подачей импульса считывания на шину 17. Импульс считывания подтвер : дает состояние триггера 9 и поступает яа вентиль 10, Первый же после воздействия импульса считывания импульс ТН2 переключает триггер j , 9 6 который выдает высокий потенциал на вентиль 5 и переключает триггер 9. Триггер 9 снимает с вентиля 10 auto- , кий потенциал и блокирует импульс считывания. Первый после BOSAelRctBMfl импульса считывания импульс ТИ1. через вентиль 5 и вентили 2 записывает в регистр 1 новоеw-разрядное слово. Второй импульс ТИ2 через вентиль 8 переключает тригге1э i, который снимает высокий потенциал с вентиля 5 и подтверждает состояние триггера 9. Пауза между импульсами считывания . переключает триггер 9. который подает на вентиль 10 высокий потенциал и цикл считывания повторяется при подаче следующего импульса считывания. . Из работы устройства видноi чтб 53У допускает независимые запись и считывание инфО(жации, импульсы записи, считывания, тактовые импульсы могут быть асинхронными. Частота такто1вых импульсов может быть много больре, чем частота импульсов записи и считывания. Для надежной работы устройства длительность импульсоа записи (считывания) должна превышать длительность тактового импульса n|W .сква : ности последних Q62) или длительность паузы тактовыми импульсами ( при 67/ 2} не менее, чем на время переклочения дополнительного 11 ( 9), увеличенного на мак|симальную разность времени включения и выключения дополнительного вентиля 13 (10) которая не превышает времени вклоцения дополнительного вентиля 13 (10), а длительность паузы между импульсами записи (считывания должна быть не меньше переключения триггера 11 (3), Регистры 1-1 ранения п-разрядных чисел могут быть реаго зованы на ft,V а регистр наТЭ-триггерах потенциальной логики. Упрайпяющий регистр записи может быть многотактовым. изобретения Буферное запоминающее устройство по авт.св. ff 750565, отличаюее с я тем, что, с целью повышения быстродействия устройства, в него введены второй и третий дополниельные триггеры и второй дополни ьный вентиль, первый вход которого подключен к первому входу второго дополнительного триггера и к шине записи, второй и третий входы второго дополнительного вентиля подкпюче-ны соответственно к тактовой шине.и к выходу второго дополнительного триггера второй вход которого подключен к первому выходу третьего дополнительного триггера, первый и второй входы третьего дополнительного триггера подключены соответственно

ITWT

к выходу второго дополнительного вентиля и к выходу третьего вентиля первого разряда управляющего регистра записи, второй выход третьего дополнительного триггера подключен к первому входу первого вентиля первого разряда управляющего регистра записи.

Источники информации, принятые во внимание при экспертизе

г щ

Авторы

Даты

1982-12-15—Публикация

1981-02-11—Подача