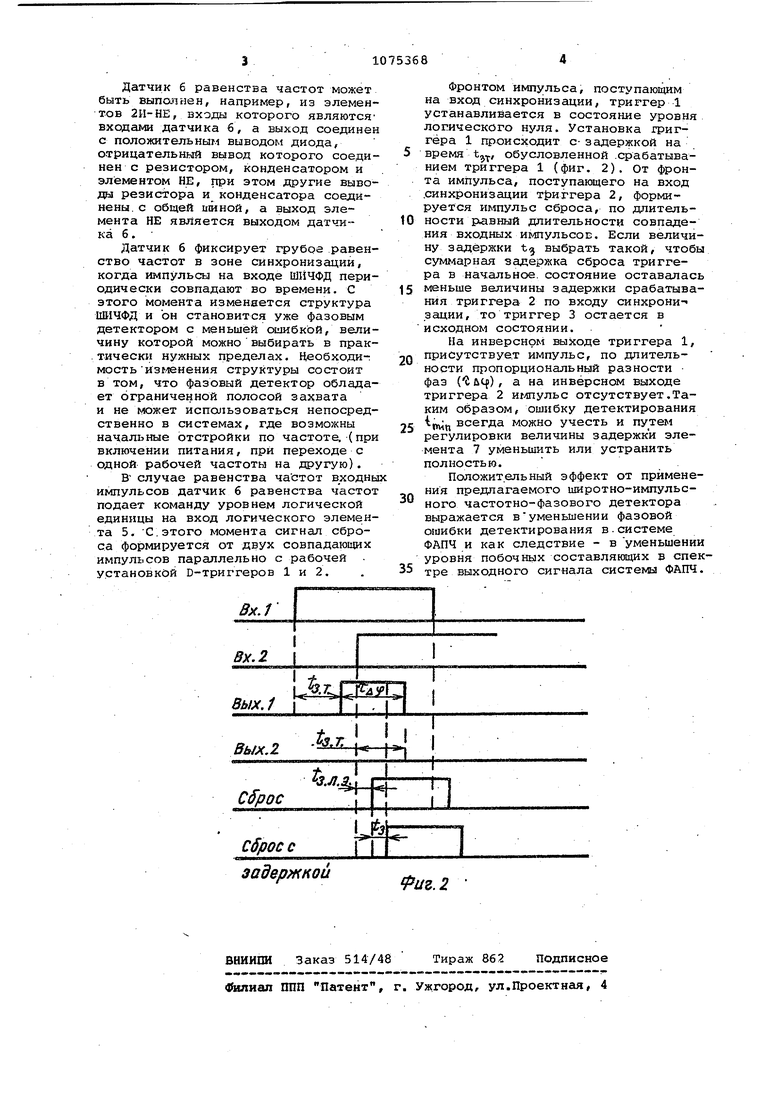

vl ел : эо Изобретение относится к радиоте нике и предназначено для работы в радиотехнической аппаратуре в цепи фазовой автоподстройки частоты (ФА Известен импульсный -частотно-фа вый детектор, содержащий два D-три гера и интегратор,входы .которого с динены соответственн.о с вых дом первого и инверсным выходом вт рого триггеров,вход синхронизации каждого из которых соединен с одно из клемм входного сигнала и входом установки в нуль другого триггера, а- информационный вход каждого триггера соединен с инверсным выходом другого триггера l.. Недостатком данного устройства является наличие общего сброса триг гера, что приводит к неу,чтенной начальной фазовойошибку.. Наиболее близким к предложенному изобретению по технической сущности является широтно-импульсный частотн фазовый детектор, содержащий два триггера, .входы синхронизации KOTOf рых соединены с входными клеммами импульсных сигналов, а инверсные выходы - с входами первого логического- элемента 2И-НЕ, выход которого соединен с входом второго логическо го элемента 2И-НЕ, выходом соединен ного с входами установки в единицу триггеров, информационные входы и входы установки в нуль которых соединены с общей юиной . Недостатком известного устройства является наличие начальной ошибки детектирования, величина которой изменяется от разброса параметров элементов схемы по быстродействию. Ошибка детектирования приводит к фазовой ошибке в системе ФАПЧ, дл компенсации которой вырабатывается компенсируквдий импульс на противоположном выходе регулирования. Всле ствие этого увеличивается уровень пульсации В управляющем напряжеНИИ системьл ОЛПЧ и, таким образом, увеличивается уровень побочных сортавляющих в спектре выходного сигнала. Целью изобретения является умень шение фазовой ошибки детектирова. ния.. С этой целью в широтно-импульсный частотно-фазовый детектор, содержащий два D-трйггера, входы синхронизации которых соединены с клеммаьш входных импульсных сигналов, информационные входы и входы установки в нуль - с общей шиной, а также первый и второй логические элементы 2И-НЕ, причем входы перBqjo логического элемента 2И-НЕ сое динены с инверсными выходами тригге ров, а один из входов второго логического элемента 2И-НЕ соединен с выходом первого логического элемента 2И-НЕ, введены датчик равенства частот, элемент задержки и логический элемент ЗИ-НЕ, два входа которого соединены соответственно с входами синхронизации обоих триггеров,входы датчика равенства частот соединены с прямыми выходами триггеров, а его выход - с третьим входом логического элемента ЗИ-НЕ, выход которого соединен с вторым входом второго логического элемента 2И-НЕ, вход элемента задержки соединен с выходом второго логического элемента 2И-НЕ, а выход - с вxoдa 1и установки в единицу три г геров. На фиг. 1 представлена блок-схема детектора; на фиг. 2 - временные диаграммы работы ишротно-импульсного частотно-фазового детектора. Широтно-импульсный частотно-фазовый детектор (С1ИЧФД) содержит D-триг.геры 1 и 2, первый и второй логические элементы 2И-НЕ 3 и 4, логический элемент ЗИ-НЕ 5, датчик 6 равенства частот и элемент 7 задержки. В широтно-импульсном частотнофазовом детекторе входы синхронизации D-триггеров 1 и 2 соединены с клеммакм ех.одных сигналов. Входы . установки в нуль и информационные D-триггеров 1 и 2 соединены с общей шиной, а входы установки в СИНИЦУ D-триггеров 1 и 2 соединены с выходом элемента 7 задержки. Прямьле выходы D-триггеров 1 и 2 соединены с входами датчика б равенства частот, выход которого соединен с одним из входов логического элемента ЗИ-НЕ 5, другие входы которого соединены с входами синхронизации D-триггеров 1 и 2. Инверсные выходы D-триггеров 1 и 2 соединены с входами логического элемента 2И-НЕ 3, выход которого соединен с одним из входов логического элемента 2И-НЕ 4, второй вход котс5рого соединен с выходом логического элемента ЗИ-НЕ 5, а выход - с входом элемента 7 задерхски. Устройство работает следующим образом. При поступлении последовательности входных импульсов на клеммы входных сигналов на инверсных выходах D-триггеров 1 и 2 формируется импульсная последовательность, ширина импульсов в которой зависит от величины разности фаз сигналов, поступающих на входы синхронизации триггеров 1 и 2. В случае большой разности частот сигналов, поступающих не вход синхронизации, датчик 6 равенства частот имеет на выходе уровень логического нуля.

Датчик 6 равенства частот может быть выполнен, например, из элементов 2И-НЕ, входы которого являются входами датчика 6, а выход соединен с положительным выводом диода, отрицательный вывод которого соединен с резистором, конденсатором и элементом НЕ, при этом другие выводы резистора и конденсатора соединены, с общей ишной, а выход элемента НЕ является выходом датчика б .

Датчик 6 фиксирует грубое равенство частот в зоне синхронизации, когда импульсы на входе ШИЧФД периодически совпадают во времени. С этого момента изменнется структура Ш1ЧФД и он становится уже фазовым детектором с меньшей ошибкой, величину которой можно выбирать в прак,тически нужных пределах. Необходи-г мостьизменения структуры состоит в том, что фазовый детектор обладает ограниченной полосой захвата и не {«зукет использоваться непосредственно в системах, где возможны начальные отстройки по частоте, (при включении питания, при переходе с одной рабочей частоты на другую).

В случае равенства частот входны импульсов датчик 6 равенства частот подает команду уровнем логической единицы на вход логического элемента 5. С.этого момента сигнал сброса формируется от двух совпадающих импульсов параллельно с рабочей . установкой D-триггеров 1 и 2.

Фронтом импульса, поступающим на вход синхронизации, триггер 1 устанавливается в состояние уровня логического нуля. Установка григгёра 1 происходит с-задержкой на время tj, обусловленной .срабатыванием триггера 1 (фиг. 2). От фронта импульса, поступающего на вход .синхронизации т иггера 2, формируется импульс сброса, по длитель0ности равный длительности совпадения входных импульсоЕ. Если величину задержки t выбрать такой, чтобы суммарная задержка сброса триггера в начальное, состояние оставалась

5 меньше величины задержки срабатывания триггера 2 по входу синхрони-задии, то триггер 3 остается в исходном состоянии.

На инверсном выходе триггера 1, присутствует импульс, по длитель0ности пропорциональный разности фаз Ci ЛЦ|) , а на инверсном выходе триггера 2 иютульс отсутствует.Таким образом, ошибку детектирования

5 всегда можно учесть и путем регулировки величины задержки элемента 7 уменьшить или устранить полностью.

Положит.ельный эффект от применения предлагаемого широтно-импульс0ного частотно-фазового детектора выражается вуменьшении фазовой ошибки детектирования в.системе ФАПЧ и как следствие - в уменьшении уровня побочных составляющих в спек5 тре выходного сигнала системы ФАПЧ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вибрационный источник сейсмических сигналов | 1983 |

|

SU1138772A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1686681A1 |

| Устройство сравнения частот и фаз | 1983 |

|

SU1171971A1 |

| Устройство управления вибрационным источником сейсмических сигналов | 1977 |

|

SU661460A1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ВРАЩАЮЩЕГОСЯ РЕАКТИВНОГО СНАРЯДА | 1997 |

|

RU2122175C1 |

| Устройство для управления трехфазным инвертором | 1984 |

|

SU1354365A1 |

WHPOTHO-ИМПУЛЬСНЫЙ ЧАСТОТНОФАЗОВГЛЙДЕТЕ1СТОР, содержащий два D-трйггера, входы синхронизации которых соед11нены с клеммами входных импульсных сигналов, информационные входы и входы установки в нуль - с общей шиноП, а тйкже первой и второй логические элементы 2И-НЕ, причем входы первого логического элемента 2И-НЕ соединеньл с инверсными выходами триггеров, из входов второго логического элемента 2W-HE соединен с выходом первого логического элемента 2И-НЕ, отличаюЧцийся тем, что, с целью уменьшения ошибки детектирования, в него введены датчик равенства частот, элемент задержки и логический элемент ЗИ-НЕ, два входы которого соединены соответственно с входами синхронизации обоих триггеров, входы датчика равенства частот соединены с прямылш выходами триггеров, а его выход - с третьим входом логичед кого элемента ЗИ-НЕ, выход которого соединен с вторым входом второго логического элемента 2И-НЕ, вход элемента задержки соединен с выходом щ второго логического элемента 2И-НЕ, (Л а выход - с входами установки в единицу триггеров.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-02-23—Публикация

1982-01-29—Подача