Изобретение относится к радиотехнике и может быть использовано в устройствах автоподстройки частоты и фазы, синтезаторах частот в устройствах цифровой обработки сигналов, синхронных демрдуляторах фазовой и частотной манипуляции для определения синфазного состояния сигналов 4

Цель изобретения - уменьшение времени определения знака частотно- фазового рассогласования.

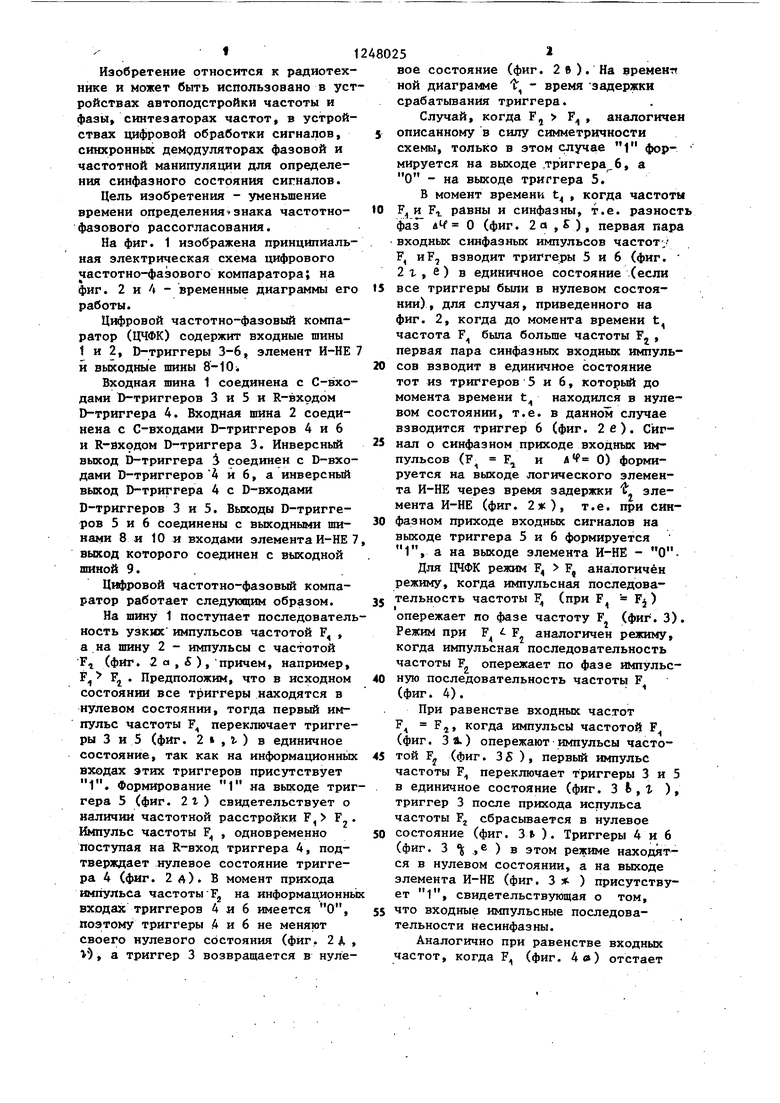

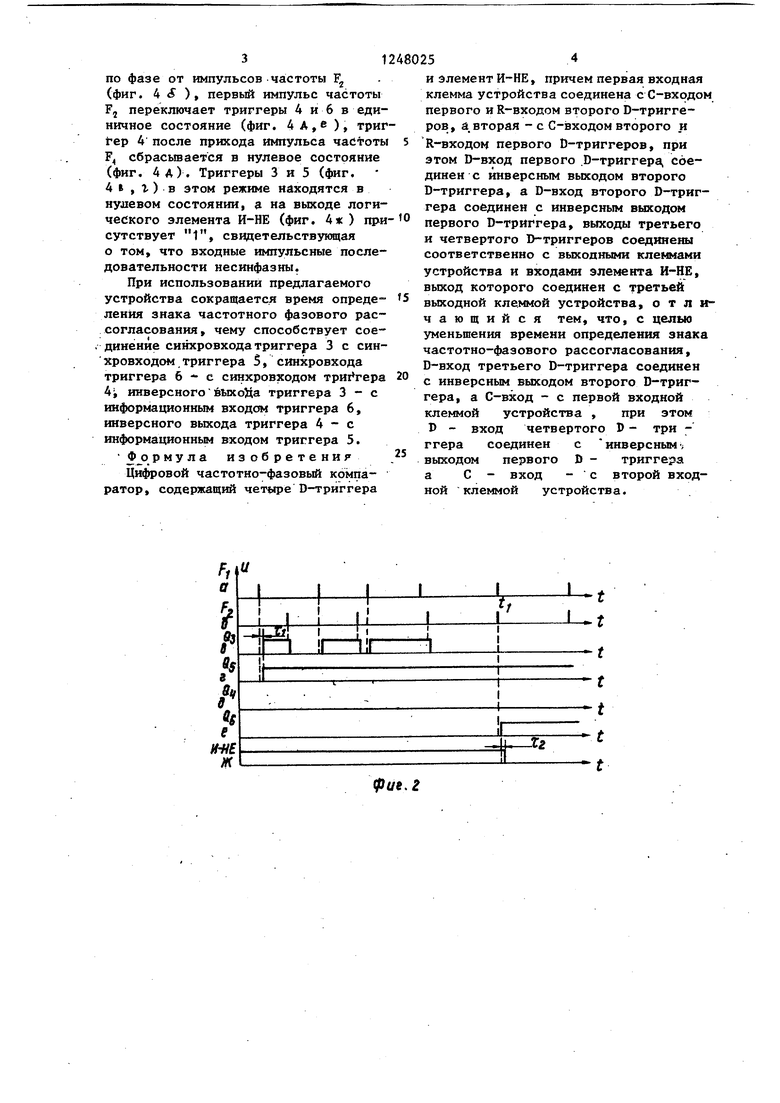

На фиг. 1 изображена принципиальная электрическая схема цифрового частотно-фазового компаратора; на фиг. 2 и 4 - временные диаграммы его работы.

Цифровой частотно-фазовый компаратор (ЦЧФК) содержит входные шины 1 и 2, D-триггеры 3-6, элемент И-НЕ и выходные шины 8-10

Входная шина 1 соединена с С-вхо- дами D-триггеров 3 и 5 и R-входом D-триггера 4. Входная шина 2 соединена с С-входами D-триггеров 4 и 6 и R-входом D-триггера 3. Инверсный выход D-триггера i соединен с D-BXO- дами D-триггеров 4 и 6, а инверсный выход D-TpHTTepa 4 с D-входами

D-триггеров 3 и 5. Выходы D-триггеров 5 и 6 соединены с выходными шинами 8 и 10 и входами элемента И-НЕ выход которого соединен с выходной шиной 9. .

Цифровой частотно-фазовый компаратор работает следующим образом.

На шину 1 поступает последователность узких импульсов частотой F , а на шину 2 - импульсы с частотой F (фиг. 2 а,5), причем, например.

F,

Fj . Предположим, что в исходном

состоянии все триггеры находятся в нулевом состоянии, тогда первый импульс частоты F переключает триггеры 3 и 5 (фиг. 2 , г. ) в единичное состояние, так как на информационньсс входах этих триггеров присутствует 1. Формирование 1 на вьрсоде триггера 5 (фиг. 21) свидетельствует о наличии частотной расстройки F F . Импульс частоты F , одновременно поступая на К-вход триггера 4, подтверждает нулевое состояние триггера 4 (фиг. 2 А). В момент прихода импульса частоты Fj на информационньЬ входах триггеров 4 и 6 имеется О, поэтому триггеры 4 и 6 не меняют своего нулевого состояния (фиг. 2А , ), а триггер 3 возвращается в нуле

5

0

вое состояние (фиг. 2 в ). На временгт ной диаграмме t, - время задержки срабатывания триггера.

Случай, когда F, F , аналогичен описанному в силу симметричности схемы, только в этом случае 1 формируется на выходе .триггера.6, а О - на выходе триггера 5.

В момент времени t , когда частоты

F и F равны и синфазны, т.е. разность фаз 44 О (фиг. 2 а ,S), первая пара входных синфазньк импульсов частот-, F nF, взводит триггеры 5 и 6 (фиг. 2 г, 6) в единичное состояние (если все триггеры были в нулевом состоянии) , для случая, приведенного на фиг. 2, когда до момента времени t, частота F была больше частоты F , первая пара синфазных входных импульсов взводит в единичное состояние тот из триггеров 5 и 6, который до момента времени t находился в нулевом состоянии, т.е. в данном случае взводится триггер 6 (фиг. 2е). Сйг5 нал о синфазном приходе входных импульсов (F FT 0) формируется на выходе логического элемента И-НЕ через время задержки t элемента И-НЕ (фиг. 2 ж), т.е. при син0 фазном приходе входных сигналов на выходе триггера 5 и 6 формируется 1, а на выходе элемента И-НЕ - ЦЧФК режим F F, аналогичен режиму, когда импульсная последова5 тельность частоты F (при F Fj)

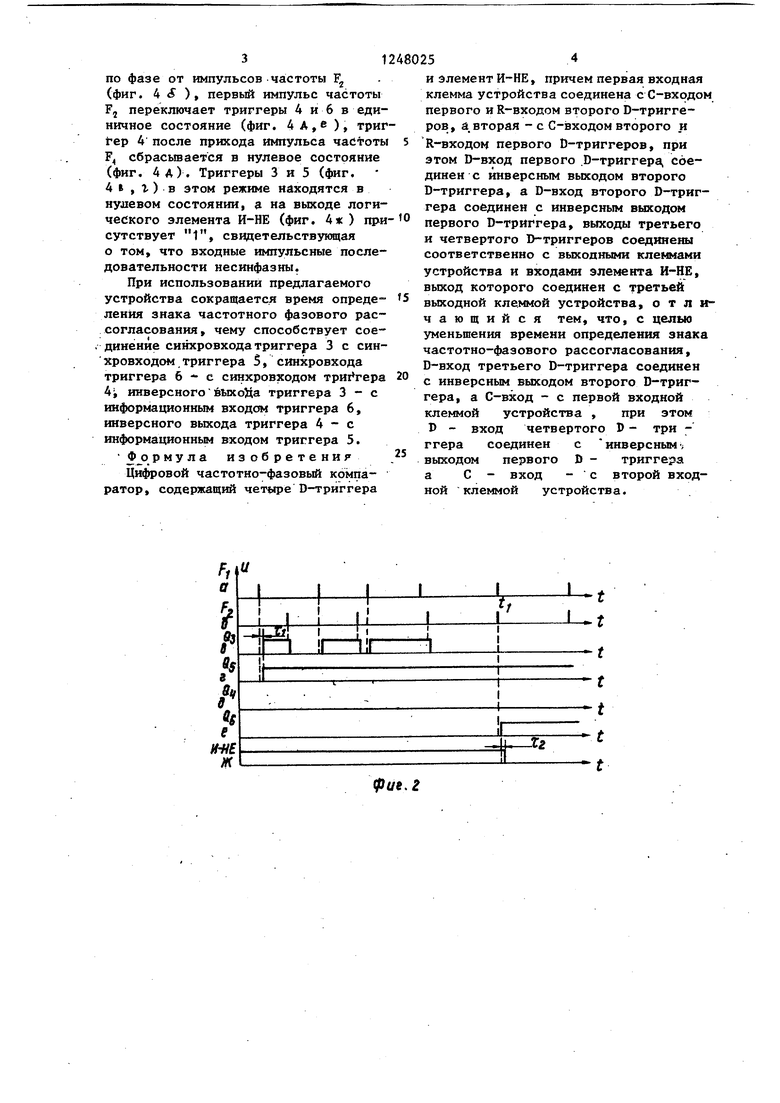

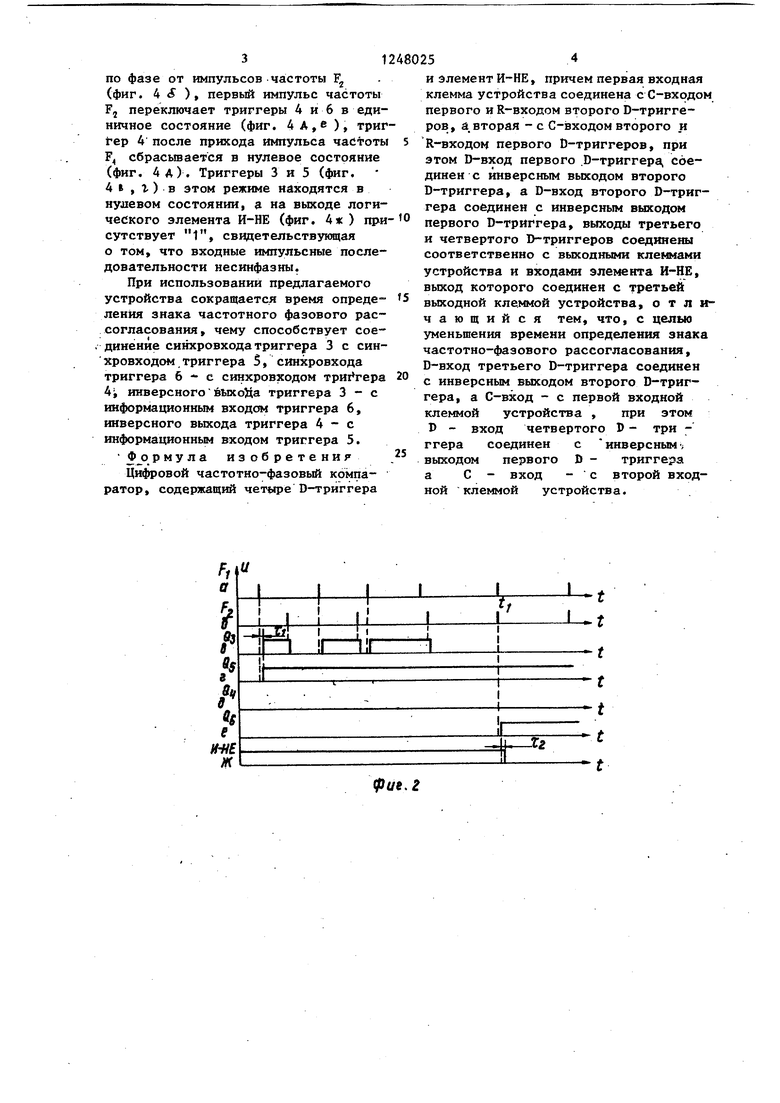

опережает по фазе частоту F (фиг. 3). Режим при F i Fj аналогичен режиму, когда импульсная последовательность частоты F опережает по фазе импульс- 0 ную последовательность частоты F (фиг. 4).

При равенстве входных частот F Fj, когда импульсы частотой F (фиг. 3 51.) опережают импульсы часто5 той FJ (фиг .35), первый импульс частоты F переключает триггеры 3 и 5 в единичное состояние (фиг. 3 S,l ), триггер 3 после прихода испульса частоты Fj сбрасывается в нулевое

0 состояние (фиг. 3t ). Триггеры 4 и 6 (фиг. 3 J( ,е ) в этом режиме находятся в нулевом состоянии, а на выходе элемента И-НЕ (фиг. 3 ) присутствует 1, свидетельствующая о том,

5 что входные импульсные последовательности несинфазны.

Аналогично при равенстве входных частот, когда F. (фиг. 4) отстает

по фазе от импульсов частоты F (фиг. 4 ), первый импульс частоты FJ переключает триггеры 4 и 6 в единичное состояние (фиг. 4А,е ), триггер 4 после прихода импульса частоты Г сбрасьгоается в нулевое состояние (фиг. 4 А). Триггеры 3 и 5 (фиг. 4 , г) в этом режиме находятся в нулевом состоянии, а на выходе логического элемента И-НЕ (фиг. 4ж ) при сутствует 1, свццетельствующая о том, что входные импульсные последовательности несинфазны.

При использовании предлагаемого устройства сокращается время опреде- ленйя знака частотного фазового рассогласования t чему способствует соединение синхровхода триггера 3 с син- хровходом триггера S, синхровхода триггера 6 - с синхровходом 4i инверсного бЫхойа триггера 3-е информационным входом триггера 6, инверсного выхода триггера 4 - с информационным входом триггера 5. Ф ормула изобретения

Цифровой частотно-фазовый компаратор, содержащий четыре D-триггера

1248025

и элемент И-НЕ, причем первая входная клемма устройства соединена с С-входо первого и R-входом второго D-триггеров, а, вторая - с С-входом второго и R-входом первого D-триггеров, при этом D-вход первого .В-триггера соединен с инверсным выходом второго D-триггера, а D-вход второго D-триг- гера соединен с инверсным выходом первого D-триггера, выходы третьего и четвертого D-триггеров соединены соответственно с выходными клеммами устройства и входами элемента И-НЕ, выход которого соединен с третьей выходной клеммой устройства, отличающийся тем, что, с целью уменьшения времени определения знака частотно-фазового рассогласования, D-вход третьего D-триггера соединен с инверсным выходом второго D-триггера, а С-вход - с первой входной клеммой устройства , при этом 1 - вход четвертого D - три - ггера соединен с инверсным выходом первого D - триггера а С - вход - с второй входной клеммой устройства.

ffJui.2

(риг. 3

Редактор А. Лежнина

Составитель М. Катанова

Техред Л.Сердюкова Корректор М. Максимишинец

Заказ 4138/56

Тираж 816

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг, tf

Подписное .

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Делитель частоты | 1987 |

|

SU1533001A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

Изобретение относится к радиотехнике и может быть использовано в устройствах автопрдстройки частоты и фазы, синтезаторах частот, в устройствах цифровой обработки сигналов. синхронных демодуляторах фазовой и частотной манипуляции, для определения синфазного состояния сигналов. Цель изобретения - уменьшение времени определения знака частотно-фазового рассогласования. Устройство содержит D-триггеры 3, 4, 5 и 6, элемент И-НЕ7, входные и выходные шины. Достижению поставленной цели способствует соединение синхровхода триггера 6 с син- хровходом триггера 4, соединение инверсного выхода триггера 3 с информационным входом триггера 6 аналогично соединению инверсного выхода триггера 4 с информационным входом триггера 5. 4 iin. (Л Is9 4i 00 О lN9 СЛ фиг,1

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-10—Подача