(5) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения проводимости и диэлектрической проницаемости и устройство для его осуществления | 1989 |

|

SU1698824A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Двухканальная следящая система | 1983 |

|

SU1200236A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Устройство для отображения параметров импульса на экране осциллографа | 1984 |

|

SU1169011A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU739732A1 |

| Интегрирующий преобразователь постоянного напряжения в код | 1988 |

|

SU1672565A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

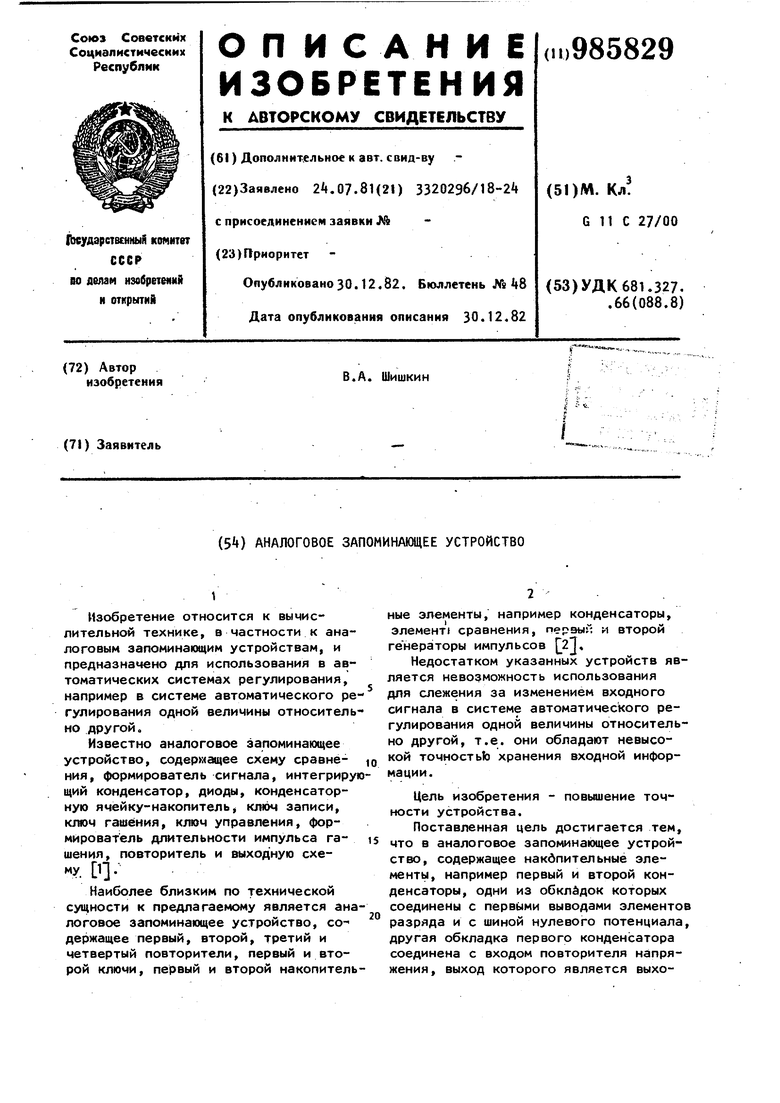

Изобретение относится к вычислительной технике, в частности к аналоговым запоминакмцим устройствам, и предназначено для использования в автоматических системах регулирования, например в системе автоматического ре гулирования одной величины относитель но другой. Известно аналоговое запоминающее устройство, содержащее схему сравнения, формирователь сигнала, интегриру щий конденсатор, диоды, конденсаторную ячейку-накопитель, ключ записи, ключ гашения, ключ управления, формирователь длительности импульса гашения, повторитель и выходную схему. 1. Наиболее близким по технической сущности к предлагаемому является ана логовое запоминающее устройство, содержащее первый, второй, третий и четвертый повторители, первый и второй ключи, первый и второй накопитель ные элементы, например конденсаторы, элемент сравнения, перэыГ1 и второй генераторы импульсов 2| Недостатком указанных устройств является невозможность использования для слежения за изменением входного сигнала в системе автоматического регулирования одной величины относительно другой, т.е. они обладают невысокой точностьЬ хранения входной информации. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее накбпительные элементы, например первый и второй конденсаторы, одни из обклдДОК КОТОРЫХ соединены с первыми выводами элементов разряда и с шиной нулевого потенциала, другая обкладка первого конденсатора соединена с входом повторителя напряжения, выход которого является выхо398jqoM устройства, первый блок сравнения первый и второй ключи, введены последовательно соединенные преобразователь напряжение-напряжение, интегратор, сумматор, третий ключ, источник опорного напряжения, инвертор, четвер тый, пятый, шестой, седьмой, восьмой и девятый ключи, разделительные элементы, второй блок сравнения, последо вательно соединенные элемент ИЛИ, фор мирователь импульсов и триггер, причем вход преобразователя напряжениенапряжение является входом устройства , выход преобразователя напряжениенапряжение дополнительно соединен соответственно через первый и второй разделительные элементы с первым входом элемента ИЛИ и с входом инвертора, выход которого соединен с вторым входом элемента ИЛИ и с первыми входами первого и второго ключей, выходы которых соединены с входами первого блока сравнения, выход первого блока сравнения соединен с первыми входами четвертого и пятого ключей, выходы которых соединены с шиной нулевого потенциала, выход третьего ключа соединен через третий разделительный элемент с вторым входом второго ключа и через четвертый разделительный элемент с вторым входом первого ключа и с входом повторителя напряжения, второй .вход третьего ключа соединен с выходом элемента ИЛИ, второй вход четвертого ключа соединен с вторым выводом первого элемента ра ряда, с другой обкладкой первого кон денсатора , с первым входом шестого ключа и через пятый разделительный элемент с выходом девятого ключа, первый вход которого соединен с первым входом восьмого ключа и с первым выходом источника опорного напряжения, второй выход которого соединен с вторым входом сумматора, второй, вход девятого ключа соединен с первы выходом второго блока сравнения, вхо ды которого соединены соответственно с выходами шестого и седьмого ключей второй вывод второго элемента разря да соединен с вторым входом пятого ключа и с первым входом седьмого ключа и через шестой разделительный элемент с выходом восьмого ключа, второй вход которого соединен с вторым выходом второго блока сравнения, выход триггера соединен с вторыми входами шестого и седьмого ключей. выход третьего ключа соединен через седьмой разделительный элемент с вторым входом пятого ключа, третьи выводы первого и вторбго элементов разряда соединены с первым выходом источника опорного напряжения На фиг, 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - эпюры напряжений на входах и выходах элементов устройства Предлагаемое устройство (фиг 1) содержит накопительные элементы, например первый и второй конденсаторы 1 и 2, преобразователь 3 напряжение- . напряжение, интегратор , сумматор 5 инвертор 6, элемент ИЛИ 7, формирователь 8 импульсов, источник 9 опорного напряжения, триггер 10, повторитель 11 напряжения, блоки 12 и 13 сравнения, шину нулевого потенциала, ключи 15-23 разделительные элементы 2430 и элементы 31 и 32 разряда Устройство функционирует следующим образом. Преобразователь 3 преобразует входной сигнал меняющейся величины положительной или отрицательной полярности (фиго 2, эпюра 2 аУ соответственно в импульс напряжения положительной или отрицательной полярности постоянной амплитуды, причем передний фронт импульса совпадает с моментом появления входного сигнала, а задний фронт - с моментом его изменения до нулевого уровня (фиг. 2, эпюра В). Интегратор 4 выдает на сумматор 5 линейно изменяющееся напряжение (фиг, 2, эпюра г), в котором оно складывается с опорным напряжением источника 9 (фиг. 2, эпюра 3). Источник 9 опорных напряжений служит для задания номинального уровня выходного напряжения устройства в номинальном режиме работы (фиг, 2, эпюра 5 ), а также для выдачи напряжения запирания на элементах 31 и 32 разряда и напряжения на подзаряд конденсаторов 1 и 2. Ключ 17 открывается преобразованным входным сигналом как положительной, так и отрицательной полярности, и закрывается в моменты изменения входного сигнала до нуля. Сигнал управления поступает на ключ 17 с выхода элемента 7, на один из входов которого подается отрицательный сигнал с преобразователя 3 через разделительный элемент 25 и инвертор 6, на другой его вход подается отрицательный сигнал с преобразователя 3 через разделительный элемент 2. Ключи 15 и 16, схема сравнения 12, разрядные ключи 18 и 13 образуют узел подзаряда. Ключи 15 и 16 открываются преобразованным и инвертируемым входным сигналом отрицательной полярности. На эти ключи сигнал управления поступает с инвертора 6. Блок 12 сравнения вырабатывает сиг нал (фиг. 2, эпюра К), открывающий ключи 18 и 19, при поступлении на его входы через открытые ключи 15 и 16 на пряжений с конденсатора 1 и с выхода ключа 17 через разделительный элемент 26. Сигнал вырабатывается только при величине напряжения на конденсато ре 1, большей величины напряжения на выходе ключа 17. В этом случае про- исходит подзаряд конденсаторов 1 и 2 через открытые ключи 18 и 19 (фиг.2, эпюры 9 ив),. Ключи 20 и 21, блок 13 сравнения, ключи подзаряда 22 и 23, разделительные элементы 28 и 29 образуют узел подзарядао Сигнал управления ключами 20 и 21 формируется с помощью формирователя 8 и триггера 10, который выдает сигнал управления в момент времени, совпадающий с задним фронтом импульса преобразователя 3, поступающего на формирователь 8 с элемента ИЛИ 7 (фиг.2, эпюра Ж.), В момент, совпадающий с передним фронтом импульса преобразователя 3 триггер 10 перебрасывается в исходное (нулевое) положение. I Напряжения с конденсаторов 1 и 2 подаются на входы блока 13 сравнения, выходной сигнал которого открывает ключ 23 при напряжении на конденсаторе 1, большем напряжения на конденсаторе 2, или ключ 22 при напряжении на конденсаторе 1, меньшем напряжения на конденсаторе 2 (фиг. 2, эпюра Ц) . Происходит быстрый подзаряд конденса тора 1 или конденсатора 2 от напряжения источника 9 через разделительный элемент 28 или 29 (фиг. 2, эпюры о , е ). Как только величины напряжений на конденсаторах сравняются, ключи 23 и 22 закрываются. Элементы 31 и 32 образуют цепи раз ряда конденсаторов 1 и 2 при выключении питания Элементы 31 и 32 закрыты при включении напряжения питания и открыты при его выключении. Устройство работает в режимах, приведенных в, таблице, в которой также приводится состояние ключей и величины входных и выходных напряжений для различных режимов. При включении (подаче питающих напряжений) и положительном входном сигнале преобразователь 3 формирует импульс положительной полярности, который поступает на интегратор k. С выхода интегратора 4 на один из входов сумматора 5 поступает линейно нарастающее напряжение Напряжение с источника 9 опорных напряжений поступает на другой вход сумматора 5, и через открытый ключ 17 и разделительные элементы 27 и 30 происходит заряд конденсаторов 1 и 2 суммарным напряжением сумматора 5. Заряд конденсаторов 1 и 2 протекает до тех пор, пока выходное напряжение Цру устройства не достигнет уровня, соответствующего моменту времени, когда величина входного сигнала станет равной нулю (нижние пунктирные линии на эпюрах 2 Q и 2е) , или не достигнет величины опорного напряже (номинальный режим устройства), за вычетом падения напряжения на ключе 17 и элементе 27 (средние сплошные линии на эпюрах g, б фиг, 2) , или не достигнет беличины суммарного напряжения сумматора 5 за вычетом того же падения напряжения, если на входе устройства продолжает присутствовать положительный входной сигнал , 1верхние пунктирные линии на эпюрах Если в следующий момент времени появится положительный входной СИ|- нал, то конденсаторы 1 и 2 будут подзаряжаться через ключ 17 от выходно напряжения сумматора 5 до величины и момента времени, пока входной сигнал не станет равным нулю. Напряжение с конденсатора 1 переается на выход устройства через повторитель 11, Если в следующий момент времени на входе устройства появится отрицательный входной сигнал, то напряжение на выходе ключа 17 будет меньше напряЖения на конденсаторе 1, Блок 12 сравнения вырабатывает сигнал, открывающий ключи 18 и 19, и происходит подзаряд конденсаторов 1 и 2 до тех пор, пока величина входного сигнала не станет равной нулю.

В процессе хранения информации конденсатор 1 медленно разряжается через нагрузку - входное сопротивление повторителя 11.

Чтобы сохранить величину напряжения, до которой был первоначально заряжен конденсатор 1, блок 13 сравнения вырабатывает сигнал, открывающий ключ 23,и конденсатор 1 быстро подзаряжается от напряжения, подаваемого на конденсатор 1 через элемент 28 и ключ 23 от источника 9.

Подзаряд конденсатора 1 продолжается до момента, когда напряжения на конденсаторах 1 и 2 сравняются.

Если по каким-либо причинам напряжение на конденсаторе 2 станет меньше напряжения на конденсаторе 1, то сигВыборка и запись при вклю ении и поло- 15,16,18,19,20,2 жительиом входном сиг- 22,23, 31 и 32 20, 21, 23, 22, при отрицательном 1 32 входном сигнале 17,15,16,18, Хранение (при вход19,23,22,30, ном сигнале, равном нулю) 31 15,16,17,18, Выключение 19,20,21,22, 23 Примечание. ;

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопительные элементы, например первый и второй конден;нал с блока ТЗ сравнения откроет ключ 22 и конденсатор 2 быстро подзарядится через элемент 29 от напряжения источника 9.

Подзаряд конденсатора 2 продолжается до момента сравнения напряжений на конденсаторах 1 и 2.

При выключении напряжения питания конденсаторы 1 и 2 разряжаются до нулевого уровня соответственно через элементы 31 и 32 (эпюры а,е на фиг.2),

Устройство, таким образом, обеспечивает выдачу управляющего сигнала путем сложения опорного напряжения с преобразованным входным сигналом, что значительно повышает его точность. Кроме того, повышается безопасность при ремонтных работах за счет разряда конденсаторов при выключении устройства.

саторы, одни из обкладок которых соединены с первыми выводами элементов разряда и с шиной нулевого потенциала, другая обкладка первого конденсатора соединена с входом повторителя 1. Uog- величина опорного напряжения 9. 2, t, ti tj моменты времени, причем k « 0,1,2,3. {} k + X, где X - целое мисло ( х 0) или I j + х; j I + у, где у - целое число (у О или j « k + у). 3. «енты времени t и tj наступают после t| s любой последовательности. Цч Ц|Г напряжения, хранящиеся в устройстве к моменты времени t и tj. 1 im Uat,,-.Uon , 17 t . lim U bi -Uni,, t - ti 15, 16. 18, 19 Upn Uni, «„() lira Ujfci, U,n(i) 20, 21 V - tUn(i, Uot.m(,, 31 и 32 Umu i|UTr, напряжения, выход которого является выходом устройства, первый блок срав нения, первый и второй ключи, отл чающееся тем, что, с целью повышения точности устройства, в него введены последовательно соединенные преобразователь напряжение-напря жение, интегратор, сумматор, третий ключ,источник опорного напряжения, инвертор, четвертый, пятый, шестой, седьмой, восьмой и девятый ключи, разделительные элементы, второй блок сравнения, последовательно соединенные элемент ИЛИ, формирователь импульсов и триггер, причем вход преоб разователя напряжение-напряжение является . входом устройства, вЫход преобразователя напряжение-напряжение дополнительно соединен соответственно через первый и второй разделитель ные элементы с первым входом элемента ИЛИ и с входом инвертора, выход которого соединен с вторым входом элемента ИЛИ и с первыми входами пер вого и второго ключей, выходы которы соединены с входами первого блока сравнения, выход первого блока сравнения соединен с первыми входами чет вертого и пятого ключей, выходы которых соединены с шиной нулевого потенциала, выход третьего ключа соеди нен через третий разделительный элемент с вторым входом второго ключа и через четвертый разделительный эле мент с вторым входом первого ключа и с входом повторителя напряжения, второй вход третьего ключа соединен с выходом элемента ИЛИ, второй вход четвертого ключа соединен с вторым выводом первого элемента разряда, с другой обкладкой первого конденсатора, с первым входом шестого ключа и через пятый разделительный элемент с выходом девятого ключа, первый вход ;которого соединен с первым входом ;восьмого ключа и с первым выходом ис|точника опорного напряжения, второй выход которого соединен с вторым входом сумматора, второй вход девятого ключа соединен с первым выходом второго блока сравнения, входы которого соединены соответственно с выходами шестого и седьмого ключей, второй вывод второго элемента разряда соединен с вторым входом пятого ключаре другой обкладкой второго конденсатора и с первым входом седьмого ключа,и через шестой разделительный элемент с выходом восьмого ключа, второй вход которого соединен с вторым выходом второго блока сравнения, выход триггера соединен с вторыми входами шестого и седьмого ключей, выход третьего ключа соединен через седьмой разделительный элемент с вторым входом пятого ключа, третьи выводы первого и второго элементов разряда соединены с первым выходом источника опорного напряжения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 589622, кл, G 11 С 27/00, 1977. 2,Авторское свидетельство СССР № , кл. q 11 С 27/00, 1973 (прототип.

«;

s

т Ш

Авторы

Даты

1982-12-30—Публикация

1981-07-24—Подача