фиг.

Изобретение относится к импульсной технике и предназначено для кодопреобразования в цифровых системах передачи данных, оборудованных регенераторами пятиуровневого сигнала.

Известен преобразователь двоичного сигнала в балансный пятиуровневый сигнал, содержащий конвертер, реверсивный счетчик, два блока задержки, формирователь, дешифратор и блок балансировки С1 3.

Однако этот преобразовательгромоздок, так как не позволяет использовать микросхемы высокой степени интеграции, а также имеет органиченное быстродействие, поскольку кодоитреобразование ведется на частоте выходного сигнала.

Наиболее близким к предлагаемому по техническому решению является преобразователь двоичного сигнала в балансньп пятиуровневый сигнал, содержащий регистр считывания, вход которого соединен с входной шиной, блок памяти, последовательно соединенные делитель частоты, -мультиплексор и инвертор, а также дешифратор состояния и дешифратор сигнала инверсии, тактовые входы регистра считывания и делителя частоты соединены с тактовой шиной, другой выход делителя частоты соединен с другими выходами регистра считывания и мультиплексора, к информационному входу которого подключен блок памяти, а дешифратор состояния через дешифратор сигнала инверсии соединен с управляющим входом инвертора С2г Недостатком этого устройства является сложность схемы балансировки выходного сигнала, так как определение знака веса пятиуровневого слова осуществляется путем анализа составляющих его символов, а для обозначекия пятиуровневого символа требуется как минимум трехразрядное двоичное слово. Кроме того, преобразователь имеет недостаточную помехозащищенность выходного сигнала, обусловленную тем, что дешифратор состояния подключан к выходу двоичного инвертора (выход преобразователя), поэтому сигнал о необходимости балансировки приходит с опозданием, и текущая цифровая сумма выходного сигнала достигает большой величины, т.е. формирует ся длинная серия однополярных символов, что вызывает большие межсимволь-

ные искажения при передаче пятиуровневого сигнала по линии, снижая тем самым надежность работы устройства. Цель изобретения - повышение на-

дежности.

Поставленная цель достигается тем, что в преобразователь двоичного сигнала в балансный пятиуровневый сигнал, содержащий регистр считывания,

вход которого соединен с входной шиной, блок памяти, последовательно соединенные делитель частоты, мультиплексор и инвертор, а также дешифратор состояния и дешифратор сигнала

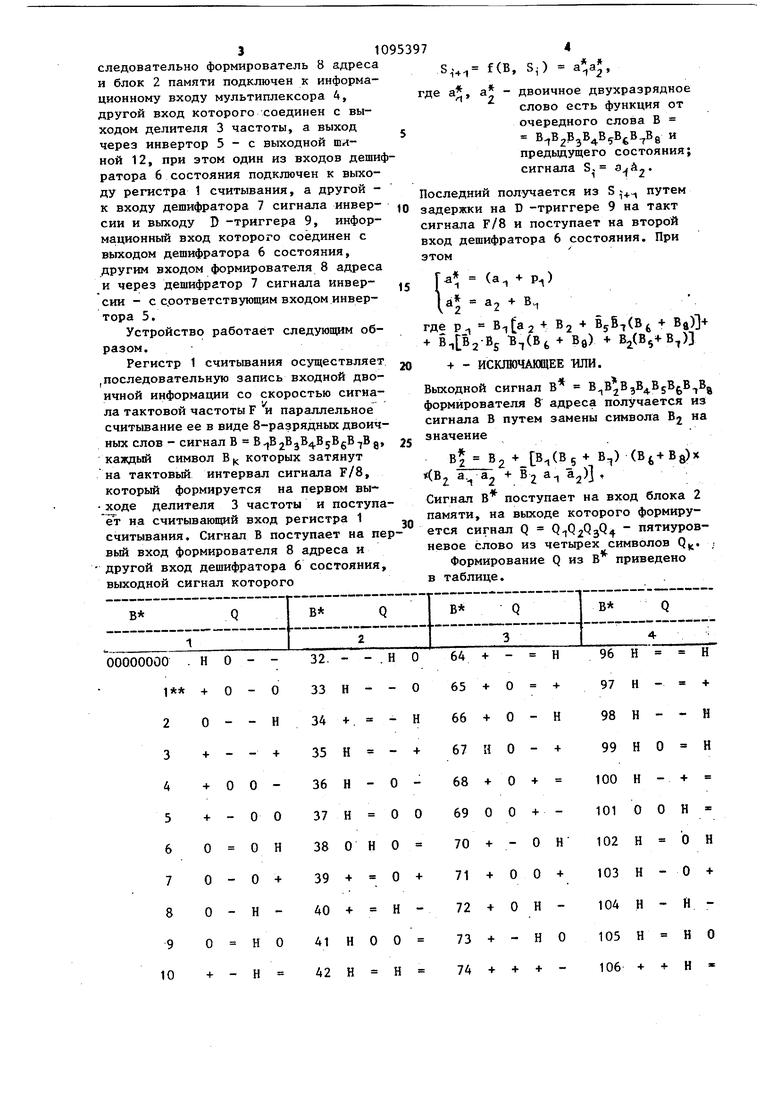

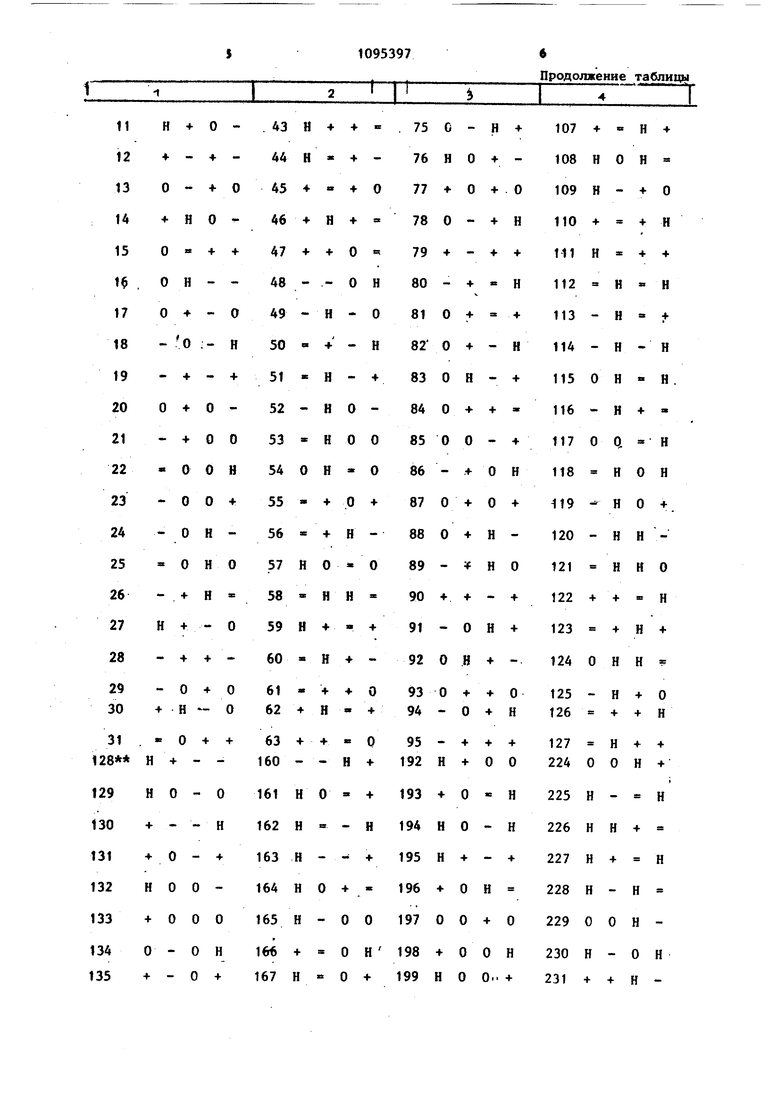

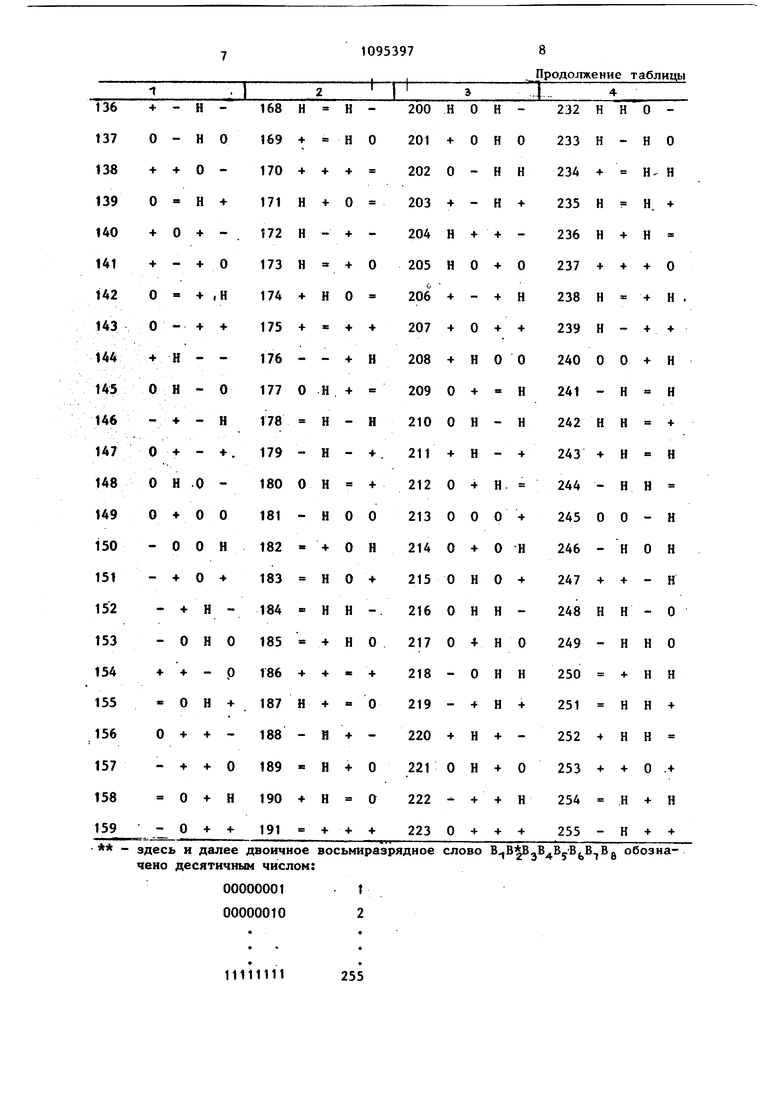

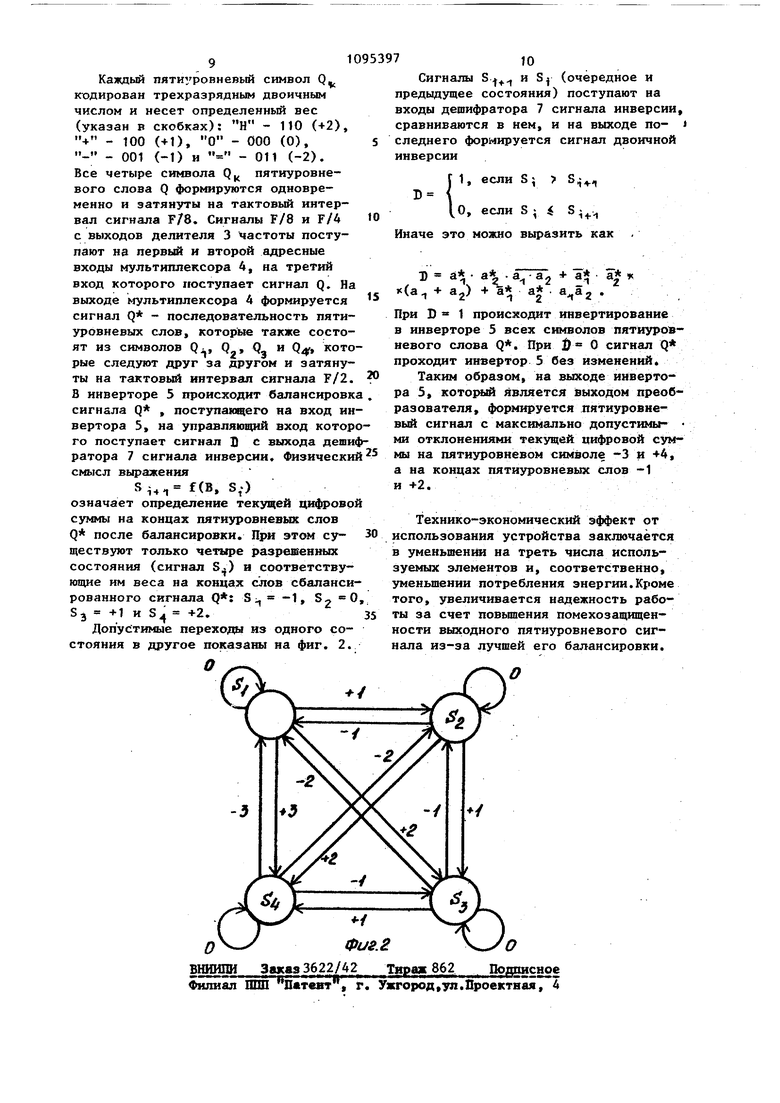

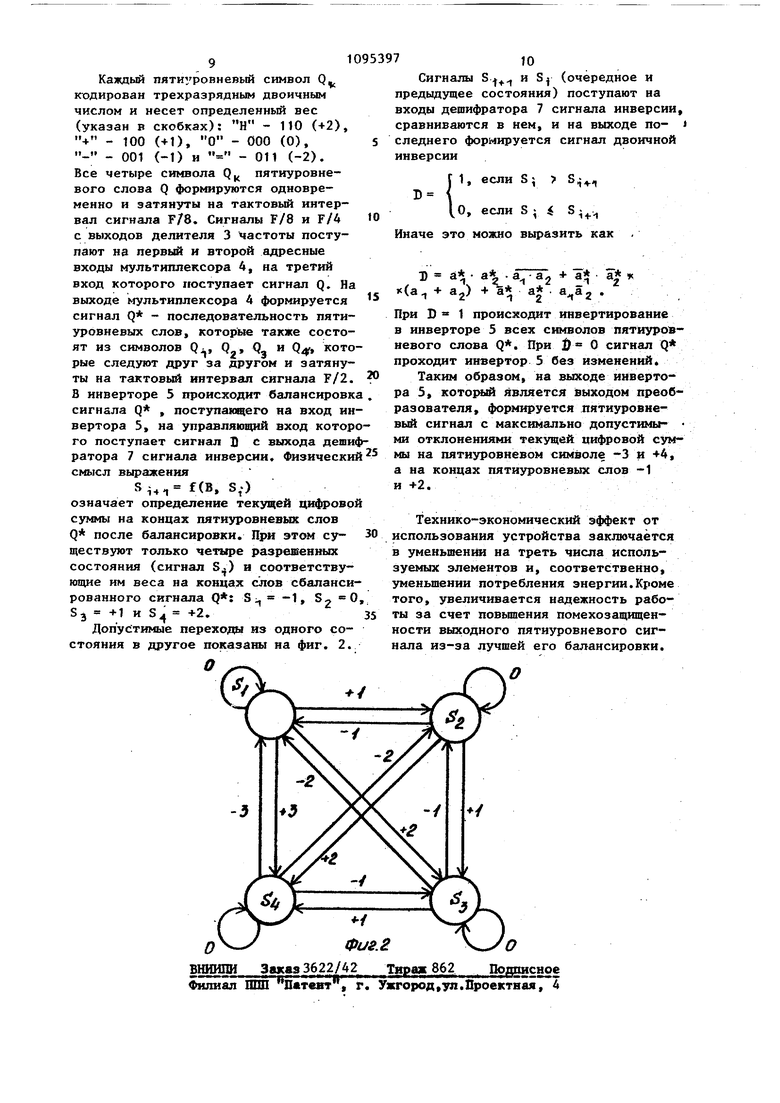

инверсии, тактовые входы регистра считывания и делителя частоты соединены с тактовой шиной, другой выход делителя частоты соединен с другими входами регистра считывания и мультиплексора, к информационному входу которого подключен блок памяти, а дешифратор состояния через дешифратор сигнала инверсии соединен с уп- равляющим входом инвертора, введены формирователь адреса и D -триггер, тактовый вход которого подключен к другому выходу делителя частоты, выход ) -триггера соединён с другим входом дешифратора сигнала инверсии и входом дешифратора состояния, другой вход которого соединен с выходом регистра считьшания и входом формирователя адреса, другой вход которого соединен с выходом дешифратора состояния и информационным входом J) -триггера, а выход подключен к входу блока памяти, причем выход инвертора подключен к выходной шине устройства. На фиг. 1 изображена функциональная схема устройства; на фиг. 2 график переходов из одного состояния в другое. Преобразователь двоичного сигнала в балансный пятиуровневый сигнал содержит регистр 1 считывания, блок 2 памяти, делитель 3 частоты, мультиплексор 4, инвертор 5, дешифратор 6 состояния, дешифратор 7 сигнала инверсии, формирователь 8 адреса и D -триггер 9, а также входную шину (вход) 10, тактовую шину 11 и выходную шину (выход) 12. Входы регистра 1 считывания подключены соответственно к входной шине 10, тактовой шине 11 и входу делителя 3 частоты, а также тактовому входу D -триггера 9, входу мультиплексора 4 и выходу делителя 3 частоты, а выход через соединенные последовательно формирователь 8 адреса и блок 2 памяти подключен к информационному входу мультиплексора 4, другой вход которого соединен с выходом делителя 3 частоты, а выход через инвертор 5 - с выходной тиной 12, при этом один из входов деши ратора 6 состояния подключен к выходу регистра 1 считывания, а другой к входу дешифратора 7 сигнала инверсии и выходу D -триггера 9, информационный вход которого соединен с выходом дешифратора 6 состояния, другим входом формирователя 8 адреса и через дешифратор 7 сигнала инверсии - с срответствующим входом инвертора 5, Устройство работает следующим образом. Регистр 1 считывания осуществляет ,последовательную запись входной двоичной информации со скоростью сигнала тактовой частоты F и параллельное считывание ее в виде 8-разрядньк двоичных слов - сигнал В каждый символ В которых затянут на тактовый интервал сигнала F/8, который формируется на первом вы ходе делителя 3 частоты и поступа ет на считывающий вход регистра 1 считывания. Сигнал В поступает на пе вый вход формирователя 8 адреса и другой вход дешифратора 6 состояния, выходной сигнал которого S,4i f(B, S,.) , слово есть функция от очередного слова В и предьщущего состояния; сигнала S, .. Последний получается из S путем задержки на D -триггере 9 на такт сигнала F/8 и поступает на второй вход дешифратора 6 состояния. При этом (а + р) а aj + В где р В-,а2 + Bj + 6567(3 + Bft)+ + § 62-85 l(Bfc BO) Bj(B5+B)3 -f - ИСКЛЮЧАЮЩЕЕ WIH. Выходной сигнал В формирователя 8 адреса получается из сигнала В путем замены символа В2 на значение ,(В5 В) () ii(B2 а.32 + 2 1 Сигнал В поступает на вход блока 2 памяти, на выходе которого формируется сигнал Q Р Р2РзР4 пятиуровневое слово из четырех символов Q. ; Формирование Q из В приведено в таблице.

Продолжение таблицы - здесь и далее двоичное восьмиразрядное чено десятичным числом: 00000001 t 00000010 2 слово B B B By-Bj B Bg обозна

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Система для телеконтроля промежуточных станций линий связи | 1987 |

|

SU1453603A1 |

| Система передачи и приема асинхронных цифровых сигналов | 1986 |

|

SU1317674A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО СИГНАЛА В БАЛАНСНЫЙ ПЯТИУРОВНЕВЫЙ СИГНАЛ, содержащий регистр считывания, вход которого соединен с входной шиной, блок памяти, последовательно соединенные делитель частоты, мультиплексор и инвертор, а также дешифратор состояния и дешифратор сигнала инверсии, тактовые входы регистра считывания и делителя частоты соединеныс тактовой шиной, другой выход делителя частоты соединен с другими входами регистра считывания и мультиплексора, к информационному входу которого подключен блок памяти, а дешифратор состояния через дешифратор сигнала инверсии соединен с управляющим входом инвертора, отличающийся тем что, с целью повы шения надежности, введены формирователь адреса и Т) -триггер, тактовый, вход которого подключен к другому выходу делителя частоты, выход 9 триггера соединен с другим входом дешифратора сигнала инверсии и входом дешифратора состояния, другой вход которого соединен с выходом регистра считьшания и входом формирователя адреса, другой вход которого соединен с выходом дешифратора состояния и информационным входом D -триггера, а выход подключен к входу блока памяти, причем выход .инвертора подключен к выходной шине устройства. D J :л :с :о /г

11111111 255

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-05-30—Публикация

1983-02-24—Подача