(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1986 |

|

SU1397903A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1984 |

|

SU1256019A1 |

| Устройство для деления | 1985 |

|

SU1291973A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

Изобретение относится к вычислительной технике, и может быть использовано, в частности, в арифметических устройствах цифровых и комбинированных вычислительных машин.

По основному авт. св. W 710040 известно устройство, содержащее регистр делимого, регистр делителя, матрицу умножения и сумматор, причем п выходов регистра делителя подключеМы соответственно к первым п входам матрицы умножения, первые п вхо-дов сумматора подключены к соответствующим п выходам регистра делимого , вторые п входов сумматора подключены к соответствующим п выходам матрицы умножения, а п выходов сумматора подключены соответственно к вторым п входам матрицы умножёния 1.

Недостатком этого устройства является низкая точность, обусловленная неустойчивой работой при различных допустимых комбинациях делимого и делителя.

Целью изобретения является повышение точности устройства.

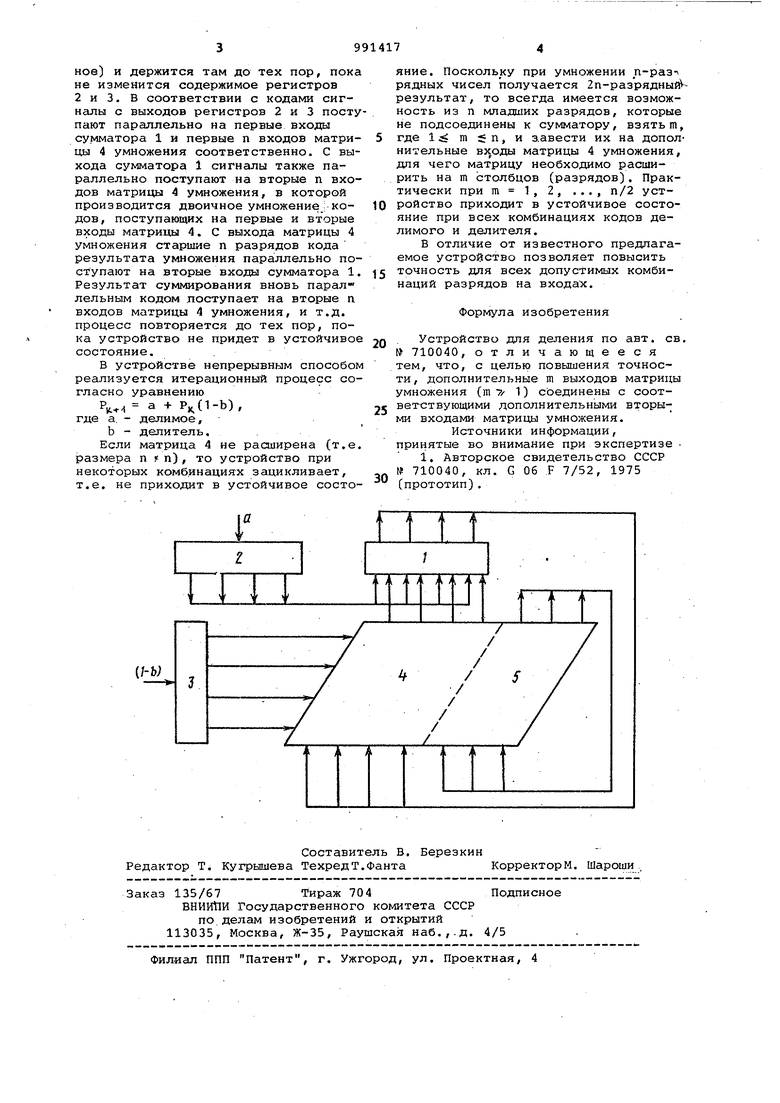

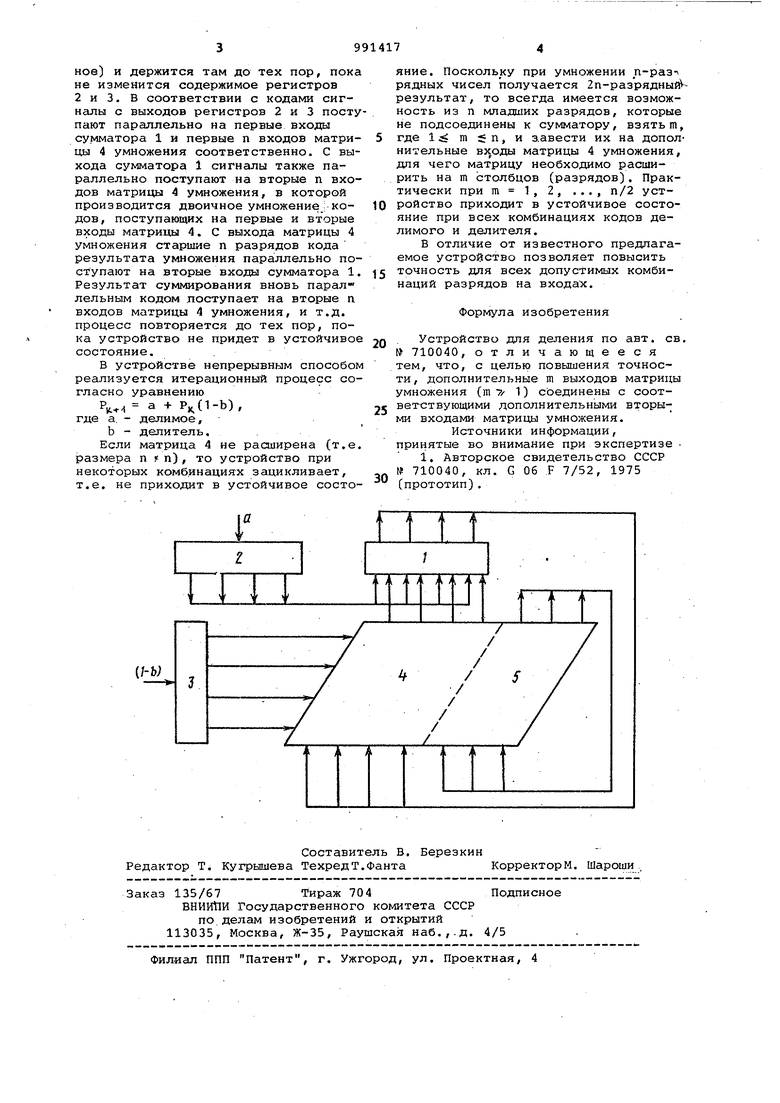

Для достижения поставленной цели в устройстве для деления дополнительные m выходов матрицы умножения (т 7/1) соединены с срответствующими

дополнительными вторыми входами матРИДЫ умножения.

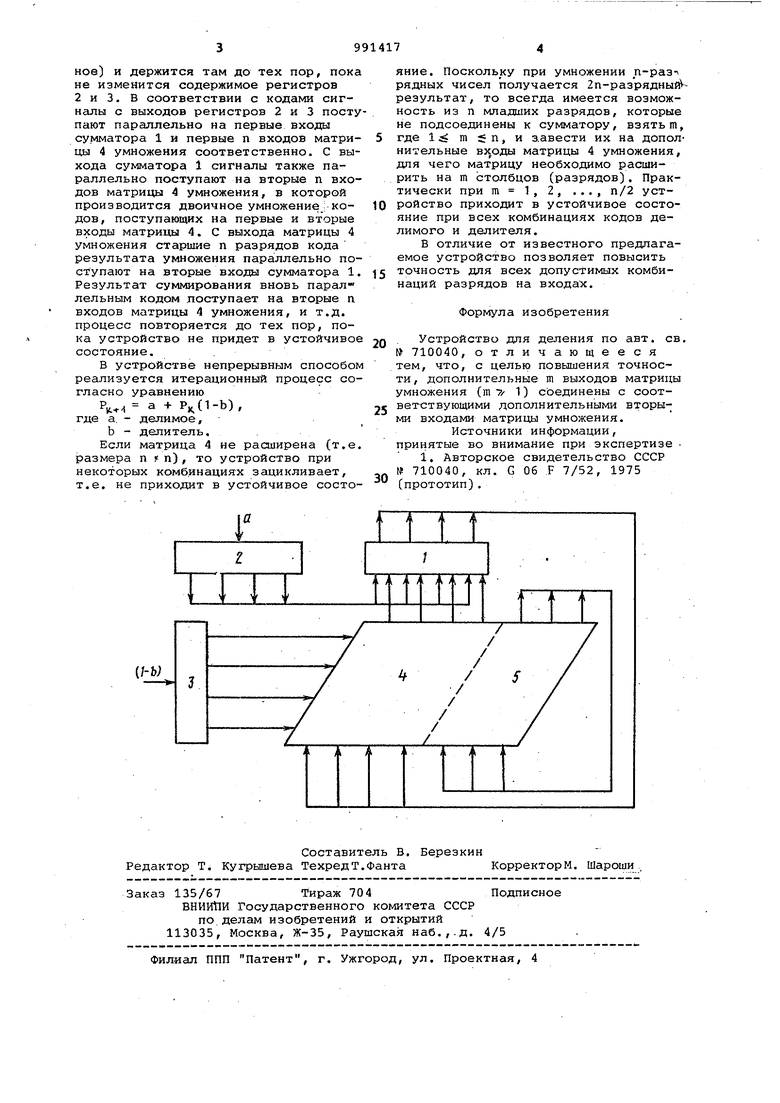

На чертеже показана структурная схема предлагаемого устройства для деления.

Устройство для деления содержит сумматор 1, регистр 2 делимого, регистр 3 делителя, матрицу 4 умножения, расширенную на дополнительную

10 часть 5, п выходов регистра 3 делите. ля подключены соответственно к первым п входам матрицы 4 умножения, п выходов регистра 2 делимого подкпю-. чены соответственно к п первым вхо дам сумматора 1, п выходов которого подключены соответственно к вторым п входам матрицы 4 умножения, п выходов которой подключены соответственно к вторым входам сумматора 1,

20 а m вторых входов дополнительной части 5 матрицы 4 умножения и m ее выходов соединены соответственно между собой. i

Устройство работав следующий об25разом.

Одновременно подаются на регистры 2 и 3 делимое и делитель соответственно. По истечении переходных процессов в устройстве на выходе сумма30 тора 1 формируется результат (част

Авторы

Даты

1983-01-23—Публикация

1981-07-17—Подача