Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и арифметических устройств быстродействующих цифровых и комбинированных вычислительных машин.

.Целью изобретения является увеличение быстродействия.

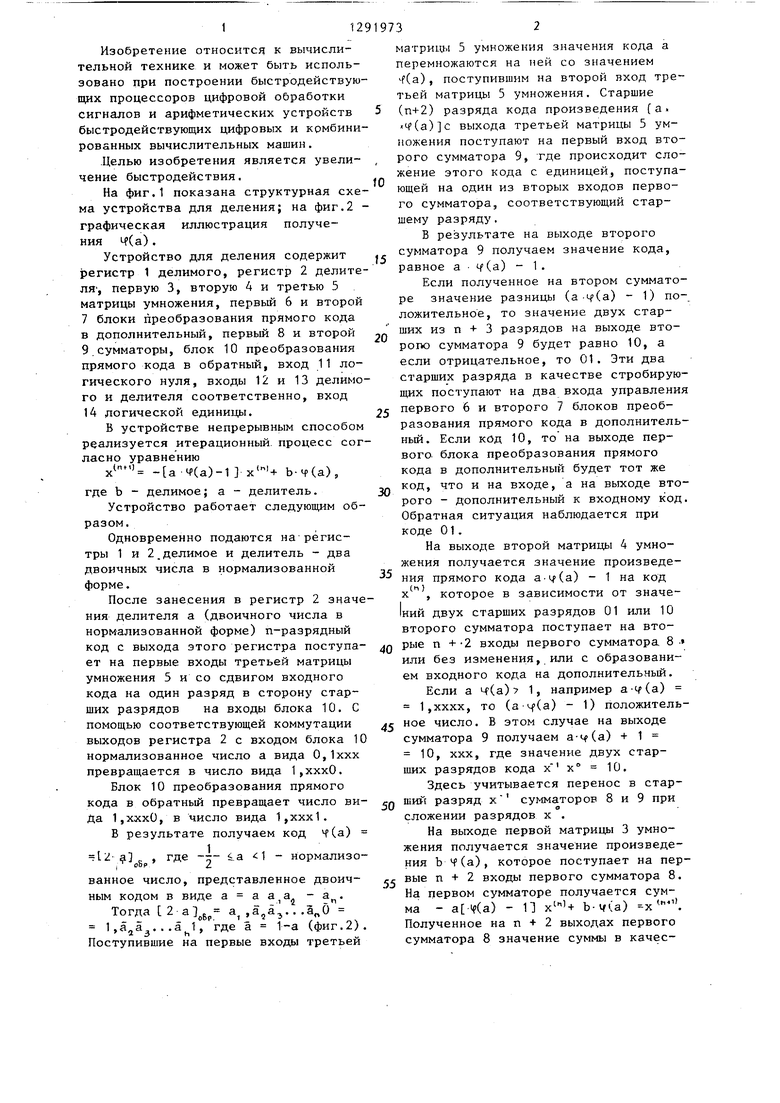

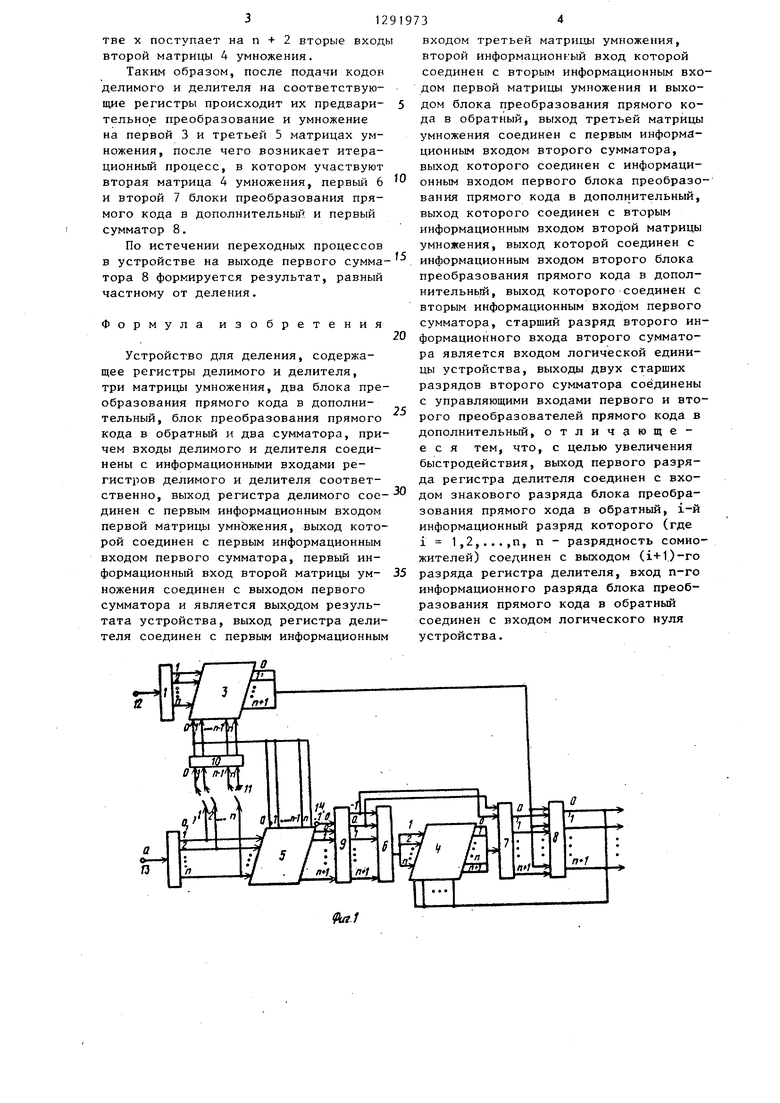

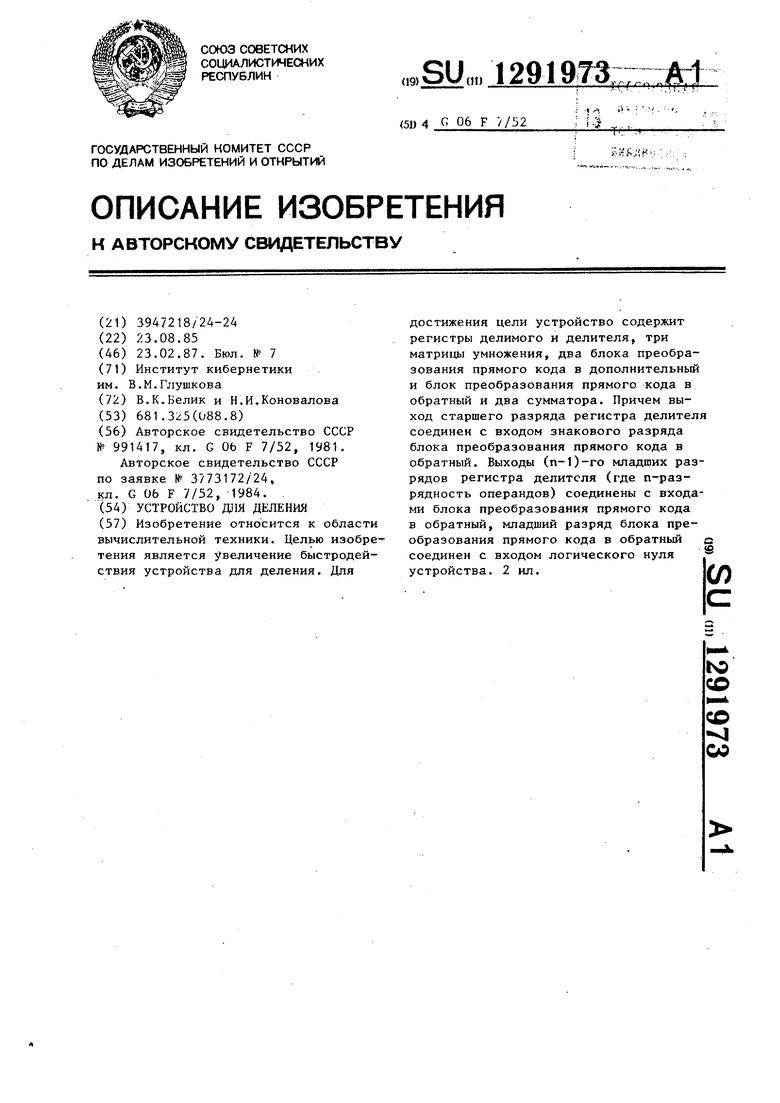

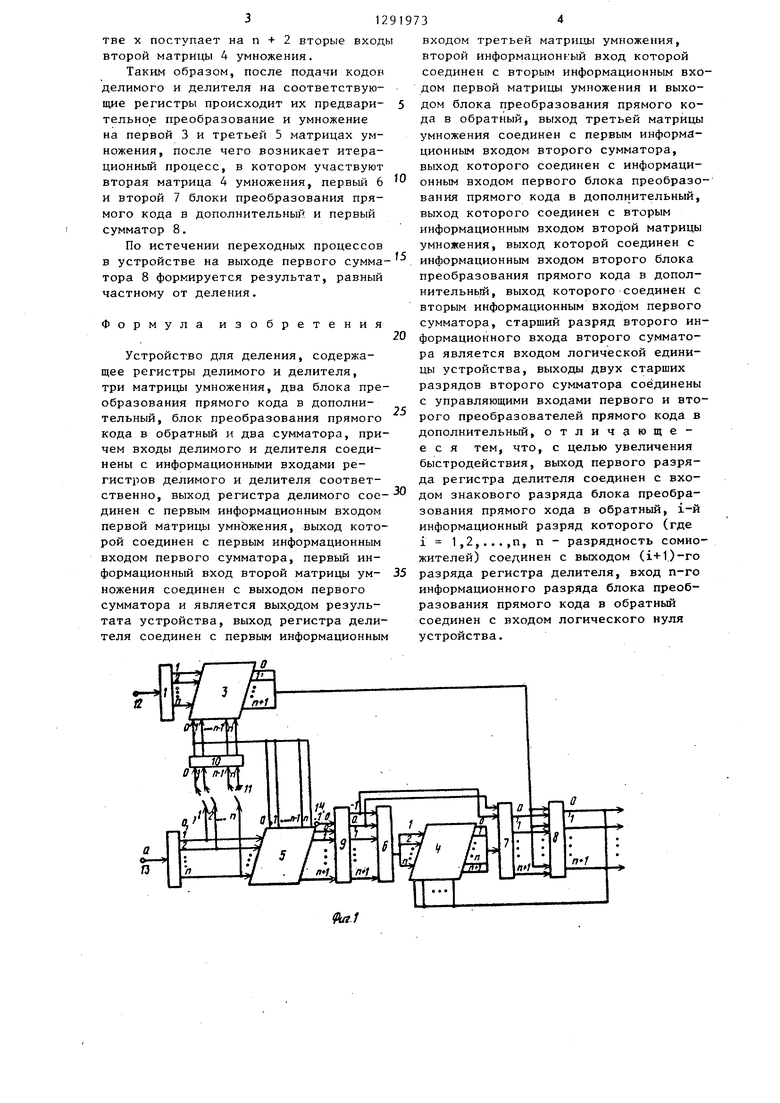

На фиг.1 показана структурная схема устройства для деления; на фиг.2 - графическая иллюстрация получения Ч (а) .

Устройство для деления содержит регистр 1 делимого, регистр 2 делите- ля , первую 3, вторую А и третью 5 матрицы умножения, первый 6 и второй 7 блоки преобразования прямого кода в дополнительный, первый 8 и второй 9.сумматоры, блок 10 преобразования прямого кода в обратный, вход 11 логического нуля, входы 12 и 13 делимого и делителя соответственно, вход 14 логической единицы.

В устройстве непрерывным способом реализуется итерационный, процесс согласно уравнению

( Ч

)- b-f(a),

2

где b - делимое; а - делитель.

Устройство работает следующим образом.

Одновременно подаются на регистры 1 и 2.делимое и делитель - два двоичных числа в нормализованной форме.

После занесения в регистр 2 значения делителя а (двоичного числа в нормализованной форме) п-разрядный код с выхода этого регистра поступает на первые входы третьей матрицы умножения 5 и со сдвигом входного кода на один разряд в сторону старших разрядов на входы блока 10. С помощью соответствующей коммутации выходов регистра 2 с входом блока 10 нормализованное число а вида 0,1ххх превращается в число вида 1,хххО.

Блок 10 преобразования прямого кода в обратный превращает число ви- Да 1,хххО, в число вида 1,ххх1.

В результате получаем код Ч (а) 1

9.R„. где

-Г - нормализованное число, представленное двоичным кодом в виде а а а,а Тогда 2 а

обр.

1,aj5...aJ,

.а,а,.

- п- .а„0

где а 1-а (фиг.2). Поступившие на первые входы третьей

fO

«5

919732

матрищ-. 5 умножения значения кода а перемножаются на ней со значением f(a), поступившим на второй вход третьей матрицы 5 умножения. Старшие (п+2) разряда кода произведения (а. Ч (а)с выхода третьей матрицы 5 умножения поступают на первый вход второго сумматора 9, где происходит сложение этого кода с единицей, поступающей на один из вторых входов первого сумматора,, соответствующий старшему разряду.

В результате на выходе второго сумматора 9 получаем значение кода, равное а Ч (а) - 1 .

Если полученное на втором сумматоре значение разницы (а- (а) - 1) положительное, то значение двух старших из п + 3 разрядов на выходе вто- ропо сумматора 9 будет равно 10, а если отрицательное, то 01. Эти два старших разр.яда в качестве стробирую- поступают на два входа управления ус первого 6 и второго 7 блоков преобразования прямого кода в дополнительный. Если код 10, то на выходе первого блока преобразования прямого кода в дополнительный будет тот же код, что и на входе, а на выходе второго - дополнительный к входному код. Обратная ситуация наблюдается при коде 01.

На выходе второй матрицы 4 умножения получается значение произведе20

30

35

ння прямого кода a-i(a) - 1 на код

.()

40

X , которое в зависимости от значе- ний двух старших разрядов 01 или 10 второго сумматора поступает на вторые п + 2 входы первого сумматора 8 . или без изменения,.или с образованием входного кода на дополнительный.

Если а чСа) 1, например а-ч (а) 1 ,хххх, то ((a) - 1) положитель- с ное число. В этом случае на выходе сумматора 9 получаем а-ч(а) + 1 10, XXX, где значение двух старших разрядов кода х х° 10.

Здесь учитывается перенос в старший разряд х сумматоров 8 и 9 при

о

сложении разрядов х .

На выходе первой матрицы 3 умножения получается значение произведения b Ч(а), которое поступает на первые п+2 входы первого сумматора 8.

50

55

На первом сумматоре получается сумма - al(a} - П Ь-ч(а) -х . Полученное на п + 2 выходах первого сумматора 8 значение суммы в качес 1291973

тве X поступает на п + 2 вторые входы второй матрицы 4 умножения.

Таким образом, после подачи кодов делимого и делителя на соответствующие регистры происходит их предвари- 5 тельное преобразование и умножение на первой 3 и третьей 5 матрицах умножения, после чего возникает итерационный процесс, в котором участвуют вторая матрица 4 умножения, первый 6 О и второй 7 блоки преобразования прямого кода в дополнительный и первый сумматор 8.

По истечении переходных процессов

входом третьей матрицы умножения, второй информационный вход которой соединен с вторым информационньм вх дом первой матрицы умножения и выхо дом блока преобразования прямого ко да в обратный, выход третьей матриц умножения соединен с первым информа ционным входом второго сумматора, выход которого соединен с информаци онным входом первого блока преобраз вания прямого кода в дополнительный выход которого соединен с вторым информационным входом второй матриц умножения, выход которой соединен с

.....„.„ ...,.„„ь,л процессов умножения, выход которой соединен с

в устройстве на выходе первого сумма- информационным входом второго блока тора В AoDMHtivpTpo rvoo-trntmr, .4

тора 8 формируется результат, равный частному от деления.

преобразования прямого кода в допол нительный, выход которого соединен с вторым информационным входом первого сумматора, старший разряд второго ин формационного входа второго сумматора является входом логической единицы устройства, выходы двух старших разрядов второго сумматора соединены с управляющими входами первого и вто рого преобразователей прямого кода в дополнительный, отличающееся тем, что, с целью увеличения быстродействия, выход первого разряда регистра делителя соединен с вхоФормула изобрете

преобразования прямого кода в дополнительный, выход которого соединен с вторым информационным входом первого сумматора, старший разряд второго ин формационного входа второго сумматора является входом логической единицы устройства, выходы двух старших разрядов второго сумматора соединены с управляющими входами первого и вто рого преобразователей прямого кода в дополнительный, отличающееся тем, что, с целью увеличения быстродействия, выход первого разряда регистра делителя соединен с вхоУстройство для деления, содержащее регистры делимого и делителя, три матрицы умножения, два блока преобразования прямого кода в дополнительный, блок преобразования прямого кода в обратный и два сумматора, причем входы делимого и делителя соединены с информационными входами регистров делимого и делителя соответ неГс „е вь, °° ° знакового разряда блока „рмора :i::.Triz :г г:™оГ:;™- -

рои соединен с первым информационным входом первого сумматора, первый информационный вход второй матрицы ум- 35 ножения соединен с выходом первого сумматора и является выхрдом результата устройства, выход регистра делителя соединен с первым информационным

информационный разряд которого (где 1 1,2,...,п, п - разрядность сомножителей) соединен с выходом (i+1)-ro разряда регистра делителя, вход п-го информационного разряда блока преобразования прямого кода в обратный соединен с входом логического нуля устройства.

входом третьей матрицы умножения, второй информационный вход которой соединен с вторым информационньм входом первой матрицы умножения и выходом блока преобразования прямого кода в обратный, выход третьей матрицы умножения соединен с первым информационным входом второго сумматора, выход которого соединен с информационным входом первого блока преобразования прямого кода в дополнительный, выход которого соединен с вторым информационным входом второй матрицы умножения, выход которой соединен с

умножения, выход которой соединен с

информационным входом второго блока

информационным входом второго блока

20

преобразования прямого кода в дополнительный, выход которого соединен с вторым информационным входом первого сумматора, старший разряд второго информационного входа второго сумматора является входом логической единицы устройства, выходы двух старших разрядов второго сумматора соединены с управляющими входами первого и второго преобразователей прямого кода в дополнительный, отличающееся тем, что, с целью увеличения быстродействия, выход первого разряда регистра делителя соединен с вхо ° знакового разряда блока „рмора - ° -

информационный разряд которого (где 1 1,2,...,п, п - разрядность сомножителей) соединен с выходом (i+1)-ro разряда регистра делителя, вход п-го информационного разряда блока преобразования прямого кода в обратный соединен с входом логического нуля устройства.

й/г.;

11,000.

(//а) прототип

1,111

1,001 0111

0,J 0,J001 0,101

0/ю 0,1101 qfff 0,1111 а Фиг.

У(а1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1317432A1 |

| Устройство для деления | 1984 |

|

SU1256019A1 |

| Устройство для деления | 1986 |

|

SU1397903A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1986 |

|

SU1354186A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

Изобретение относится к области вычислительной техники. Целью изобре- тения является увеличение быстродействия устройства для деления. Для постижения цели устройство сор.ержит регистры делимого и делителя три матрии}: умножения, два блока преобразования прямого кода в дополнительный и блок преобразования прямого кода в обратный и два сумматора. Причем выход старшего разряда регистра целителя соединен с входом знакового разряда блока преобразования прямого кода в обратный. Выходы (n-l)-ro младших разрядов регистра делителя (где п-раз- рядность операндов) соединены с входами блока преобразования прямого кода в обратный, младший разряд блока преобразования прямого кода в обратный Q а соединен с входом логического нуля устройства. 2 ил. сл N5 QO СО 00

Составитель Н.Маркелова Редактор Н.Лазаренко Техред В.КадарКорректор Н.Король

Заказ 265/47Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Устройство для деления | 1981 |

|

SU991417A2 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР по заявке № 3773172/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1987-02-23—Публикация

1985-08-23—Подача