И-зоб.ретение относится к вычислительной технике и может быть использовано , в частности, в арифметических устройствах цифровых и комбинированных машин.

Целью изобретения является увеличение быстродействия.

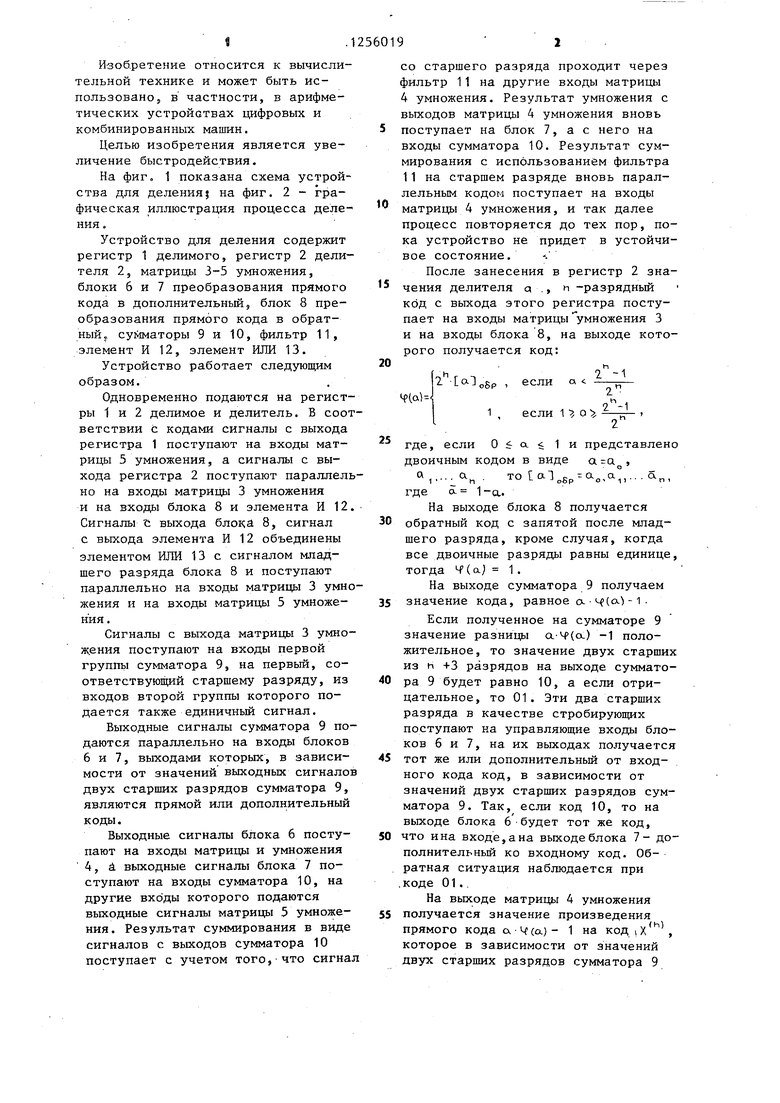

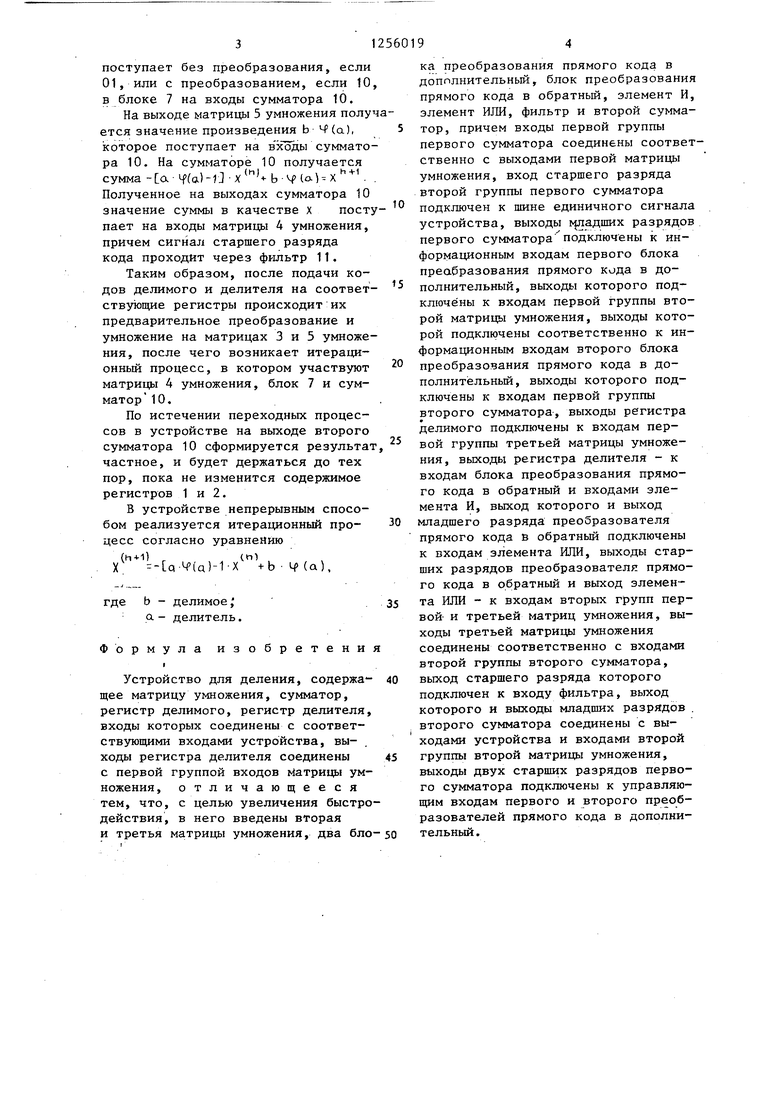

На фиг. 1 показана схема устройства для деления; на фиг. 2 - графическая иллюстрация процесса деления .

Устройство для деления содержит регистр 1 делимого, регистр 2 делителя 2, матрицы 3-5 умножения, блоки 6 и 7 преобразования прямого кода в дополнительный 5 блок 8 преобразования прямого кода в обратный, сумматоры 9 и 10, фильтр 11, элемент И 12, элемент ИЛИ 13.

Устройство работает следующим образом.

Одновременно подаются на регистры 1 и 2 делимое и делитель. В соответствии с кодами сигналы с выхода регистра 1 поступают на входы матрицы 5 умножения, а сигналы с выхода регистра 2 поступают параллелно на входы матрицы 3 умножения и на входы блока 8 и элемента И 12 Сигналы t: выхода блока 8, сигнал с выхода элемента И 12 объединены элементом ИЛИ 13 с сигналом младшего разряда блока 8 и поступают параллельно на входы матрицы 3 умножения и на входы матрицы 5 умножения .

Сигналы с выхода матрицы 3 умножения поступают на входы первой группы сумматора 9, на первый, соответствующий старшему разряду, из входов второй группы которого подается также единичный сигнал.

Выходные сигналы сумматора 9 подаются параллельно на входы блоков 6 и 7, выходами которых, в зависимости от значений выходных сигнало двух старших разрядов сумматора 9, являются прямой или дополнительный коды.

Выходные сигналы блока 6 поступают на входы матрицы и умножения 4, и. выходные сигналы блока 7 поступают на входы сумматора 10, на другие входы которого подаются выходные сигналы матрицы 5 умножения. Результат суммирования в виде сигналов с выходов сумматора 10 поступает с учетом того, что сигна

со старшего разряда проходит через фильтр 11 на другие входы матрицы 4 умножения. Результат умножения с выходов матрицы 4 умножения вновь

поступает на блок 7, а с него на входы сумматора 10. Результат суммирования с использованием фильтра 11 на старшем разряде вновь параллельным кодом поступает на входы

матрицы 4 умножения, и так далее процесс повторяется до тех пор, пока устройство не придет в устойчивое состояние.

После занесения в регистр 2 значения делителя а ., и -разрядный код с выхода этого регистра поступает на входы матрицы умножения 3 и на входы блока 8, на выходе которого получается код:

Ч(а1Ц

Il -Lal gp , если а l-ll

1

если 1 о

где, если О о. 1 и представлено двоичным кодом в виде а а ,

«1,...сх . то а„,а°,.,.а„, где а 1-0..

На выходе блока 8 получается

обратный код с запятой после младшего разряда, кроме случая, когда все двоичные разряды равны единице, тогда Ч (а} 1 .

На выходе сумматора 9 получаем

значение кода, равное сх ч(л -1

Если полученное на сумматоре 9 значение разницы а-Ч (а-) -1 положительное, то значение двух старших из и +3 разрядов на выходе сумматора 9 будет равно 10, а если отрицательное, то 01. Эти два старших разряда в качестве стробирующих поступают на управляющие входы блоков 6 и 7, на их выходах получается

тот же или дополнительный от входного кода код, в зависимости от значений двух старших разрядов сумматора 9. Так, если код 10, то на выходе блока 6-будет тот же код,

что и на входе, а на выходе блока 7- дополнительный ко входному код. Обратная ситуация наблюдается при коде 01.,

На выходе матрицы 4 умножения

получается значение произведения прямого кода а Ч (о.) - 1 на код, , которое в зависимости от значений двух старших разрядов сумматора 9

поступает без преобразования, если 01, или с преобразованием, если 10 в блоке 7 на входы сумматора 10.

На выходе матрицы 5 умножения полуется значение произведения b Ч (а), которое поступает на в ходы сумматора 10. На сумматоре 10 получается сумма .}-r X b Ч (о-Ь X . Полученное на выходах сумматора 10 значение суммы в качестве X поступает на входы матрицы 4 умножения, причем сигнал старшего разряда кода проходит через фршьтр 11.

Таким образом, после подачи кодов делимого и делителя на соответствующие регистры происходит их предварительное преобразование и умножение на матрицах 3 и 5 умножения, после чего возникает итерационный процесс, в котором участвуют матрицы 4 умножения, блок 7 и сумматор 10.

По истечении переходных процессов в устройстве на выходе второго сумматора 10 сформируется результат частное, и будет держаться до тех пор, пока не изменится содержимое регистров 1 и 2.

В устройстве непрерывным способом реализуется итерационный про- цесс согласно уравнению

(h-H)(П1

X (Q)-1-X -i-b Ч (а),

где b - делимое;

а - делитель.

Формула изобретения

I

Устройство для деления, содержа- щее матрицу умножения, сумматор, регистр делимого, регистр делителя, входы которых соединены с соответствующими входами устройства, выходы регистра делителя соединены с первой группой входов Матрицы умножения, отличающееся тем, что, с целью увеличения быстродействия, в него введены вторая и третья матрицы умножения, два бло-

0

5

5

ка преобразования прямого кода в дополнительный, блок преобразования прямого кода в обратньш, элемент И, элемент ИЛИ, фильтр и второй сумматор, причем входы первой группы первого сумматора соединены соответственно с выходами первой матрицы умножения, вход старшего разряда второй группы первого сумматора подключен к шине единичного сигнала устройства, выходы ь адших разрядов первого сумматора подключены к информационным входам первого блока преабразования прямого кода в дополнительный, выходы которого подключены к входам первой группы второй матрицы умножения, выходы которой подключены соответственно к информационным входам второго блока преобразования прямого кода в дополнительный, выходы которого подключены к входам первой группы второго сумматора, выходы регистра делимого подключены к входам первой группы третьей матрицы умножения, выходы регистра делителя - к входам блока преобразования прямого кода в обратный и входами элемента И, выход которого и выход младшего разряда преобразователя прямого кода в обратный подключены к входам элемента ИЛИ, выходы старших разрядов преобразователя прямого кода в обратный и выход элемента ИЛИ - к входам вторых групп первой и третьей матриц умножения, выходы третьей матрицы умножения соединены соответственно с входами второй группы второго сумматора, выход старшего разряда которого подключен к входу фильтра, выход которого и выходы младших разрядов . второго сумматора соединены с выходами устройства и входами второй группы второй матрицы умножения, выходы двух старших разрядов первого сумматора подключены к управляющим входам первого и второго преобразователей прямого кода в дополнительный.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1317432A1 |

| Устройство для деления | 1985 |

|

SU1291973A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

Изобретение относится к вычис- лительной технике и может быть не- пользовано как базовое в арифметических устройствах цифровых и. комбинированных вычислительных машин высокого быстродействия. Цель изобретения - повышение быстродействия. Устройство сЬдержит сумматор, регистр делимого, регистр делителя, три матрищи умножения, два блока преобразования прямого кода в дополнительный, блок преобразования прямого кода в обратный, элемент И, элемент ИЛИ и фильтр. 2 ил. 1C ел 05

aiooj.ff,ow o,on о,юо awr // o,m f,o x фиг. 2

a aoof-,,O07

Редактор П.Коссей

Составитель А.Клюев Техред Л.Сердюкова

Заказ 4824/48 Тираж 671 Подписное

ВНИИГШ Государственного комитета .СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А.Обручар

| Устройство для деления | 1975 |

|

SU710040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации памяти микро-ЭВМ | 1980 |

|

SU991427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1984-07-19—Подача