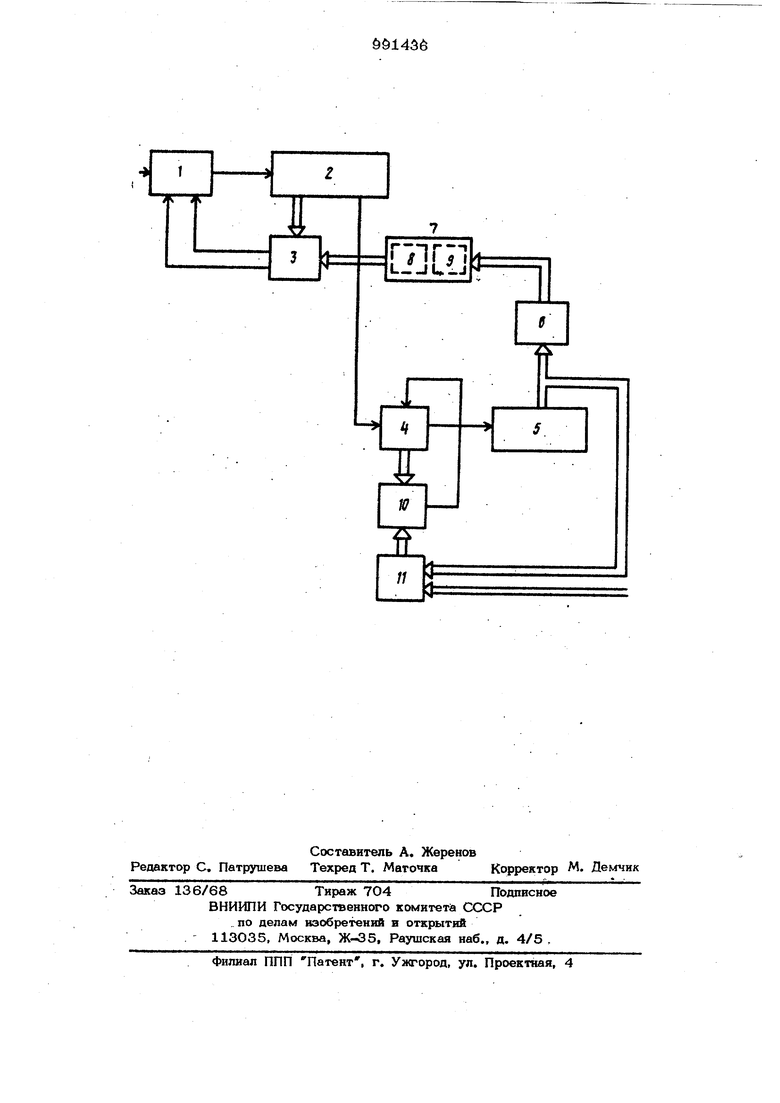

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок вьгчитания и сумм рования, два счетчика, делитель частоты, коммутатор, первый и второй выхоцы ко торого соединены соответственно с перьвым и вторым входами блока вьгчитания и суммирования, третий вход которого является информационным входом устройства, выход блока вычитания и суммирования соединен с входом первого счетчшш, первый выход которого соединен с информационным входом коммутатора, выход первого счетчика соединен с входом делителя частоты, выход которого подключен к входу второгб счетчика, младй шие разряды адрерного входа постоянного запоминающего блока соединены с въто-1 дом второго счетчика, выход постоянного запоминающего блока подключен к управляющему входу коммутатора, ста1Ш1ие 14азряды адресного входа соединены с управляющим входом устройства 2 . Однако данное устройство обладает недостаточной точностью. Цель изобретения - повыщение точности. Поставленная цель достигается тем, что в устройство, содерисашее блок вычитания и суммирования, два счетчика, делитель частоты, блок постоянной памяти и коммутатор, первый и второй вькоаы которого соединены соответственно с пер вым и вторым входами блока вычитания и суммирования, третий вход которого является информационным входом устройства, выход соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутатора, второй выход первого счетчика соединен с информационным входом делителя частоты, первый выход которого подключен к входу второго счетчика, выхра которс го соединен с младшими разрядами адрео ного входа блока постоянной памяти, стар шие разряды адресного входа которого соединены с управляющим входом устройства, введены схема сравнения, дешифратор и блок задания кодов характеристик, вход которого соединен с выходом деши4 ратора, а выход подключен к управляющему входу коммутатора, вхбд дешифратора соединен с выходом второго счетчика, входы схемы сравнения соединены соответ отвенно с вторым выходом делителя частоты и выходом блока посто5шной памяти, выход схемы сравнения подключен к установочному вхоцу делителя частоты. На чертеже представлена схема уст ройства. Устройство содержит блок 1 вычитания я суммирования, счетчик 2, коммутатор 3, делитель 4 частоты, счетчик 5, дешифратор 6, блок 7 задания кодов характеристик, включающий наборное поле 8 и переключатель 9, схему 10 сравнения, блок 11 постоянной памяти. Разбиение на участки аппроксимации осуществляется делителем 4 частоты, вход которого подключен к одному из выходов счетчика 2. Коэффициенты деления делителя часто ты хранятся в блоке 11 постоянной памяти. Устройство работает следующим образом. На вход блока 1 вычитания и суммирования от преобразователя параметрн. число импульсов (на чертеже не показан) поступает последовательность импульсов. В зависимости от подключенной характеристики в блоке 7 И кода на выходе дешифратора 6 с выхода блока 7 на управляющий вход коммутатора 3 прступает управляющий код, разрешающий прохождение определенного числа импульсов, сформированных на выходах счетчика 2, на входы блока 1 вычитания и суммирования (импульсов). Это и число импульсов добавляется к последовательности импульсов от преобразователя параметр-число импульсов или вычитается из нее на данном участке аппроксимации. В результаге на вход счетчика 2 поступает лйнеаризо ванная последовательность импульсов. Выходы дешифратора 6 в блоке 7 задания кодов характеристик переключателем 9 подключены к группе шин участков, соответствукяцей выбранной характеристике. Каждая из шин участков на наборном поле 8 соединена с управляющими входами коммутатора 3, исходя из того, чтобы разрешалось прохождение на выходы коммутатора 3 определенного числа импульсов, которое добавляется или вычитается из входной последовательности импульсов на участке аппроксимации, который соответствует данн(Л шине участков. I Выбор группы шин участков в аппроксимации, которая соответствует данной характеристике, осуществляется переключателем 9, который подключает соответствующую группу шин участков к выходам дешифратора 6. На выход блока 11 постоянной памяти I поступает коц коэффициента деления, соответствующий текущему 59 участку аппроксимации. Выборвш коэффи- циента аеления производится по младшим адресным разрядам блока 11, подключенным к группе выходов вгорого счетчика 5 и старшим адресным входам, которью использованы для выбора страницы блока . постоянной памяти, соответствующей типу измерительного преобразователя. При совпадении кода на выходе блока 11 и кода на выходах триггеров делителя 4 частоты, схема 10 сравнения вырабатывает сигнал сброса делителя 4 частоты, .при этом счетчик 5 переключается в состояние, которое соответствует следующему участку аппроксимации.. Таким образом переключение на еле- дуюший участок е ппроксимации происходит после поступления на вход устройства числа импульсов, равного длине текущего участка аппроксимации, которая хранится в блоке 11 постоянной памяти. Изобретение обеспечивает уменьщение погрешности линеаризации. Формула изобретения Устройство для линеаризации характеристик измерительных преобразователей, содержащее блок вычитания и суммирова- ния, два счетчика, делитель частоты, бло постоянной- памяти в коммутатор, первый и выходы которого соединены соответственно с первым и вторым входами 3е6 блока вычитаний в суммирования, третий вход которого является информационным входом устройства, выход соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутатора, второй выхоа первого счетчика соединен с информациЬтаым входом делителя частоты, первый выход которого подключен к входу второго-счет чика, выход которого соединен с млацшимн разрядами адресного входа блока постоянней памяти, старшие разряды адресного входа которого соединены с уЬ равляижшм входом устройства, отличающееся тем, что, с 1юдью повышения точности, в него введены схема сравнения, дешифратор н блок заванвя кодов характеристик, вход которого соеця. iieH с выходом дешифратора, а выход подключен к управляющему входу к 1мутатора, вход дешифратора соединён с выходом второго счетчики, входы схемы cpaiaнения соединены соответственно с вторые выходом делителя частоты и выходом бло-ка,постоянной памяти, выход схемы сравнения подключен к установочному . входу делителя частоты. Источники информашш, принятые во внимание при экспертвэе 1.Авторское свидетельство. OCXJP № 698000, кл. GO6F 15/20, 1978. 2.Авторское свидетельство СССР по заявке NJ 3278083/18- 4, кя. G06F 15/2О, 1981 (прототиа).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для линеаризации характеристик измерительных преобразователей | 1981 |

|

SU982007A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1037266A1 |

| Функциональный генератор | 1980 |

|

SU902022A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1056220A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1983 |

|

SU1126978A1 |

| Многоканальный функциональный преобразователь | 1980 |

|

SU1023348A2 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

Авторы

Даты

1983-01-23—Публикация

1981-10-09—Подача