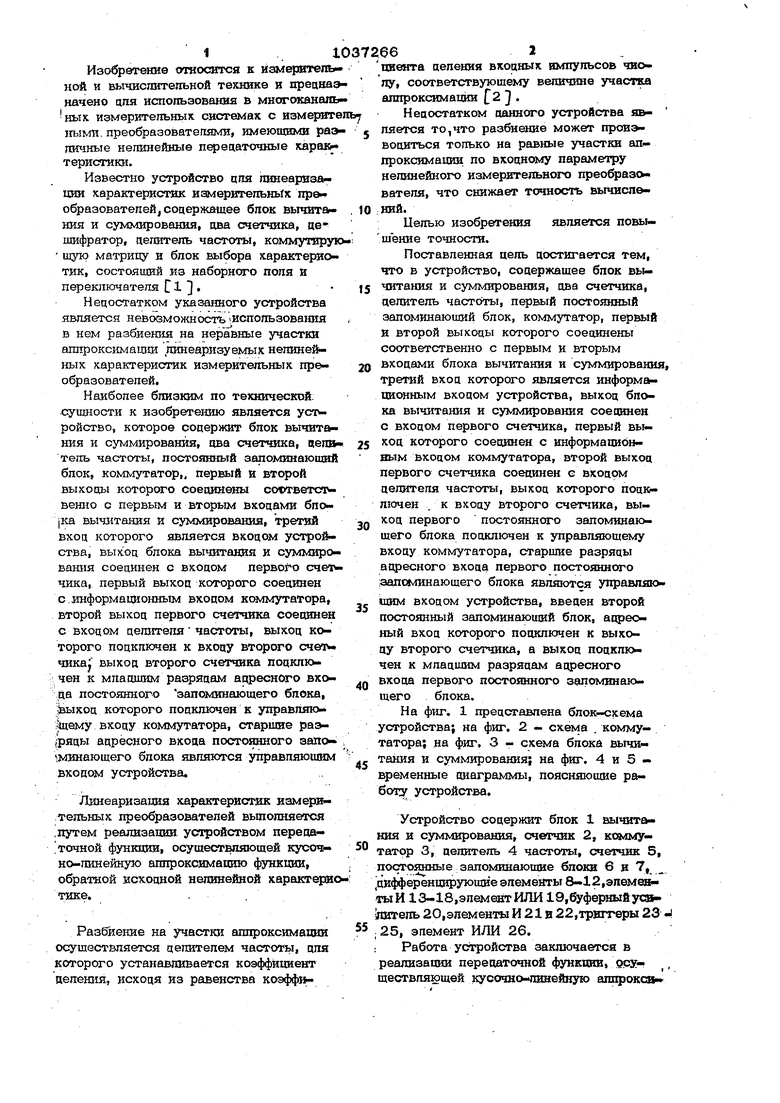

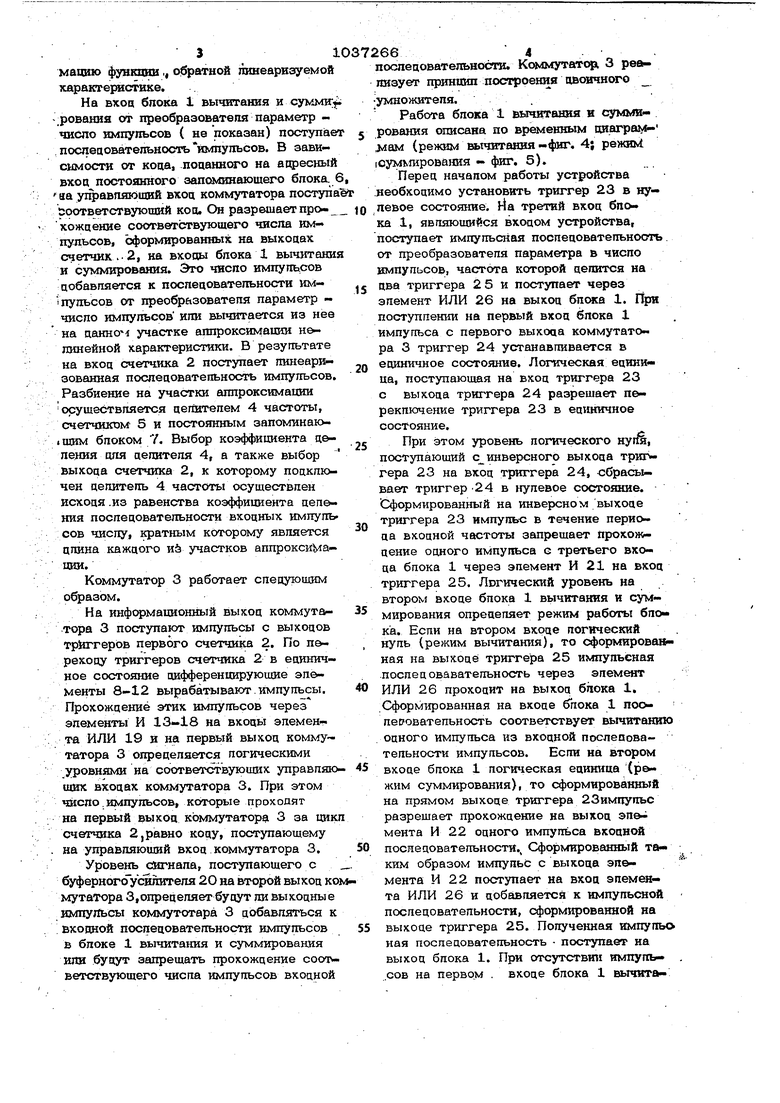

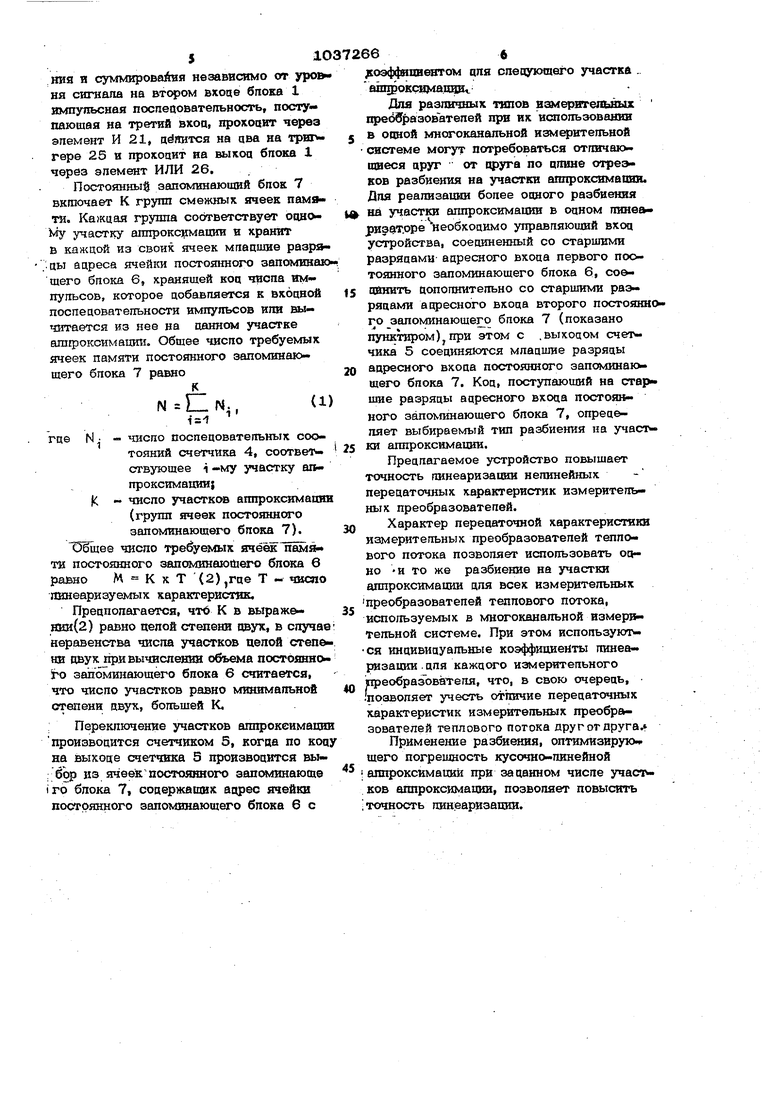

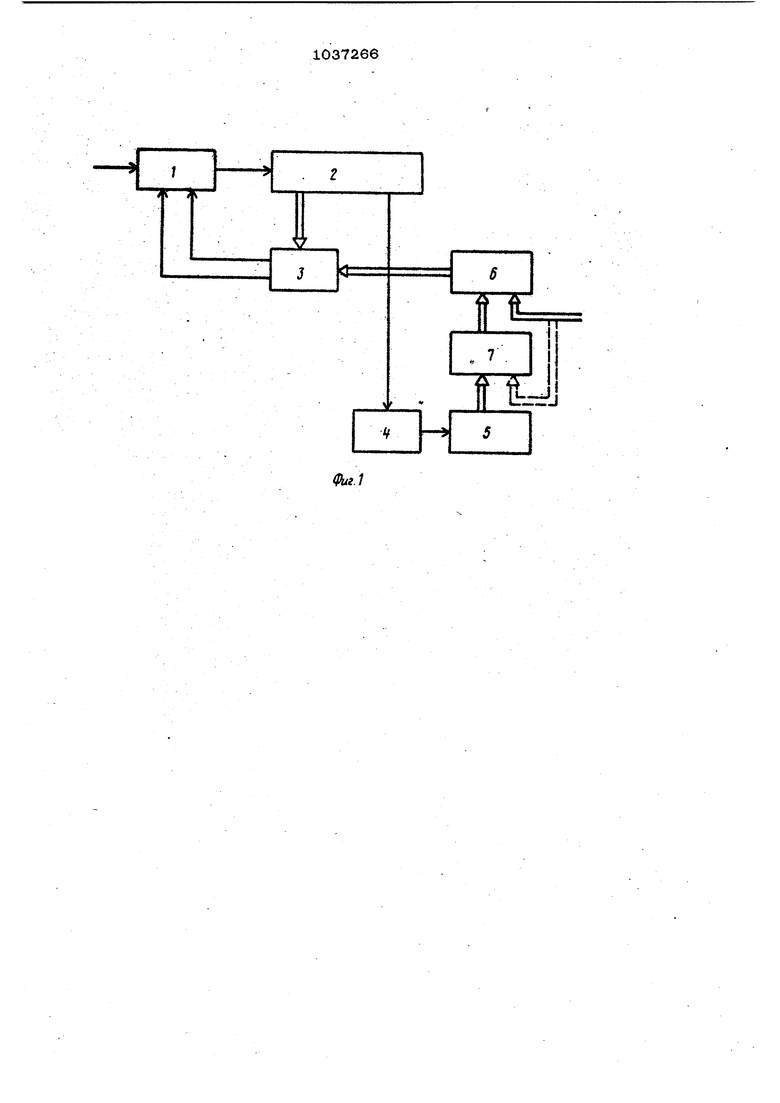

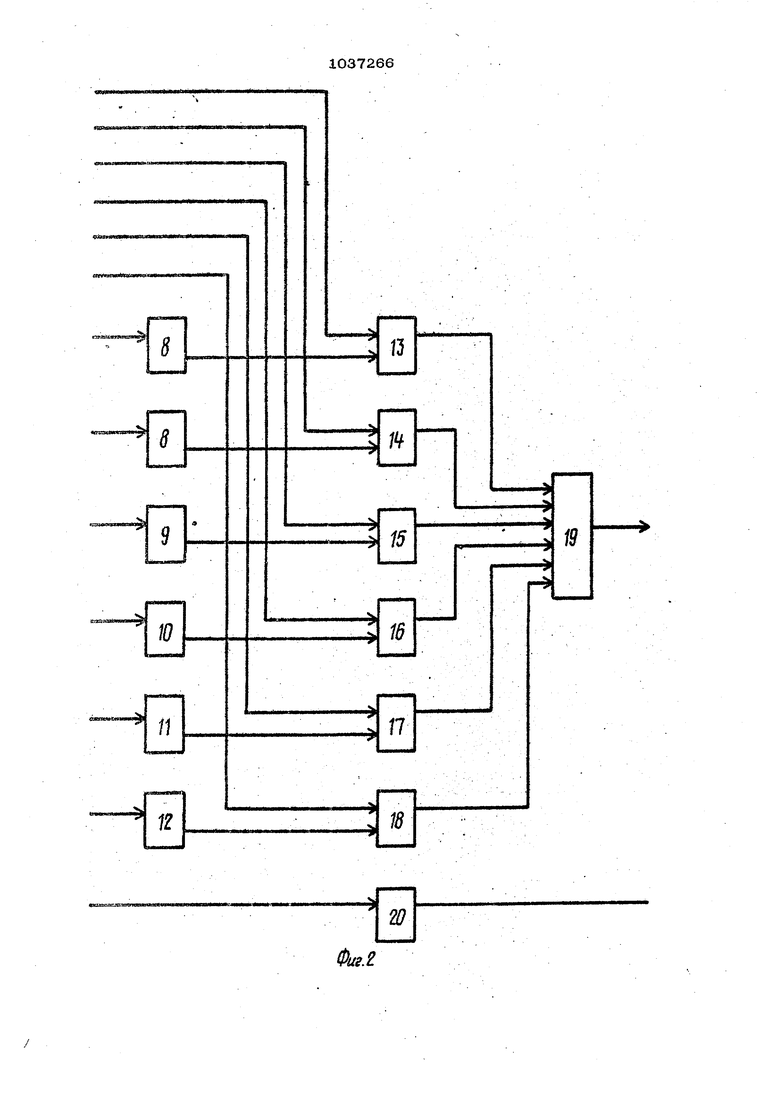

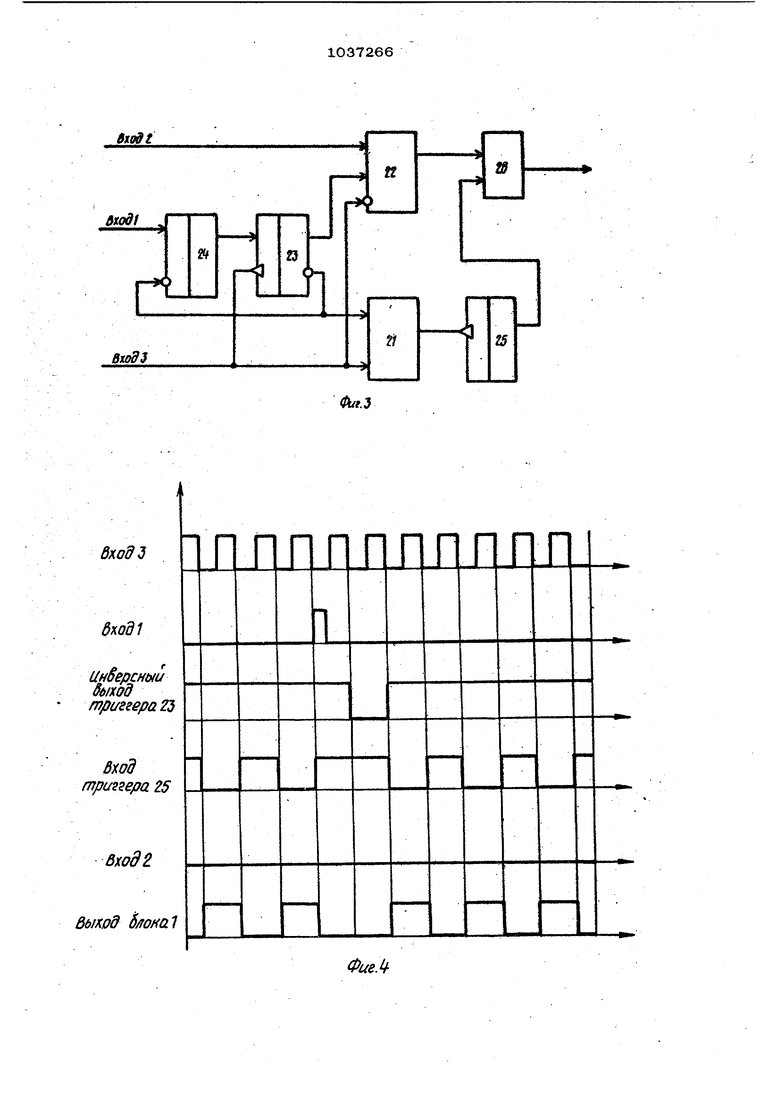

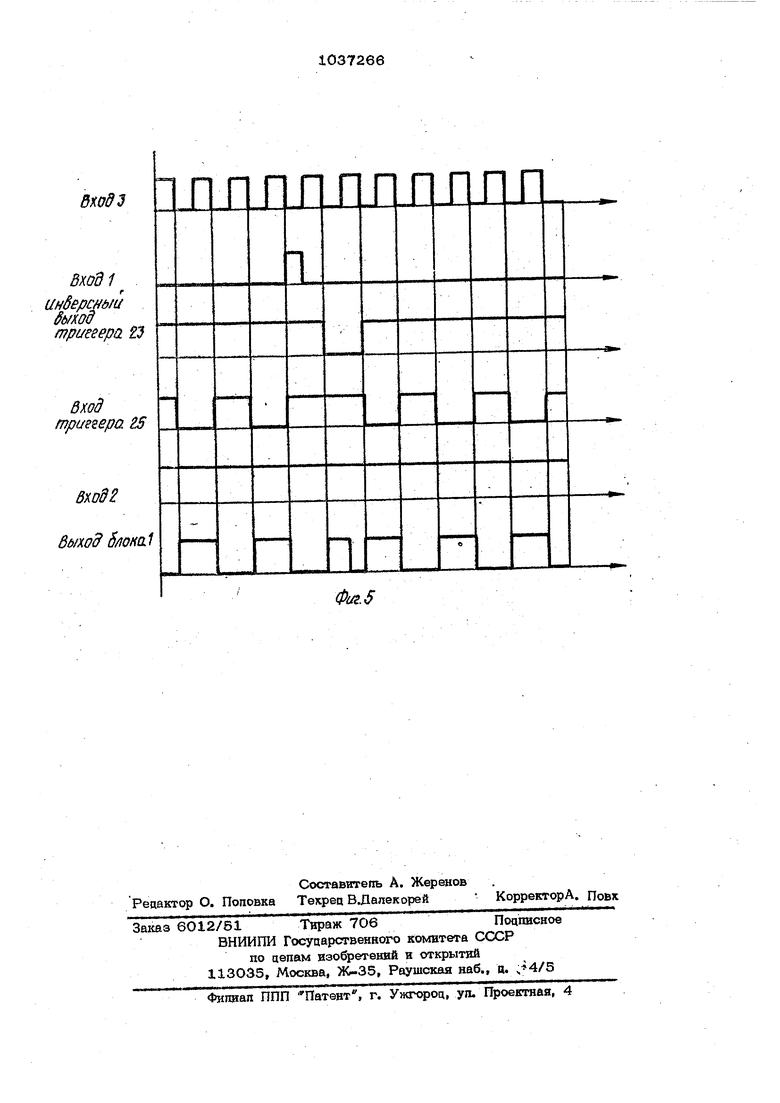

1 Изобретение относится к измеритель ной и вычиспитепьной текника и прецнаэ начено цпя испопьаовакия в многоканапь ных измерительных снстемах с измерит jibSKffl, преобразоватеггами, имеющими раэ личные нелинейные пфедаточиые характеристики. Известно устройство цпя пинеариза-шш характеристик измерительных преобразоватепей, содержащее блок вычита ния и суммирования, два счетчика, це шифратор, дешггепь частоты, коммутяру щую матрицу и блок выбора характерио тик, состоящий из наборного поля и перею1:ючателя С1 Недостатком указанного устройства является невозмоншостьИспользования в нем разбиешш на неравные участья аппроксимации линеаризуемых непиней нык характеристик измерительных преобразователей. Наиболее близким по технической. сущности к изобретению является уст ройство, которое содержит блок вычит&ния и суммирования, цва счетчика, вепв тепь частоты, постоянный запоминающий блок, коммутатор, первый и второй выходы которого соединены соогветсрвешю с первым и вторым входами бпоjim вычитания и суммирования, третий вход которого является входом устройства, выход блока вычитания и суммирования соединен с входом первого счет чика, первый выход которого соединен с.информационным входом коммутатора, второй выход первого счетчика соещшен с входом делителя частоты, выход которого подключен к входу второго C4eiw чика выход второго счетчика подключен к миадщим разрядам адресного входа постоянного запомин 1ющего блока, Ьыход которого подключен к улравляк Ацему входу коммутатора, старшие разгряды адресного входа постоянного заповминающего блока являются управляющим входом устройства. Линеаризация характеристик измерл тельных преобразователей вьшолняется .путем реализации устройством передаточной функции, осуществляющей кусочнсх-линейную аппроксимацию функции, обратной исходной негашейной характерн тике,.. Разбиение на участки аппроксимации осуществляется делителем частоть, для которого устанавливается коэффициент деления, исходя из равенства коэфф 66ииента деления входных импульсов числу, соответствующему величине участка аппроксимации 2 . Недостатком данного устройства является то,что разбиение может производиться только на равные участки аппроксимации по входному параметру нелинейного измерительного преобразователя, что снижает точность вьпшслеЦелью изобретения является повььщение точности. Поставленная цель достигается тем, что в устройство, содержащее блок вычитания и суммирования, два счетчика, делитель частоты, первый постоянный запоминающий блок, коммутатор, первый и второй выходы которого соединены соответственно с первым и вторым входами блока вычитания и суммирования, третий вход которого является информеьцисданым входом устройства, выход блока вычитания и суммирования соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутатора, второй выход первого счетчика соединен с входом делителя частоты, выход которого подключен . к входу второго счетчика, выход первого постоянного запоминающего блока подключен к управляющему входу коммутатора, старщие разряды адресного входа первого постоянного ;аапоминающего блока явл5потся управпяк шим входом устройства, введен второй постоянный запоминающий блок, ащ)еоный вход которого подключен к выходу второго счетчика, а выход подклк чен к младщим разрядам адресного входа первого постоянного запоминающего блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема . коммутатора; на фиг, 3 - схема блока вычитания и суммирования} на фиг. 4 и 5 временные диаграммы, поясняющие работу устройства. Устройство содержит блок 1 вычитания и суммирования, счетчик 2, коммутатор 3, делитель 4 частоты, счетчик 5, постоянные запоминающие блоки 6 и 7, дифференцирующие элементы 8-12 ,эдемвны И 13-18ээлемент ИЛИ 19,буферный усиитель 20,эпемен1Ъ1 И 21 в 22,трвггеры 23 25, элемент ИЛИ 26. Работа устройства заключается в реализации передаточной функции, ОРУ- , ществляющей кусочно-линейную алпрокс 10 манию фунгаокв., обратной линеаризуемой каракгещстике. На вхоц блока I вычитания и cyiviMK; -.рования от преобразователя параметр число импульсов { не показан) поступает поспецовательностъимпульсов. В завиС11МОСТИ от копа, поданного на адресный вход постоянного запоминающего блока. 6, аа управпяющий вход коммутатора поступает Соответствующий код. Он разрииает прохождение соответствующего числа импульсов, сформированных на выходах счетчик.. 2, на входы блока 1 вычитани и суммирования. Это число импугшсов добавляется к последовательности им- i пульсов уг преобразователя параметр число импульсов или вычитается из нее на данноч участке аппроксимации н&гашейной характеристики. В результате на вход счетчика 2 поступает линеаризованная последовательность импульсов Разбиение на участки аппроксимации осуществляется делителем 4 частоты, счетчкктзм 5 и постоянным запоминак 1 щим блоком 7. Выбор коэффициента деления для делителя 4, а также выбор выхода счетчика 2, к которому подкпго чен делитель 4 частоты осуществлен исходя .из равенства коэффициента деления последовательности входных импуль сов числу, кратным которому является длина каждого и6 участков аппроксиЫаЮШ. Коммутатор 3 работает следующим образом. На информационный выход коммутатора 3 поступают импульсы с выходов триггеров первого счетчика 2. По п&реходу триггеров счетчика 2 в единичное cocTosnme дифференцирующие элементы 8-12 вырабатывают.импульсы. Прохождение этих импульсов через элементы И 13-18 на входь элемента ИЛИ 19 и на первый выход коммутатора 3 определяется логическими уровнями на соответствующих управляю UOIX входах коммутатора 3. При этом число. импульсов, которые прокодят на первый выход коммутатор 1 3 за цик счетчика 2,равно коду, поступающему . на управляющий вход коммутатора 3. Уровень Сигнала, поступающего с буферногсГусжпителя 20 на второй выход ко мутатора 3,определяет будут ли выходные импульсы коммутотара 3 добавляться к входной последовательности импульсов в блоке 1 вычитания и суммирования или будут запрещать прохождение COOTW ветствующего числа импульсов входной 66 поспецовательнсютк. Коммутатечх 3 рв&лизует принюш построения двоичного Умножителя. Работа блока 1 вычитания и сумлгаровакия описана по временным OH.arpais ллелл (режим вьтчитания-фиг, 4; режнк( |Суммирова П1я фиг. 5). Перед началом работы устройства необходимо установить триггер 23 в ну- ,певое состояние. На третий вхоц бпо« ка 1, являющийся входом устройства, поступает импульсная последовательность от преобразователя параметра в число кмпупьсов, частота которой делится на чва триггера 25 и поступает через элемент ИЛИ 26 на выход блсжа 1. При поступпении на первый вход блока 1 кмпупьса с первого выхода коммутатора 3 триггер 24 устанавливается в единичное состояние. Логическая единица, поступаюишя на вход триггера 23 с выхода триггера 24 разрешает переключение триггера 23 в единичное состояние. При этом уровень лошческого ну1, поступающий с инверсного выхода триггера 23 на вход триггера 24, сбрасывает триггер.24 в нулевое состояние. Сформированный на инверсном выходе триггера 23 импульс в течение периода входной частоты запрещает прохон дение одного импульса с третьего входа блока 1 через элемент И 21 на вход триггера 25. Логический уровень на втором входе блока 1 вычитания и суммирования определяет режим работы блока. Еспи на втором входе логический нуль (режим вычитания), то сформированная на выходе триггера 25 импульсная .последовавательность через элемент ИЛИ 26 проходит на выход бдока 1. Сформированная на входе блока 1 поолероватепьность соответствует вычитанию одного импульса из входной поспеповательности импульсов. Если на втором входе блока 1 логическая единица ( суммирования), то сформированный на прямом выходе триггера 23импульс разрешает прохождение на выход элемента И 22 одного импульса входной поснецовательностн., Сформированный таким образом импульс с выхода элемента И 22 поступает на вход элемента ИЛИ 26 и добавляется к импульсной последовательности, сформированной на выходе триггера 25. Полученная ная последовательность - поступает на выход блока 1. При отсутствии импульсов на первом . входе блока 1 вычитанйя я суммироваАия независимо от уров ня сигнала на вхоце бпока 1 импульсная поспецоватепьность, поступаюшая на третий вхоц, прохоцит через элемент И 21, дёяится на цва на триг гере 25 и проходит на выкоц бпока 1 через элемент ИЛИ 26. Постоянный запоминающий бпок 7 вкшочает К групп смежных ячеек пам ти. Кажцая группа сосзтветствует оцно Wy участку аппроксрмашга и хранит в кажцой из своик ячеек мпацшие разра . цы ацреса ячейки постоянного запоминаю щего бпока 6, хранящей коц числа импупсьсов, которое добавляется к входной после доватегсьности импульсов или вычитается из нее на цанном участке ашгроксимации. Общее число требуемых ячеек памяти постоянного запоминающего блока 7 равно К N d N. . гце N - число последовательных соотояний счетчика 4, соответствующее i -му участку аппроксимашш}число участке аппроксимашш (групп ячеек постоянного запоминающего блока 7). Общее чиспо требуемых aneiieliaMHти постоянного запоминаюшего блока 6 равно М К X Т (2),гце Т - чисяо Линеаризуемых характеристик. Предполагается, чтб К в выраж&нйи(2) равно целой степени даух, в случав неравенства числа участков целой степе ни двyxJipи вычислении объема постоянно зго запоминающего блока 6 считается, что число участков равно минимальной степени двух, большей К, Переключение участков аппроксимаци производится счетчиком 5, когца по коц на выходе счетчвака S производится вы: бор из ячеек постоянного запсяупшающ© iro блока 7, содержащих адрес ячейки постоянного запоминающего блока 6 с доэффяов ггом апя следующего участка . аппроксимации Для различных типов измерительных преобразователей при их использовании в одной многоканальной изм ительной системе могут потребоваться отличающиеся друг от друга по длине отреэков разбиения на участки аппроксимации. Для реализашш более одного разбиения на участки аппроксимации в одном линеа ризаторе необходимо управляющий вход устройства, соединенный со старшими разрядами адресного входа первого поотоянного запоминающего блока 6, со&дШшть дополнительно со старшими разрядами aigjecH ro входа второго постоянного запоминающего бпока 7 (показано пунктиром), при этом с .выкоцом счет чика 5 соединяются младшие разряды адресного вкода постоянного запоминающего блока 7. Код, поступающий на старшие разряды адресного входа постоя ного запокшнающего блока 7, определяет выбираемый тип разбиения на учас ки аппроксимашш. Предлагаемое устройство повышает точность линеаризации нелинейных передаточных характеристик измерительных преобразователей. Характер передаточной характеристики измерительных преобразователей теплового потока позволяет использовать одно И то же разбиение на участки аппроксимации для всех измерительных преобразователей теплового потока, используемых в многоканальной измерительной системе. При этом используют ся индивидуальные коэффициенты линеаризащш.для каждого измерительного преобразователя, что, в свою очередь, .позволяет учесть отличие передаточных характеристик измерительных преобразователей геплового потока друготпруга. Применение разбиения, оптимизирующего погрешность кусочно-линейной аппроксимации при заданном числе участ КОБ аппроксимации, позволяет повысить точность линеаризации.

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для линеаризации характеристик измерительных преобразователей | 1981 |

|

SU982007A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1981 |

|

SU991436A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1056220A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1983 |

|

SU1126978A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Цифровое устройство для линеаризации характеристики измерительных преобразователей | 1981 |

|

SU1015391A2 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Устройство для измерения температуры | 1986 |

|

SU1394063A1 |

| АППРОКСИМАТОР МОНОТОННЫХ ФУНКЦИЙ | 1991 |

|

RU2023297C1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ ПРЕОБРАЗОВАТЕЛЕЙ, содержащее блок вычиташя и суммирова ния, два счетчика, детштепъ частоты, первый постоянный, запоминаюишй блок, коммутатор, первый к второй выходы которого соединены соответственно с первым и вторым входами блока вычитания и суммирования, третий вход которого является информационным входом устройства, выход блока вычитания и суммирования соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутатора, второй выход первого счетчика соединен с входом ёгштеля частоты, выход которого подключен к входу второго счетчика, выход перво го постоянного аапоминающьго блока подключен к управл5 ощему входу комму «татора, старшие разряды адресного вхо- да первого постоянного запоминаюоюго блока являются управляющим входом устройства, отличающееся тем, что, с цепью повышения точнооти, в него введен второй постоянный (Л зад оминающий блок, адресный вход которого подключен к выходу второго счетчика, выход подключен к младшим разрядам адресного входа первого постоянного запоминающего блока. оо IND О) О5

Фиг.

бходз

Bxodi

иноерсньш дшод mpuseepa 0

Вкод tS

8wd2

бб/xoff S/ioKa.1

Фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство для линеаризации характериситик измерительных преобразователей | 1978 |

|

SU698000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ПЛОМБА ПРЕИМУЩЕСТВЕННО ДЛЯ ЖЕЛ.-ДОР. ВАГОНОВ | 1925 |

|

SU3278A1 |

| G, 06 F 15/2О, 1981 (прототип). | |||

Авторы

Даты

1983-08-23—Публикация

1982-04-07—Подача