С54) ГЕЧЕРАТбР ЦИКЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1981 |

|

SU995289A1 |

| Генератор циклов | 1979 |

|

SU877511A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Генератор циклов | 1976 |

|

SU647680A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для генерирования импульсных сигналов с заданными периодами следования. Общеизвестны электронные и импуль ные генераторы, собранные на лампа или .транзисторах по схеме кварцевых генераторов, блокинг-генераторов, мультивибраторов. Недостатком таких электронных схе генераторов циклов является ограниченность диапазона згщания периода следования выходных сигналов микросекундными - миллисекундными значениями. Для расширения диапазона задания периода следования выходных сигналов используют делители частоты или счет чики импульсов на триггерах, схемы, которых становятся сложными при коэф фициентах деления больше 2 Указанные недостатки устранены в генераторах циклов, собранных на регистре сдвига, сумматоре, генераторе этсшонной частоты, блоке синхронизации и блоке перестройки 1. Наиболее близким техническим-реше нием к предлагаемому является генера тор циклов, содержащий генератор эталонной частоты, блок синхронизации, блок перестройки, сумматор и регистр сдвига, подключенный выходом к первому входу первого элемента И, подключенного выходом к первому входу сумматора, другие входы которого подключены кпервому выходу блока синЧ хронизации, подключенного входом к выходу генератора эталонной частоты и к выходу второго элемента И, подключенного первым вхтодом к выходу блока перестройки, подключенного входами к первой, группе выходов блока синхронизации, и вторым входом - к единичному выходу триггера, подключенного нулевым выходом ко второму входу первого элемента И, нулевым входом - кЪ второму вмходу блока синхронизации и первому входу третьего элемента И, подключенного вторым входом к выходу переноса сумматора и выходом - к единичному входу триггера и выходу устройстваО. Недостатком генератора циклов является сложность его перестройки на заданную частоту, что является следствием двоичной обработки сумматором содержимого регистра сдвига.

Перестройка.данного генератора циклов на эадайную частоту требует сложных вычислений для расчета двоичных начальных условий и большого количества операций по -ручной установке ДВОИЧНОГО, кода начальных условий на клавшином устройстве блока перестройки.

Цель изобретения - упрошениё перестройки генератора циклов на заданную частоту.

Указанная цель достигается тем, что генератор циклов содержит генератор эталонной частоты, блок синхронизации, устройство ввода ,и элемент ИЛИ, сумматор и регистр сдвига, первый, второйи третий элементы и и триггер, причем выход регистра сдвига подсоединен к первому входу первого элемента и, выход которого подклйчен к первому входу сумматора, второй вход которого подсоединен к первому выходу блока синхронизации,

вход которого подключен к выходу генератора эталонной частоты, третий вход сумматора связан с выходом второго двухвходового элемента И, первый вход которого связан с выходом элемента ИЛИ, входы которого соединены с выходами устройства ввода, входы которого подсоединены к группе выходов блока синхронизации, второй вход второго элемента И подсоединен к прямому выходу триггера, инверсный выход которого связан со вторым входом первого элемента И, второй выход блока синхронизации связан с нулевым

вхрдом триггера и с первым входом

третьего элемента И, второй вход которого подсоединен к выходу переноса сумматора,а выход третьего элемента И подключен к единичному входу триггера и является выходом устройства, два О-три гера, первый и второйдополнительные элементы ИЛИ и четвертый элемент И, причем выход суммы сумматора подключен к входу первого D-триггера, выход которого подсоединен к первому входу первого дополнительного элемента ИЛИ, выход которого соединен со входом второго D-триггера, выход которого связан с первым входом второго дополнительного элемента ИЛИ, второй вход которого и первого дополнительного элемента ИЛИ соединены с выходом четвертого элемента И,первый вход которого подключен к выходу переноса сумматора., а второй вход подсоедийен к третьему выходу блока синхронизации.

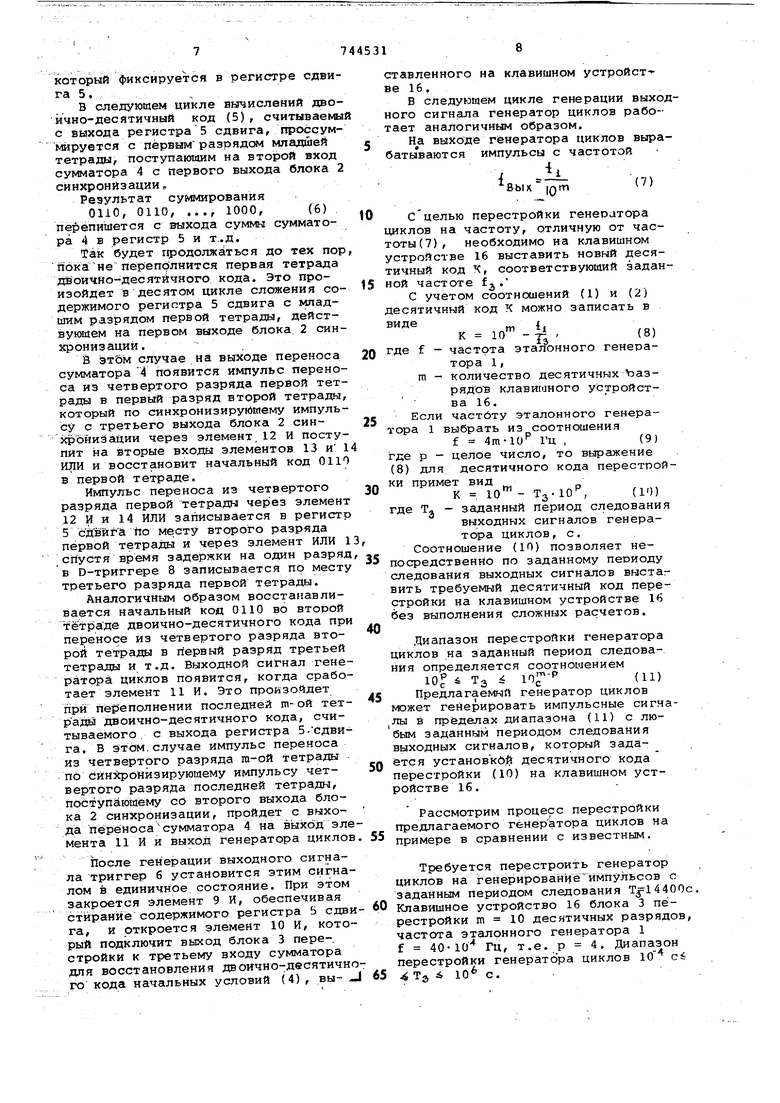

На чертеже изображена стоуктурная схема генератора циклов.

Генератор циклов содержит генератор 1 эталонной частоты, блок 2 синхронизации, блок 3 перестройки, сумматор 4, регистр 5 сдвига, триггер 6, ва D-триггера 7 и 8, четыре двухвхОдовых элемента 9-12 И, два двух744531

входовых элемёнта 13 и 14 ИЛИ. Блок перестройки 3.состоит из элемента 15 ИЛ и десятичного клавишного устройства 16.

Выход генератора 1 эталонной частоты подключен к входу блока 2 синхронизации, первая группа выходов которого подключена к клавишному устройству 16 блока 3 перестройки.

Сумматор 4 подключен первым входом

к выходу элемента 9 И, подключенного

первым входсяи к выходу регистра 5 сдвига, вторым входом - к первому .: выходу блока 2 синхронизации, третьим входом - к выходу элемента 10 И, подключенного первым входом к выходу

блока 3 перестройки и вторым входом - к единичному выходу триггера б; Нулевой выход триггера б подключен ко второму входу элемента 9 И.

Нулевой вход триггера 6 подключен

второму выходу блока 2 синхоонизации и к первому входу элемента,, 12 И и выходу переноса сумматора 4. Единичный вход триггера б подключен к выходу элемента 11 И и к выходу генератора циклов.

Выход суммы сумматора 4 подключен к входу D-триггера 7, выход которого подключен к первому входу элемента

13 ИЛИ. Выход элемента 13 ИЛИ подключен к входу D-триггера 8, выход которого подключен к первому входу элемента 14 ИЛИ, подключенного вторым входом к второму входу элемента

13 ИЛИ и к выходу элемента 12 И, подключенного вторым входом к третьему, выходу блока 2 синхронизации. Выход элемента-14 ИЛИ подключен к входу регистра 5 сдвига. Выходы клавишного устройства 16 подключены к входам

элемента 15 ИЛИ, выход которого является выходом блока 3 перестройки.

Генератор циклов работает следующим образом.

Генератор 1 эталонной, частоты вырабатывает импульсные сигналы с частотой f, которые поступают в блок 2 синхронизации. Блок 2 синхронизации с помощью делителя частоты вырабаты:вает по первому и второму выходу импульсы с частотой

.(П

где п - количество двоичных разрядов

регистра сдвига 5. Импульсы на первом выходе блока 2 синхронизации синхронизируют первый младший разряд регистра 5 сдвига, и на втором выходе -последний п + 2-ой разряд полного регистра, образованного последовательным соединением двух D-триггеров 7 и 8, и регистра 5 сдвига.

На третьем выходе блока 2 синхронизации вьфабатываются импульсы с частотой

i

которые синхронизируют каждый четвертый разряд тетрады полного п + 2разрядного регистра. Количество двои ных разрядов регистра 5 сдвига выбирается из условия

п 4т - 2 , (3) где m - количество тетрад полного

регистра.

Блок 2 синхронизации вырабатывает на п -t- 2 выходах первой группы п + 2 последовательностей синхронизирующих импульсов, сдвинутых друг относительно друга на один период эталонной частоты f.

Каждый выход первой группы блока 2 синхронизации синхронизирует считывание с выхода регистра 5 соответствующего разряда двоично-десятичного кода.

Синхронизирующие импульсы разрядов с первой группы выходов блока 2 синхронизации поступают на входы десятичного клавишного устройства 16 блока 3 перестройки.

Клавишное устройство 16 состоит из m десятичных клавишных гребенок, каждая из которых содержит десять клавиш 0-9. Каждая клавишная гребёнка подключена к соответствующим четырем выходам первой группы выходов блока 2 синхронизации и имеет четыре выхода. Все 4т выходов всех m клавишных гребенок подключены к входам элемента 15 ИЛИ, выход которого является выходом блока 3 перестройки

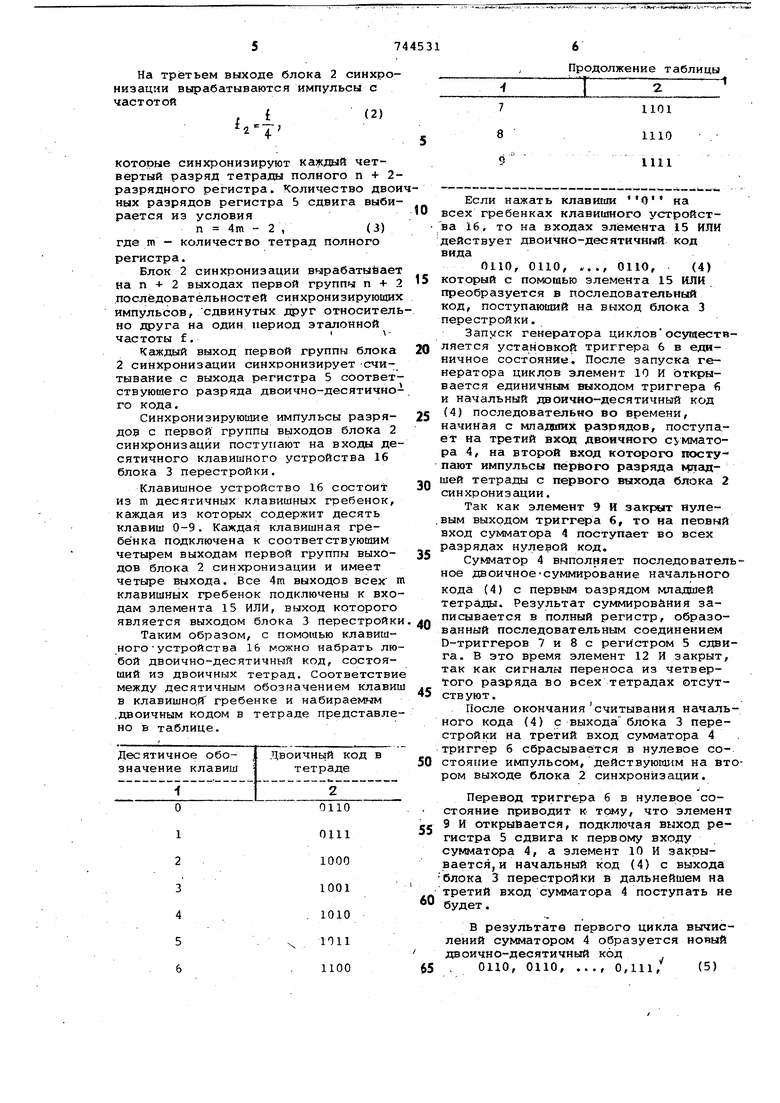

Таким образом, с помощью клавишного -устройства 16 можно набрать любой двоично-десятичный код, состоящий из двоичных тетрад. Соответствие между десятичным обозначением клавиш в клавишной гребенке и набираемым .двоичным кодом в тетраде представлено в таблице.

Продолжение таблицы

1111

Если нажать клавиши на

0 всех гребенках клавишного устройства 16, то на входах элемента 15 ИЛИ действует двоично-десятичный код вида

ОНО, ОНО, .. ., ОНО, (4)

5 который с помощью элемента 15 ИЛИ преобразуется в последовательный код, поступающий на выход блока 3 перестройки.

Запуск генератора цикловосуществляется установкой триггера 6 в еди0ничное состояние. После запуска генератора циклов элемент 10 И открывается единичным выходом триггера fi и начальный двоично-десятичный код (4) последовательно во времени,

5 начиная с младояих разрядов, поступает на третий вход двоичного сумматора 4, на второй вход которого поступают импульсы пёрйого разряда млгщшей тетрады с первого выхода блока 2

0 синхронизации.

Так как элемент 9 И закрыт нуле,вым выходом триггера 6, то на пеовый вход сумматора 4 поступает во всех разрядах нулевой код.

5

Сумматор 4 выполняет последовательное двоичное-суммирование начального кода (4) с первым оазрядом младшей тетрады. Результат суммирования записывается в полный регистр, образо0ванный последовательным соединением D-триггеров 7 и 8 с регистром 5 сдвига. В это время элемент 12 И закрыт, так как сигналы переноса из четвертого разряда во всех тетрадах отсут5ствуют.

После окончаниясчитывания начального кода (4) с выходаблока 3 перестройки на третий вход сумматора 4 триггер 6 сбрасывается в нулевое со50 импульсом, действующим на втором выходе блока 2 синхронизации.

Перевод триггера 6 в нулевое состояние приводит к тому, что элемент 9 И открыйается, подключая выход ре55гистра 5 сдвига к первому входу сумматора 4, а элемент 10 И закрывается, и начальный код (4) с выхода блока 3 перестройки в дальнейшем на третий вход сумматора 4 поступать не

60 будет.

В результате первого цикла вычислений сумматором 4 образуется новый двоично-десятичный код

(5)

ОНО, ОНО,

0,111,

65 который фиксируется в регистре сдвига 5 ... В следующем цикле вычислений двоично-десятичный код (5), считываемы с выхода регистра 5 сдвига, гфоссуммируется с первым разрядом младшей тетрады, поступающим на второй вход сумматора 4 с первого выхода блока 2 синхронизации. Результат суммирования ОНО, ОНО, .. ., 1000,(6) перепишется с выхода суммы сумматора 4 в регистр 5 и т..д. Так будет г одолжйться до тех пор йокане перепрлнится первая тетрада двоичйо-десятичного кода. Это произойдет в десятом цикле сложения содержимого регистра 5 сдвига с младшим разрядом первой тетрады, действующем на первом выходе блока. 2 синхронизации.И эт5м случае на выходе переноса сумматора 4 появится импульс переноса из четвертого разряда первой тетрады в первый разряд второй тетрады, который по синхронизируйюему импульсу с третьего выхода блока 2 синхрбниЗации через элемент,12 И поступит на вторые входы элементов 13 и 1 ИЛИ и восстановит начальный код ОНО в первой тетраде. Импульс переноса из четвертого разряда первой тетрады через элемент 12 И и 14 ИЛИ записывается в регистр 5 сйвйга fto ме.сту второго разряда первой тетрады и через элемент ИЛИ 1 спустя время задержки на один разряд в D-триггере 8 записывается по месту третьего разряда первой тетрады. Аналогичньви образом восстанавливается начальный код ОНО во ВТОРОЙ тетраде двоично-десятичного кода при переносе из четвертого разряда второй тетрады в первый разряд третьей тетрады и т.д. Выходной сигнал генератора циклов появится, когда сработает элемент 11 И. Это произойдет при переполнении последней т-ой тетрада двоично-Десятичного кода, считываемого, с выхода регистра 5-сдвига. В этом,случае импульс переноса из четвертого разряда т-ой тетрады по сйнхрбмйзируюшему импульсу четвертого разряда последней тетрады, поступйюгцёму со второго выхода блока 2 синхронизации, пройдет с выхода переноса сумматора 4 на выход эле мента 11 И и выход генератора циклов После генерации выходного сигнала триггер б установится этим сигналом в единичное.состояние. При этом закроется элемент 9 И, обеспечивая стирание содержимого регистра S сдви га, и откроется элемент 10 И, который подключит выход блока 3 перестройки к третьему входу сумматора для восстановления двоично-десятично го кода начальных условий (4), выставленного на клавишном устройстве 16. В следующем цикле генерации выходного сигнала генератор циклов работает аналогичным образом. На выходе risHepaTopa циклов вырабатываются импульсы с частотой с целью перестройки генератора циклов на частоту, отличную от частоты (7) , необходимо на клавишном устройстве 16 выставить новый десятичный код К, соответствующий эаданной частоте f. С учетом соотнесений (1) и (2) десятичный код К можно записать в виде .„ t, К 10--, (8) где f - частота эталонного генератора 1, m - количество десятичных ЪазряДов клавишного устройства 16. Если частбту эталонного генератора 1 выбрать из соотношения f 4m-10 Гц , (9) где р - целое число, то выраикение (В) для десятичного кода перестройки примет вид к 10 - Тд- 10 где Tg - заданный период следования выходных сигналов генератора циклов, с. Соотношение (10) позволяет непосредственно по заданному периоду следования выходных сигналов выстаг вить требуемый десятичный код перестройки на клавишном устройстве 16 без выполнения сложных расчетов. Диапазон перестройки генератора циклов на заданный период следования определяется соотношением 10 Тз (11) Предлагаемый генератор циклов может генерировать импульсные сигнаЛы в пределах диапазона (И) с любым заданным периодом следования выходных сигналов, который задаётся установкой десятичного кода перестройки (10) на клавишном устройстве 16. Рассмотрим процесс перестройки предлагаемого генератора циклов на примере в сравнении с известным. Требуется перестроить генератор циклов На :генёрироеаниё импульсов с заданным периодом следования T.j 14400c, Клавишное устройство 16 блока 3 перестройки m 10 десятичных разрядов, частота эталонного генератора 1 f 40-10 Гц, т.е. р 4. Диапазон перестройки генератора циклов 10 ci 10 с. 6 По формуле (10) получаем д сятич ный код перестройки К 10 -14400 10 9856000000, который с помощью четырех нажатий вы ставляется на клавишном устройстве блока 3 перестройки. В общем случае процесс перестрой ки предлагаемого генератора циклов требует выполнить одну операцию вычитания по формуле (10) для получения десятичного кода перестройки-и осуществить десять нажатий на клавишном устройстве 16 блока 3 перестройки. Расчет двоичного кода начальных условий для известного генератора циклов требует выполнить в общем сл чае О 32 операции вычитания с мно горазрядными десятичными числами и осуществить Е 32 нажатия двоичног клавишного устройства 16 блока 3 пе рестройки, где 6 - количество разря дов двоичного кода перестройки. Таким образом, процесс перестрой ки предлагаемого генератора циклов упрощается по количеству расчетных операций в 32 раза и по количеству ручных операций установки клавишного устройства блока перестройки в 3 раза. Дополнительные затраты оборудова ния на реализацию предлагаемого генератора циклов по сравнению с известным несущественны и составляют два D-триггера, два двухвходовых элемента ИЛИ и один двухвходовый элемент И. Формула изобретения Генератор циклов, содержащий генератор эталонной частоты, блок син хронизации, устройство ввода и элемент ИЛИ, сумматор и регистр сдвига первый, второй и третий элементы И триггер, причем выход регистра сдай га подсоединен.к первому входу первого элемента И, выход которого под ключен к первому входу сумматора, в рой вход Которого подсоединен к пер вому выходу блока синхронизации, вход которого подключен к выходу генератора эталонной частоты, третий вход сумматора связан с выходом второго элемента И, первый вход которого связан с выходом элемента ИЛИ, входы которого соединены с выходами устройства ввода, входы которого подсоединены к группе выходов блока синхронизации, второй вход второго элемента И подсоединен к прямому выходу триггера, инверсный выход которого связан с о вторым входом первого элемента И, выход блока синхронизации связан с нулевым входом триггера и с первым входом третьего элемента И, второй вход которого подсоединен к выходу переноса сумматора, а выход третьего элемента И подключен к единичному входу триггера и является выходом устройства отличаюиийс я тем, что, с целью упрощения перестройки устройства на заданную частоту, оно Йодёржит два D-триггера, первый и второй дополнительные элементы ИЛИ и четвертый элемент И, причем выход суммы сумматора подключен ко входу первого D-триггера, выход которого подключен к первому входу первого дополнительного элемента или, выход которого соединен со входом второго D-триггера, выход которого связан с первым входом второго дополнительг ного элемента ИЛИ, второй вход кото рого и первого дополнительного элемента ИЛИ соединены с выходом четвертого элемента И, первый вход которого подключен к выходу переноса cyNBviaTOpa, а второй вход подсоединен к третьему выходу блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №.485437, кл. G 06 F 1/02, 1972. 2.Авторское свидетельство-СССР № 291198, кл. G 06 F 1/02, 1969 (прототип).,

744531

ВыхоЪ

3-«jfo

Г

J I

El

э1

Авторы

Даты

1980-06-30—Публикация

1978-04-03—Подача