тельная погрешность преобразования не превышает заданного значения 2jНедостатками известного устройства аналого-ц-ифрового преобразования является то, что блок выделения старшей единицы вносит дополнительную задержку распространения, что снижает быстродействие.

Цель изобретения - повышение &аст.родействия параллельно-последовательного аналого-цифрового, преобразователя для сигналов с широким динамическим диапазоном.

Поставленная цель достигается тем что в параллельно-последовательный аналого-цифровой преобразователь, со держащий первый цифроаналоговый преобразователь, первую и вторую ступени компараторов, первый и второй делители напряжений, выходы которых поключены соответственно к первым входам компараторов соответствующей ступени, вторые входы которых соединены с шиной входного сигнала, а выходы второй ступени компараторов подключены к входам шифратора, первый и второй ВХОДЫ первого делителя напряжения соединены соответственно с общей шиной и с выходом источника опорного напряжения, первый вход второго делителя напряжения подключен к общей шине, введены второй цифроаналоговый преобразователь и сдвигатель кода, информационные входы которого .соединены соответственно с выходами шифратора и с выходом млад1иего компаратора первой ступени, а входы управления и входы перйого цифроаналогового преобразователя соединены соответственно с выходами компараторов первой ступени, начиная с второго компаратора, входы второго цифроаналогового преобразователя соединены соответственно с выходами компараторов первой ступени , а токо-вые выходы первого и второго цифроаналоговых преобразователей соединены соответственно с вторым и третьим входами второго делителя.

Кроме того, сдвигатель кода выполнен на логических элементах И, ИЛИ, запрета и инверторе, причем элементы И объединены в группы, число которых равно числу компараторов первой ступени, число элементов И в каждой группе равно числу информационных входов сдвигателя кода, число элементов запрета на единицу меньше числа компараторов первой ступени, при этом первые входы элементов И каждой группы объединены и соединены соответственно ,с выходом инвертора,. выходами элементов запрета и старшим входом управления сдвигателя кода, информационные входы подключены в каждой группе элементов И к вторым входам соответствующих номеру информационного входа элементов И, вхо инвертора соединен с первым входом .управления сдвигателя кода, первый и второй входы каждого элемента запрета соединены с соответствующим и последукяцим входами управления сдвигателя кода, выходная шина младшего разряда аналого-цифрового преобразователя подключена к выходу первого элемента И первой группы, выходная шина каждого последующего разряда, кроме старшего, подключена к выходу соответствующего элемента ИЛИ, вхо ды которого соединены с выходом первого элемента И группы элементов И, Iсоответствующей номеру разряда, и с выходами следующих по порядку элементов И предшествующих групп, а выходная шина старшего разряда подключена к выходу последнего элемента И старшей группы элементов И.

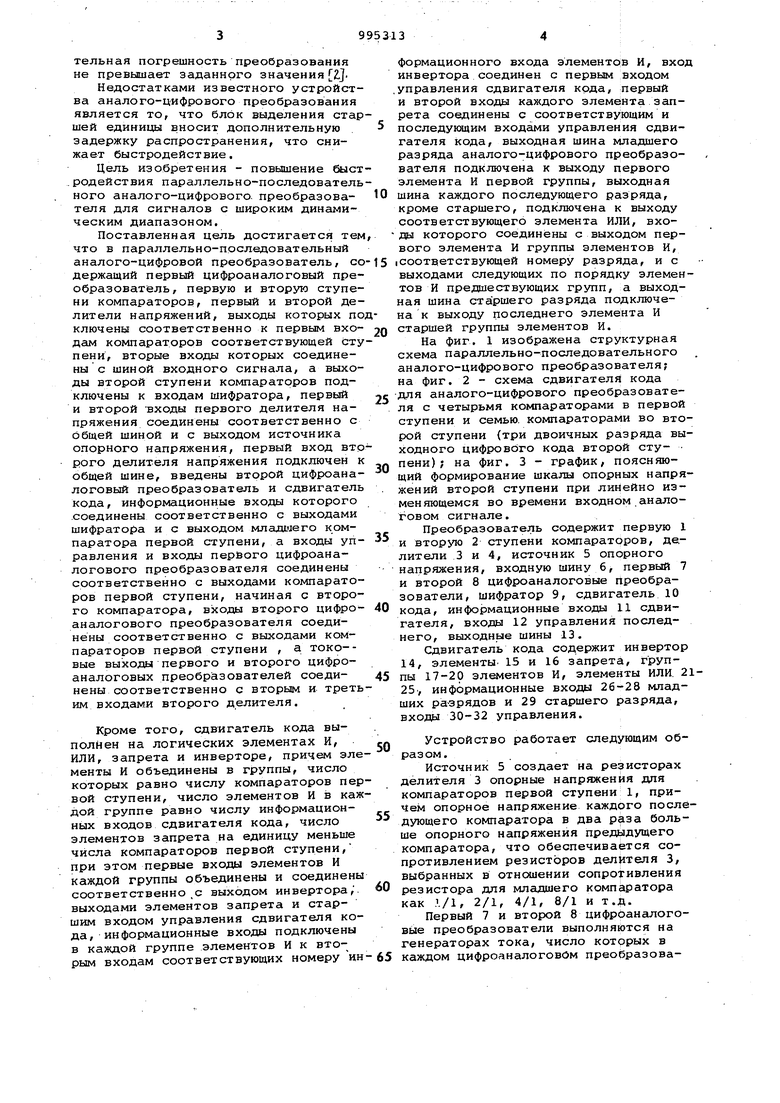

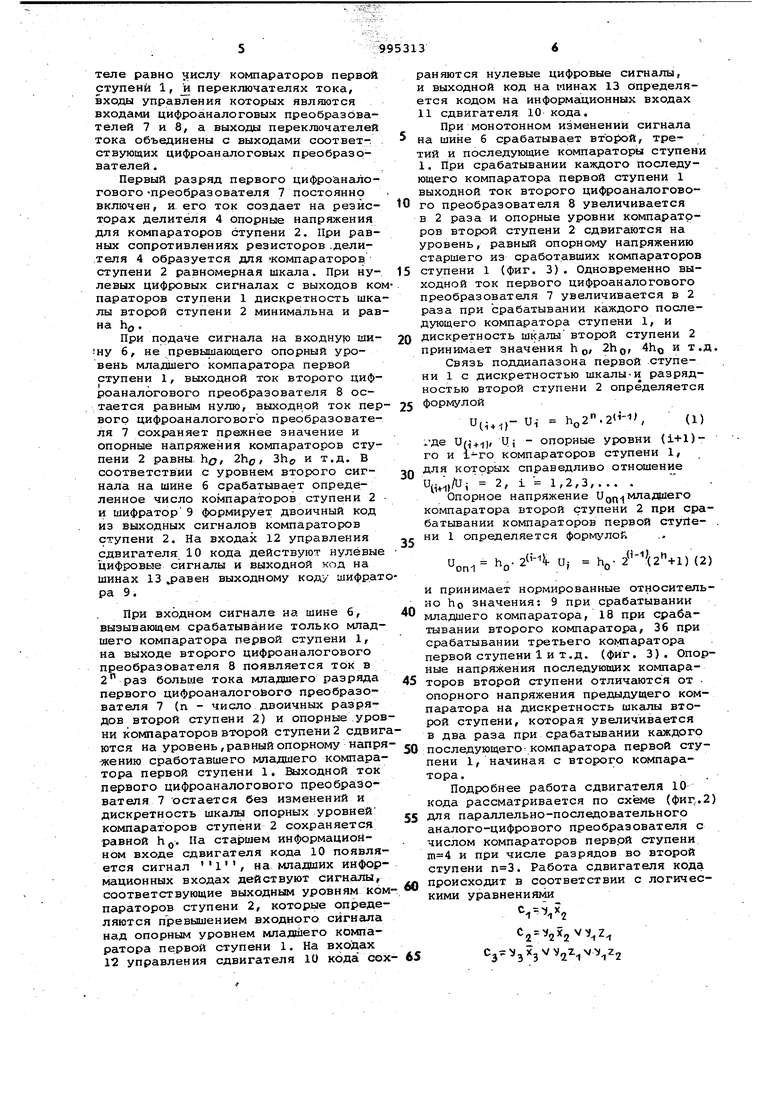

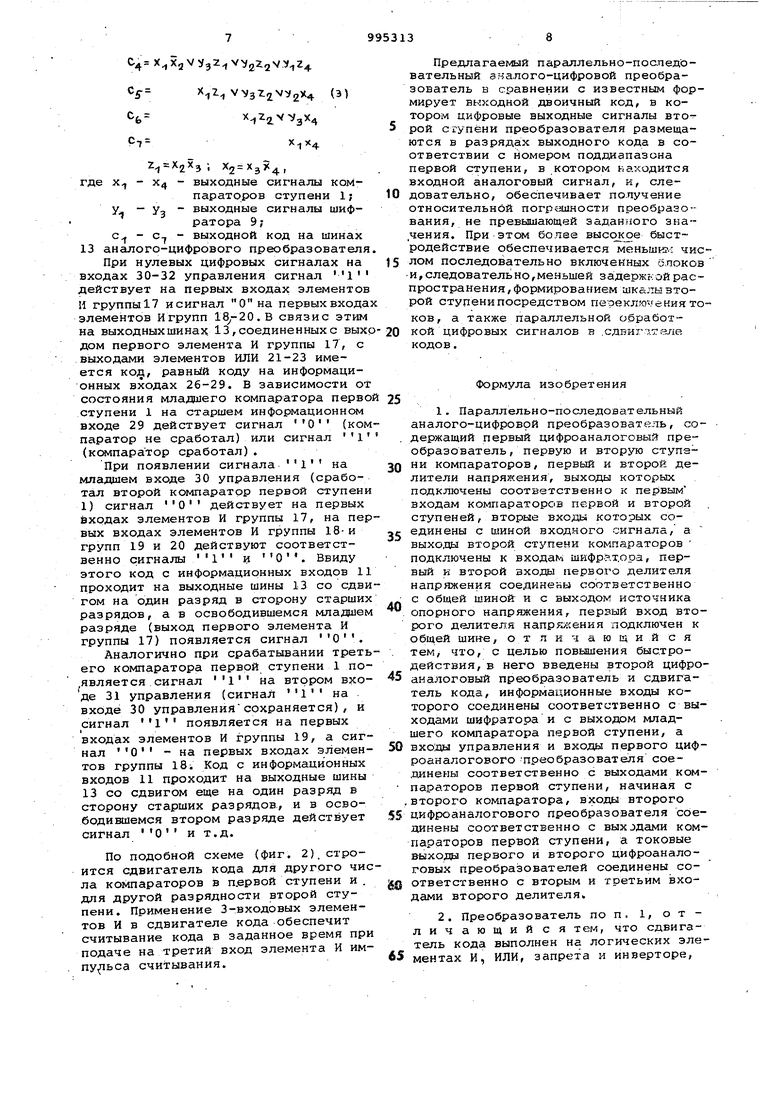

На фиг. 1 изображена структурная схема параллельно поспедовательного аналого-цифрового преобразователя; на фиг. 2 - схема сдвигателя кода для аналого-цифрового преобразователя с четырьмя компараторами в первой ступени и семью, компараторами во второй ступени (три двоичных разряда выходного цифрового кода второй сту- пени); на фиг. 3 - график, поясняющий формирование шкалы опорных напряжений второй ступени при линейно изменяющемся во времени входном ансшоговом сигнале.

Преобразователь содержит первую 1 и вторую 2 ступени компараторов, делители 3 и 4, источник 5 опорного напряжения, входную шину 6, первый 7 и второй 8 цифроаналоговые преобразователи, шифратор 9, сдвигатель 10 кода, информационные входы 11 сдвигателя, входы 12 управления последнего, выходные шины 13.

Сдвигатель кода содержит инвертор 14, элементы 15 и 16 запрета, группы 17-20 элементов И, элементы ИЛИ. 225 информационные входы 26-28 младших ра-зрядов и 29 старшего разряда, входы 30-32 управления.

Устройство работает следующим образом.

Источник 5 создает на резисторах делителя 3 опорные напряжения для компараторов первой ступени 1, причем опорное напряжение каждого последующего компаратора в два раза больше опорного напряжения предыдущего компаратора, что обеспечивается сопротивлением резисторов делителя 3, выбранных в отношении сопротивления резистора для младшего компаратора как .1./1, 2/1, 4/1, 8/1 и т.д.

Первый 7 и второй 8 цифроаналоговые преобразователи выполняются на генераторах тока/ число которых в каждом цифроаналоговйм преобразователе равно 1ислу компараторов первой ступени 1, и переключателях тока, входы управления которых являются входами цифроаналоговых преобразсэвателей 7 и 8, а выходы переключателей тока объединены с выходами соответ-т ствующих цифроаналоговых преобразователей ..

Первый разряд первого цифро&налогового-преобразователя 7 постоянно включен, и. его ток создает на резисторах делителя 4 опорные напряжения для компараторов ступени 2. При равных сопротивлениях резисторов .дели.теля 4 образуется для компараторов, ступени 2 равномерная шкала. При нулевых цифровых сигналах с выходов копараторов ступени 1 дискретность шкалы второй ступени 2 минимальна и равна h .

При подаче сигнала на входную ши:ну 6, не превышающего опорный уровень младшего компаратора первой ступени 1, выходной ток второго цифроаналогового преобразователя 8 остается равным нулю, выходной ток первого цифроаналогового преобразователя 7 сохраняет прежнее значение и опорные напряжения компараторов ступени 2 равны, ho, , 3hp и т.д. В соответствии с уровнем второго сигнала на шине 6 срабатывает определенное число компараторов ступени 2 и шифратор9 формирует двоичный код из выходных сигналов компараторов ступени 2. На входах 12 управления сдвигателя 10 кода действуют нулевые цифровые сигналы и выходной код на шинах 13 .равен выходному коду шифратра 9.

При входном сигнале на шине 6, вызывающем срабатывание только младшего компаратора первой ступени 1, на выходе второго цифроаналогового преобразователя 8 появляется ток в 2 раз больше тока младшего разряда первого цифроаналогобого преобразователя 7 (п - число двоичных разрядов второй ступени 2) и опорные уровни компараторов второй ступени 2 сдвигются на уровень, равный опорному напря-жению сработавшего младшего компаратора первой ступени 1. Выходной ток первого цифроаналогового преобразователя 7 остается без изменений и дискретность шкалы опорных уровней компараторов ступени 2 сохраняется равной hg. Па старшем информационном входе сдвигателя кода 10 появляется сигнал Ч , на младших информационных входах действуют сигналы, соответствующие выходным уровням компараторов ступени 2, которые определяются превышением входнрго сигнала над опорным уровнем младшего компаратора первой ступени 1. На входах 12 управления сдвигателя 10 кода сохраняются нулевые цифровые сигналы, и выходной код на шинах 13 определяется кодом на информационных входах 11 сдвигателя 10 кода.

При монотонном изменений сигнала

на шине 6 срабатывает второй, третий и последующие компараторы ступени 1. При срабатывании каждого последующего компаратора первой ступени 1 выходной ток второго цифроаналогового преобразователя 8 увеличивается в 2 раза и опорные уровни компаратрров второй ступени 2 сдвигаются на уровень, равный опорному напряжению старшего из сработавших компараторов

ступени 1 (фиг. 3). Одновременно выходной ток первого цифроаналогового преобразователя 7 увеличивается в 2 раза при срабатывании каждого последующего компаратора ступени 1, и

дискретность шкалы второй ступени 2 принимает значения h д, 2ho, 4hQ и т.д.

Связь поддиапазона первой .ступени 1 с дискретностью шкалыи разрядностью второй ступени 2 определяется

формулой

,,,- и, ho2.,(1)

.де и/|+), Uj - опорные уровни (i-(-l)го и х-го компараторов ступени 1, для которых справедливо отношение ,,/U 2, i 1,2,3,... .

Опорное напряжение Ugf,-( младше го компаратора второй ступени 2 при срабатывании компараторов первой CTyrte- . ни 1 определяется формулой

oni ho- Uf Ч ) (2)

и принимает нормированные относительно ho значения: 9 при срабатывании

младшего компаратора, 18 при срабатывании второго компаратора, 36 при срабатывании третьего компаратора первой ступени 1 и т.д. (фиг. 3). Опорные напряжения последующих компараторов второй ступени отличаются от опорного напряжения предыдущего компаратора на дискретность шкалы второй ступени, которая увеличивается в два раза при срабатывании каждого

последующего:компаратора первой ступени 1, начиная с второго компаратора.

Подробнее работа сдвигателя 10 кода рассматривается по схеме (фиг..2)

для параллельно-последовательного аналого-цифрового преобразователя с числом компараторов перврй ступени и при числе разрядов во второй ступени . Работа сдвигателя кода

происходит в соответствии с логическими уравнениями

C VjXjVV.Z

65 C X XaVy32 VV2Z2V fiZ , VV3Z2VV2X4 (Э) , vv-x ,X , где x - x - выходные сигналы компараторов ступени 1; у УЗ выходные сигналы шифратора 9; с - с - выходной код на шинах 13 аналого-цифрового преобразователя При нулевых цифровых сигналах на входах 30-32 управления сигнал Ч действует на первых входах элементов И группы17 исигнал первыхвхода элементов Игрупп 18,-20.В связис этим на выходныхшинах 13,соединенных с вых дом первого элемента И группы 17, с выходами элементов ИЛИ 21-23 имеется ко, равнЕлй коду на информационных входах 26-29. В зависимости от состояния младшего компаратора перво ступени 1 на старшем информационном входе 29 действует сигнал О (ком паратор не сработал) или сигнал ч (компаратор сработал). при появлении сигнала младшем входе 30 управления (сработал второй компаратор первой ступени 1) сигнал О действует на первых входах элементов И группы 17, на пер вых входах элементов И группы 18-и групп 19 и 20 действуют соответственно сигналы этого код с информационных входов 1 проходит на выходные шины 13 со сдви гом на один разряд в сторону старших разрядов, а в освободившемся младшем разряде (выход первого элемента И группы 17) появляется сигнал О. Аналогично при срабатывании треть его компаратора первой ступени 1 пона втором вхо,является сигнал де 31 управления (сигнал Ч на входе 30 управлениясохраняется), и появляется на первых сигнал входах элементов И группы 19, а сиг нал О - на первых входах элементов группы I8i Код с информационных входов 11 проходит на выходные шины 13 со сдвигом еще на один разряд в сторону старших разрядов, и в освободившемся втором разряде действует и т.д. сигнал По подобной схеме (фИг. 2). строится сдвигатель кода для другого чис ла компараторов в п.ервой ступени и для другой разрядности второй ступени. Применение 3-входовых элементов И в сдвигателе кода обеспечит считывание кода в заданное время при подаче на третий вход элемента И импу ьса считывания. Предлагаемый параллельно-поanедовательный аналого-цифровой преобразователь в сравнении с известным формирует выходной двоичный код, в котором цифровые выходные сигналы вто-г рой ступени преобразователя размещаются в разрядах выходного кода в соответствии с Номером поддиапазона первой ступени, в котором находится входной аналоговый сигнал, и, следовательно, обеспечивает получение относительной погрсаиности преобразования, не превышающей заданного зна,чения. При этом более выссжое быстродействие обеспечивается меньшга: числом последовательно включенных блоков и,следовательно,меньшей задержкой распространения , формированием шкалы второй ступени посредством переключения токов, а также параллельной обработкой цифровых сигналов в .сдвиг з.тале кодов. Формула изобретения 1.Параллельно-последовательный аналого-цифровой преобразователь, содержащий первый цифроаналоговый преобразователь, первую и вторую ступени компараторов, первый и второй делители напряжения, выходы которых подключены соответственно к первым входам компараторов первой и второй ступеней, вторые входы которых соединены с шиной входного сигнала, а выхо,цы второй ступени компараторов подключены к входам шифрат.ора, первый и второй входы первого делителя напряжения соединены соответственно с общей шиной и с выходом источника опорного напряжения, первый вход второго делителя напряжения подключен к общей шин-е, отличающийся тем, что, с целью повышения быстродействия, в него введены :второй цифроаналоговый преобразователь и сдвигатель кода, информационные входы которого соединены соответственно с выходами шифратора и с выходом младшего компаратора первой ступени, а входы управления и входы первого цифроаналогового -преобразователя сое.цинены соответственно с выходами компараторов первой ступени, начиная с второго компаратора, входы второго цифроаналогового преобразователя соединены соответственно с выходами компараторов первой ступени, а токовые выходы первого и второго цифроаналоговых преобразователей соединены соответственно с вторым и третьим входами второго делителя. 2.преобразователь по п. 1, от личающийся тем, что сдвигатель кода выполнен на логических элементах И, ИЛИ, запрета и инверторе.

причем элементы И объединены в группы, числокоторых равно числу ксмлпараторов первой ступени, число элементов И в каждой группе равно числу информационных входов сдвигателя кода, число элементов запрета на единицу меньше числа к.смпараторов первой ступени, при этом первые входы элементов И каждой группы объединены и соединены соответственно с выходом инвертора, выходами элементов запрета и старшим входом управления сдвигателя кода, информационные входы подключены в каждой группе элементов И к вторым входам соответствующих номеру информационного входа элементов И, вход, инвертора соединен с первым входом управления сдвигателя кода, первый и второй входы каждого элемента запрета соединены с соответствующим и последующим входами ;управления сдвигателя кода, выходная

шина младшего разряда ангшого- цифрового преобразователя подключена к выходу первого элемента И первой группы, входная шина каждого последующего разряда, кроме стаЕиаего, подключена к выходу -соответствующёго элемента:ИЛИ, входы которого соединены с выходом первого элемента И группы элементов и, соответствующей номеру разряда, и с выходами следующих по порядку элементов И предшествующих групп, а выходная шина старшего разряда подключена к выходу последнего элемента И старшей группы элементов И. .

15

Источники информации, принятые во внимание при экспертизе 1. AfeTopcKoe свидетельство рССР W 350160, кл. Н 03 К 13/17, 0.4.09.72. 2. Авторское свидетельство СССР

20 № 5S8628, кл. Н 03 ,К 13i/l7, 31.10.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжение-код | 1983 |

|

SU1403370A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1327290A1 |

| Многоканальный аналого-цифровой преобразователь | 1990 |

|

SU1835604A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1494218A2 |

13

Авторы

Даты

1983-02-07—Публикация

1980-07-09—Подача