К

14

Изобретение относится в; радиоэлектронике, измерительной технике, вы- |чйслительной технике.

I Цель изобретения - уг рощение и по- вьшение точности устройства.

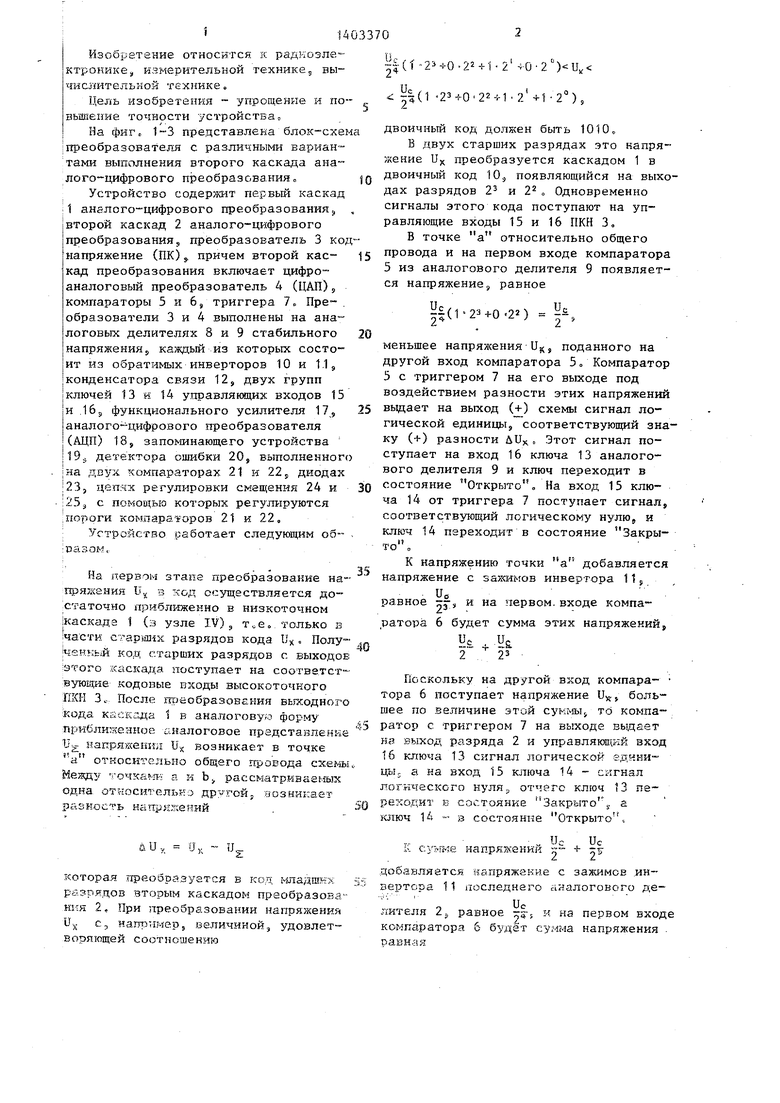

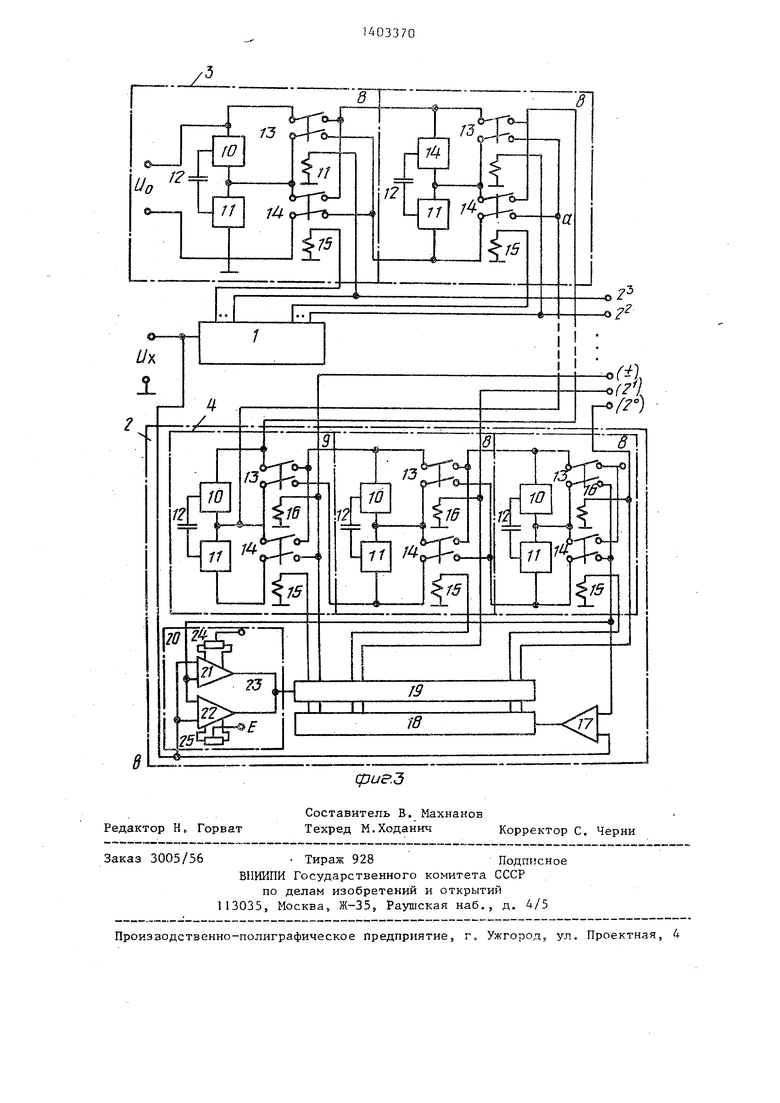

На фиг 1-3 представлена блок-схем I преобразователя с различными вариантами выполнения второго каскада ана лого-цифрового преобразования о

Устройство содержит первый каскад :1 аналого-цифрового преобразования I второй каскад 2 аналого-цифрового преобразованияS пр еобразователь 3 код напряжение (ПК) 5. причем второй кас- кад преобразования включает цифро- аналоговый преобразователь 4 (ЦАП), компараторы 5 и 6, триггера 7 Пре-. образователи 3 и 4 выполнены на аналоговых делителях 8 и 9 стабильного напряжения5 каждый из которых состоит нз обратимых инверторов 10 и llj конденсатора связи 12, двух групп Ключей 13 и 14 управляющих входов 15 |И ,165 функционального усилителя 17, Iаналого-цифрового преобразователя КАЦП) 18, запоминающего устройства 19s детектора ошибки 20, выполненног :на двух компараторах 21 и 22s диодах ;23j цепях регулировки смещения 24 и ;25э с помощью которых регулируются пороги компараторов 21 и 22, ; Устройство работает следующим об- :раЗОМс

На первом этапе гфеобразование напря7кения и.., 3 код осуществляется до- статочно приближенно в низкоточном каскаде 1 (з узле IV), т„е„. только в :части c-rapsfflix разрядов кода Ux Полу- |ч8нкь;й код старших разрядов с выходов этого KacKa ia поступает на соответст--- вующие кодовые входы высокоточного Л.КН 3.-. После преобразования выходного кода каскада 1 в аналоговую форму при6ли;кенное аналоговое представленне и«г напряже 1|-П1 U возникает в точке а откосигельно общего провода схемы Нежду точка ж а к Ь рассматриваекых одна относительно другой, возникает разность напрклсений

|(t 23-i-0.22 1-2 -i-0-2 )U ||(1 23-fO 22- r1.2-)-1-2°),,

двоичный код должен быть 1010

В двух старших разрядах это напряжение и, преобразуется каскадом 1 в двоичный код lOj появляющийся на выходах разрядов 2 и Одновременно сигналы этого кода поступают на управляющие входы 15 и 16 ПКН 3,

В точке а относительно общего провода и на первом входе компаратора 5 из аналогового делителя 9 появляется напряжение5 равное

|(1 23-f0.2M ,

меньшее напряжения Uj, поданного на другой вход компаратора 5 о Компаратор 5 с триггером 7 на его выходе под воздействием разности этих напряжений выдает на выход (+) схемы сигнал логической единицы, соответствующий знаку () разности uUx „ Этот сигнал поступает на вход 16 ключа 13 аналогового делителя 9 и ключ переходит в состояние Открыто На вход 15 ключа 14 от триггера 7 поступает сигнал, соответствующий логическому нулю, и ключ 14 пареходит в состояние Закры

К напряжению точки а добавляется напряжение с зажимов инвертора 11,.

. Ufi равное -J-5 и на первом, входе компа

ратора 6 будет сумма этих напряжений,

У Ц

2 . 23

Э

Поскольку на другой вход компара- тора 6 поступает напряжение U, большее по величине этой , то компаратор с триггером 7 на выходе вьщает на выход разряда 2 и управляютщй вход 16 ключа 13 сигнал логической еднни- ЦЫ; а на вход 15 ключа 14 - сигнал логнческого нуля,) отчего ключ t3 пе- рекодит в состояние Закрыто s а с«юч 14 - в состояние Открыто .

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Устройство для изготовления фотоформ | 1987 |

|

SU1454800A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1647895A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1462475A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

Изобретение относится к радио- электронике, измерительной технике, вычислительной технике. В двухкаскад- ном преобразователе напряжения в код,. состоящем, из первого каскада аналого- цифрового преобразования, преобразователя кода в напряжение и второго каскада аналого-цифрового преобразования, последний выполнен в виде высокоточного цифроаналогового преобразователя на обратимых инверторах с конденсаторами связи и ключами, образующими аналоговые делители стабиль-; ного напряжения. 3 з.п. ф-лы, 3 ил. с iS

aUv О,

и.

которая преобразуатся в код младших: разрядов вторым каскадом преобразова, нмя 2, При преобразовании напряжения Uj. с, например5 величиной, удовлетворяющей соотношению

суъте напряжении

+ УС 2

добавляется |{апряжекие с зажимов .инвертора 11 последнего а алогового о Uc

лителя Zj равное и на первом входе

ко паратора разная

о будет сумг-ia напряжения

УС

23

г Ч

Поскольку на другой вход компаратора 6 поступает напряжение, меньшее по величине этой суммы, то этот компаратор с триггером 7 на выходе выдает на выход разряда 2 сигнал логического нуля.

В результате описанных процессов на выходах 2, 2, (+), (2), (2°) схемы появляются соответственно сигналы 10+10 с учетом сигнала знака (+) ошибки, выходной код

1000

10

Т010

Однако в каскаде 1 на первом этапе возможна ошибка преобразования, равная одной дискрете младшего разряда, в связи с чем вместо представленного набора кода 10 на первом этапе может быть набран код 11 с допустимой ошиб- кой в одну дискрету младшего (второго разряда.

В таком случае описанный механизм преобразования приводит к появлению на выходах разрядов 2, 2, (+ , (2) (2°) других сигналов 11(-)0,1, соответствующих тому же коду 1010 величины U;, если учесть сигнал ошибки (-) и тоэ что 3Ha4ai4:ie цифры 01 кода для этого случая представлены в обратном коде1100 10

ТоТо

в отличие от схемы фиг. 1 второй каскад преобразования в схеме фиг. 2 содержит низкоточный аналого-цифровой преобразователь 18 и дифферен- циальньй усилитель 17.

Б этом варианте исполнения устрой- ство работает следующим образом.

Положим, что первьм низкоточным каскадом 1 осуществлено преобразование напряжения U в старшие разряды

кода с некоторой ошибкой. Поскольку кодовые выходы этого каскада соединены с кодовым входом старших ра.зря- дов высокоточного ПКН 3, то напряжение на выходе высокоточного ЦАП 4 будет прибш женно равным напряжению и,. Это напряжение поступает на один вход дифференциального усилителя 17, на другой вУ.оц которого подано напряжение Us,

g

Q 5

5

g

0

0

5

В результате между двумя этими входами дн(|)ференциального усилителя будет приложено разностное напряжение j представляющее ошибку преобразования в аналоговой форме.

Поскольку напряжение ошибки все же меньше по величине напряжения U,, то оно усиливается в необходимое число раз этим дифференциальным усилителем, а затем преобразуется низкоточным АЦП 18 в цифровой код, поступающий на кодовые входы высокоточного ПКНЗ, фop иpyющим младшие разряды кода. Этот цифровой код, преобразуясь в аналоговую форму, компенсирует напряжение ошибки на выходе высокоточного ЦАП 4 благодаря возникающей отрицательной обратной связи в контуре, включающем дифференциальный усилитель 17, низкоточный АЦП 18 и высокоточный ЦАП 4. Эта отрицательная обратная связь приводит к уменьшению напряжения ошибки на выходе высокоточного ПКН 3 до весьма малой величины, определяемой чувствительностью дифференциального усилителя„

Детектор ошибки представляет собой допусковую схему с тремя состояниями: ошибка равна (больше, меньше) допускаемой.Эти состояния устанавливаются путем смешения нулевого уровня компараторов 21 и 22 посредством цепей регулировки смешения нулевого уровня 24 и 25, подсоединенньй к источнику напряжения Е.

В момент достижения ош11бкой допустимой величины детектор ошибки (т.е. компараторы 21, 22) выдает на своем выходе сигнал ошибка равна допускаемой, которьш поступает на вход запрета запоминающего устройства 19 и тем самым разрывает цепь обратной связи, замыкающуюся через это запоминающее устройство.

Появляющийся на выходе детектора ошибки сигнал ошибка равна допускаемой используется для индикации достижения равновесия в схеме, а следовательно, и момента точного преобразования напряжения а сигналы ошибка больше (меньше) допускаемой могут быть использованы для запрета считьшания неустановившихся, ошибочных значений результируюпдсго кода с выходов 2, 2, (+},2,2 устройства в целом.

Формула изобретения

4, Преобразователь по пп, 2 и 3 отличающийся тем, что, цифроаналоговый преобразователь выполнен на последовательно соединенных т-аналоговых делителях стабильчающийся тем, что, с целью упрощения и повышения точности, дополнительный выход преобразователя кода в напряжение соединен с третьим входом второго каскада аналого-цифро- 25 ного напряжения по числу разрядов вого преобразования.цифроаналогового преобразователя,

2, Преобразователь по п. 1, о т - каждый из которых выполнен на двух л и ч а ю щ и и с я тем что второй обратимых инверторах, двух группах каскад аналого-цифрового щгеобразова- и конденсаторе связи, через ния выполнен на компараторахj тригге- ЗО который соединены импульсные входы

pax и цмфроаналогоЕом преобразователе j первый опорный вход которого является вторым В5Г.ОДОМ каскада,, объединен с. первым входом первого компаратора и й:влJзeтcя первым опорным выходом цифроаьгушгового преобразователя, второй йход первого компаратора и первые входы остальных рсомпаратороз объединены и являются первым входом каскада, вьгход каждого компаратора через соответствующий триггер подключен к цифровым входам соответствующего разряда цифроаналогового преобразователя второй опорный вход которого является третьим входом каскадад вторые входы компараторов, кроме первого компаратораj соединены с соот- зг тстзующи 5и опорны ми вьшодами, начиная с Бтсрого, цифроаналогового преобразователя причем один из цифровых входов кзлщого разряда 1ц-1фроана™ логового преобразователя является соотвегствую1дК1 1 младшим разрядом вы- .ходной п-разрядной шины.

Зо Преобразователь по п Ij от - л и ч а к щ и и с я тем,, что второй каскад аналого-цифрового преобразования выполнен на аналого -цифрозом преобразователе цифроаналоговом преобразодвух обратимых инверторов, входы по постоянному току которых являются входами соответствующего делителя стабильного напряжения, кроме перво

35 го 5 а выходы обратимых инверторов к дого делителя стабильного напряжени объединены и являются соответствующ опорным выходом цкфроаналогового пр образователя и подключены к информа

40 ционнь м входам первых ключей первой и второй группJ информационные вход вторых ключей которых объединены со ответственно с входами по постоянно току инверторов, выходы первого клю

45 ча первой группы и второго ключа вт рой группы объединены и являются па вым выходом fiHa.noroBoro делителя ст бильного напряжения, а выходы второ ключа :аервой группы и первого ключа

50 второй х руппы объединены и являются Еторьп- вьгходом аналогового делителя стабмпько1 о напряжения,, управляющие кходы ключей первой и второй групп я-е„ . яются цифровыГ Ш входаит соответ5 ; ствующего разряда цкфроаналогового преобразователя, вход по постсяином току первого обратимого инвертора п вого анзлогового делителя-стабильно го напряжения является вторым опорвателё и дифференциальном усилителе, первый вход которого является первым входом каскада, второй вход соединен с выходом цифроаналогового преобразователя, а выход подключен к входу аналого-и 1фрового преобразователя, выходы группы выходов которого соединены с соответствующими цифровыми входами соответствующих разрядов цифроаналогового преобразователя, первый и второй опорные входы которого являются соответственно вторым и третьим входами каскада, причем один из цифровых входов каждого разряда ц фpoaнaлoгoвoгo преобразователя является соответствующим младшим разрядом выходной п-разрядной шины.

4, Преобразователь по пп, 2 и 3, отличающийся тем, что, цифроаналоговый преобразователь выполнен на последовательно соединенных т-аналоговых делителях стабильного напряжения по числу разрядов цифроаналогового преобразователя,

двух обратимых инверторов, входы по постоянному току которых являются входами соответствующего делителя стабильного напряжения, кроме первого 5 а выходы обратимых инверторов каждого делителя стабильного напряжения объединены и являются соответствующим опорным выходом цкфроаналогового преобразователя и подключены к информационнь м входам первых ключей первой и второй группJ информационные входы вторых ключей которых объединены соответственно с входами по постоянному току инверторов, выходы первого клю-

ча первой группы и второго ключа второй группы объединены и являются пар вым выходом fiHa.noroBoro делителя стабильного напряжения, а выходы второго ключа :аервой группы и первого ключа

второй х руппы объединены и являются Еторьп- вьгходом аналогового делителя стабмпько1 о напряжения,, управляющие кходы ключей первой и второй групп я-е„ . яются цифровыГ Ш входаит соответствующего разряда цкфроаналогового преобразователя, вход по постсяиному току первого обратимого инвертора первого анзлогового делителя-стабильно- , го напряжения является вторым опор7 . U033708

ным входом цифроаналогового преобра- напряжения, а выходом цифроаналого- зрвателя, первым опорным входом ко- вого преобразователя является первый торого являются выходы обратимых ИИ- выход последнего аналогового делителя верторов первого делителя стабильного g стабильного напряжения.

фи.1

„.„..-..„J

Фиг..2

о-«

13

/у .JL

1 -г- tb

//

L

75

JrJI

Ux

JL

8

Щ

//9

Редактор H. Горват

дзиг.

Составитель В. Махнанов

Техред М.Ходанич Корректор С. Черни

8

8

/2

I

2- -o/

I

//9

| Электроника, 1979, № 10, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| Преобразователи информации для ЭЦВУ, М.: Мир, 1975, с | |||

| Способ изготовления фасонных резцов для зуборезных фрез | 1921 |

|

SU318A1 |

Авторы

Даты

1988-06-15—Публикация

1983-01-06—Подача