Изобретение относится к вычислительной технике и может быть использовано для управления режимами обмена и регенерации накопителей, имеющих ограниченное время хранения информации (например, выполненных на МДП-БИС).

Известно устройство для управления динамической памятью, содержащее формирователь синхронизирующих сигналов, формирователь сигналов регенерации и триггер режима 1 .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому является устройство для управления динамической памятью, содержащее формирователь синхронизирующих сигналов, формирователь сигналов регенерации, триггер режима, управляющую шину, триггер конца цикла, два элемента И-НЕ, выходы триггера режима соединены со входами первого элемента И-НЕ, выход которого соединен с входом формирователя синхронизирующих сигналов, входы триггера режима соединены соответственно с шиной управления и одним из вхо.цов второго элемента И-НЕ, с выходом того же элемента и выходом формирователя сигналов регенерации, другой вход второго элемента И-НЕ соединен с единичным выходом трипгера конца цикла, входы которого соединены соответственно с шиной управления и выходом формирователя синхронизирующих сигналов f2j.

Недостатком данного устройства является низкое быстродействие,

10 обусловленное дополнитёльньоми задержками выполнения обмена в случае поступления запроса на обмен с отстаиванием относительно запроса регенерации на время, не превышающее

15 время цикла накопителя.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство .для управления ди20намической памятью, содержащее формирователь синхронизирующих сигналов, триггеры, формирователь сигналов регенерации и элементы И-НЕ, причем выходы первого триггера соединены с

25 входами первого элемента И-НЕ, выход которого подключен к входу формирователя синхронизирующих сигналов, первый вход первого триггера соединен с первыми входами второго триг30гера и второго элемента И-НЕ, выход

которого подключен к второму входу первого триггера, а второй вход - к :выходу второго триггзра, первый вход которого является входом устройства, введены третий триггер, элементы ИЛИ, элемент И, элемент задержки и элемент ИЛИ-НЕ, первый вход которого соединен с вторым входом второго триггера и вы(ходом первого элемента ИЛИ, первый вход которого подключен к первому выходу первого триггера , а второй вход - к выходу формирователя синхронизирующих сигналов и первому входу второго элемента ИЛИ, второй вход которого соединен с вторьом выходом первого триггера, второй вход элемента ИЛИ-НЕ подключен к nepV вому выходу третьего триггера, второй выход которого соединен с входом элемента задержки и первым входом элемента И, второй вход которого подключен к выходу элемента задержки, а выход - к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход - с третьим .входом первого триггера, первый вход третьего триггера подключен к выходу формирователя сигналов регенерации, а второй в-ход - к выходу второго элемента ИЛИ.

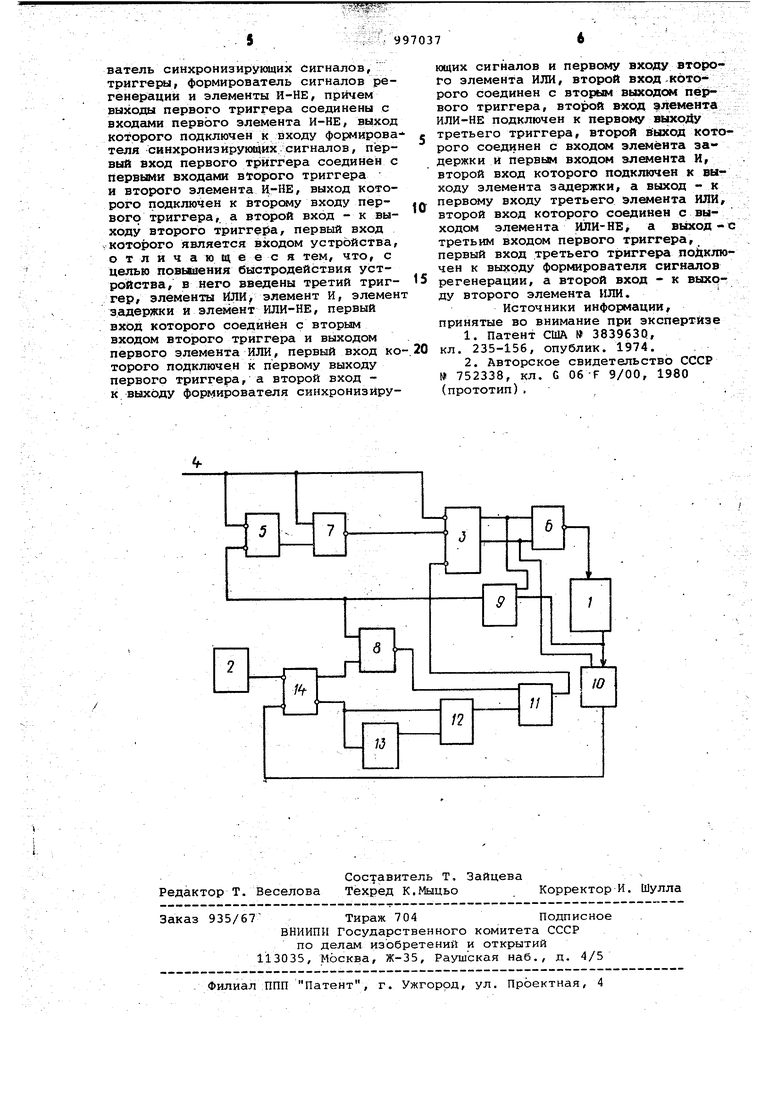

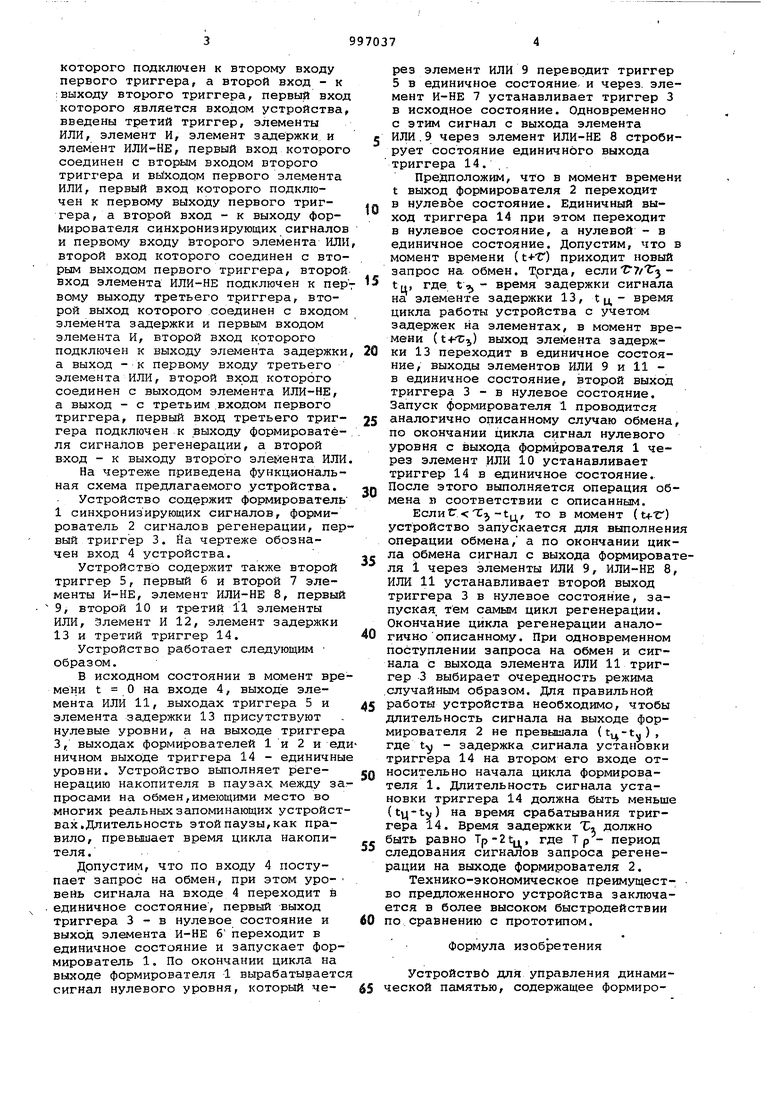

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит формирователь 1 синхронизирующих сигналов, формирователь 2 сигналов регенерации, первый триггер 3. На чертеже обозначен вход 4 устройства.

Устройство содержит также второй триггер 5, первый б и второй 7 элементы И-НЕ, элемент ИЛИ-НЕ 8, первый 9, второй 10 и третий 11 элементы ИЛИ, Элемент И 12, элемент задержки 13 и третий триггер 14.

Устройство работает следующим образом.

В исходном состоянии в момент времени t 0 на входе 4, выходе элемента ИЛИ 11, выходах триггера 5 и элемента задержки 13 присутствуют нулевые уровни, а на выходе триггера 3, выходах формирователей 1 и 2 и единичном выходе триггера 14 - единичные уровни. Устройство выполняет регенерацию накопителя в паузах между запросами на обмен,имеющими место во многих реальных запоминающих устройствах. Длительность этой паузы,как правило, превышает время цикла накопителя.

Допустим, что по входу 4 поступает запрос на обмен, при этом уро- вень сигнала на входе 4 переходит в . единичное состояние, первый выход триггера 3 - в нулевое состояние и выход элемента И-НЕ б переходит в единичное состояние и запускает формирователь 1. По окончании цикла на выходе формирователя 1 вырабатывается сигнал нулевого уровня, который через элемент ИЛИ 9 переводит триггер 5 в единичное состояние- и через, элемент И-НЕ 7 устанавливает триггер 3 в исходное состояние. Одновременно с этим сигнал с выхода элемента с ИЛИ.9 через элемент ИЛИ-НЕ 8 стробирует состояние единичного выхода триггера 14. ,.

Предположим, что в момент времени t выход формирователя 2 переходит

в нулевое состояние. Единичный выход триггера 14 при этом переходит в нулевое состояние, а нулевой - в единичное состояние. Допустим, что в момент времени (t+T) приходит новый запрос на обмен. , ecnHT 7/f y5 tj,, где t,, - время задержки сигнала на элементе задержки 13, t ц, - время цикла работы устройства с учетом задержек на элементах, в момент времени (t-f-C) выход элемента задерж0 ки 13 переходит в единичное состояние, выходы элементов ИЛИ 9 и 11 в единичное состояние, второй выход триггера 3 - в нулевое состояние. Запуск формирователя 1 проводится

5 аналогично описанному случаю обмена, по окончании цикла сигнал нулевого уровня с выхода формирователя 1 через элемент ИЛИ 10 устанавливает триггер 14 в единичное состояние..

Q После этого выполняется операция обмена в соответствии с описанным.

ЕслиГ Г,,-ty, то в момент (tftr) устройство запускается для выполнения операции обмена, а по окончании цик- ла обмена сигнал с выхода формировате ля 1 через элементы ИЛИ 9, ИЛИ-НЕ 8, ИЛИ 11 устанавливает второй выход триггера 3 в нулевое состояние, запуская, тем самым цикл регенерации. Окончание цикла регенерации анало0 гично описанному. При одновременном поступлении запроса на обмен и сигнала с выхода элемента ИЛИ 11 триггер 3 выбирает очередность режима .случайным образом. Для правильной

5 работы устройства необходимо, чтобы длительность сигнала на выходе формирователя 2 не превышала (), где t- - задержка сигнала установки триггера 14 на втором его входе отQ носительно начала цикла формирователя 1. Длительность сигнала установки триггера 14 должна быть меньше (ty-t) на время срабатывания триггера 14. Время задержки Т должно

быть равно Tp-Zti,, где Тр - период

следования сигналов запроса регенерации на выходе формирователя 2.

Технико-экономическое преимущество предложенного устройства заключается в более высоком быстродействии

0 по сравнению с прототипом.

Формула изобретения

Устройствб для управления динами5 ческой памятью, содержащее формирователь синхронизирующих сигналов, триггеры, формирователь сигналов регенераций и элементы И-НЕ, причем выходы первого триггера соединены с входсши первого элемента И-НЕ, выход которого подключен к входу формиррва теля синхронизирукицйх сигналов, nispвый вход первого триггера соединен с первыми входами второго триггера и второго элемента И-НЕ, выход которого подключен к второму входу первого триггера, а второй вход - к выходу второго триггера, первый вход .которого является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены третий триггер, элементы ИЛИ, элемент И, элемен задержки и элемент ИЛИ-НЕ, первый вход которого соединен с вторьам входом второго триггера и выходом первого элемента ИЛИ, первый вход ко торого подключен к первому выходу первого триггера, а второй вход к выходу формирователя синхрониэйруюсдих сигналов и первому входу второго элемента ИЛИ, второй вход-которого соединен с вторым выходом первого триггера, второй в-ход элемента ИЛИ-НЕ подключен к первому выходу третьего триггера, второй выход которого соединен с входом задержки и первым входом элемента И, второй вход которого подключен к выходу элемента задержки, а выход - к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход -с третьим входом первого триггера, первый вход третьего триггера пойключен к выходу формирователя сигнгшов регенерации, а второй вход - к выхрду второго элемента ИЖ. Источники информации, принятые во внимание при экспертизе 1.Патент США 383963Q, кл. 235-156, опублик. 1974. 2.Авторское свидетельство СССР 752338, кл. G 06-F 9/00, 1980 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1987 |

|

SU1471196A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Устройство для управления регенерацией в блоках оперативной памяти | 1980 |

|

SU942137A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для контроля магистралей ЭВМ | 1980 |

|

SU945868A1 |

| Устройство для регенерации информации в динамической памяти | 1981 |

|

SU1012346A1 |

| Многоканальное устройство сопряжения | 1976 |

|

SU679973A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

Авторы

Даты

1983-02-15—Публикация

1981-06-22—Подача