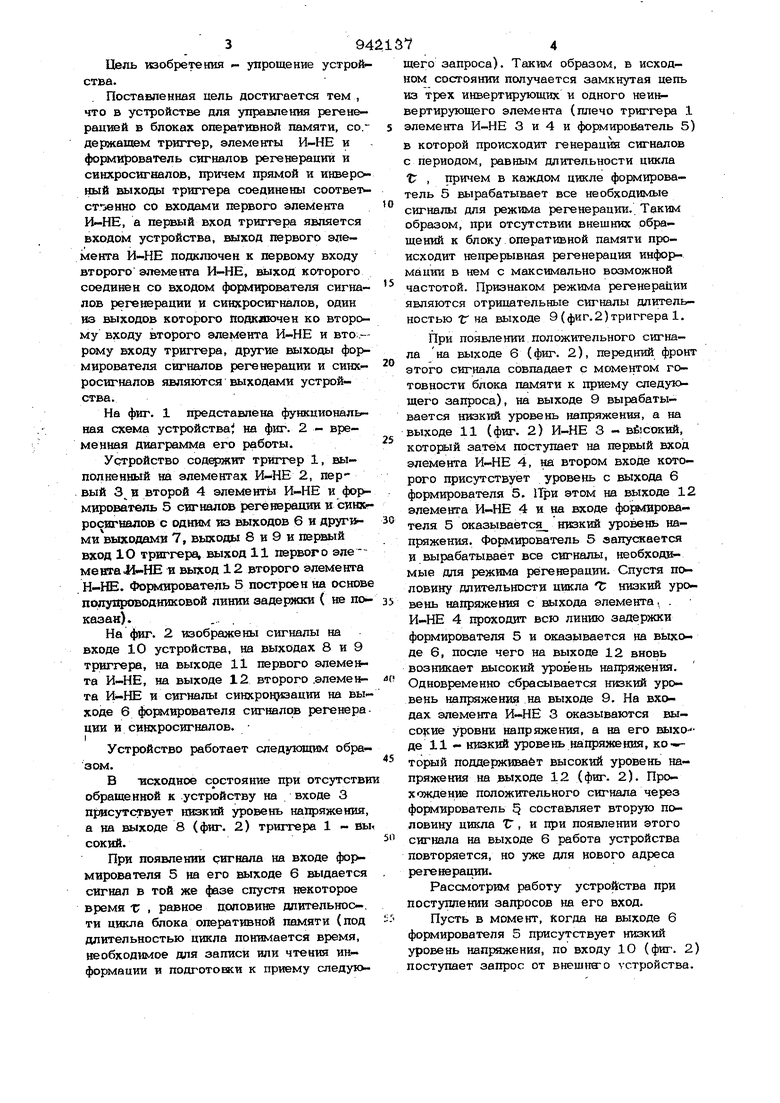

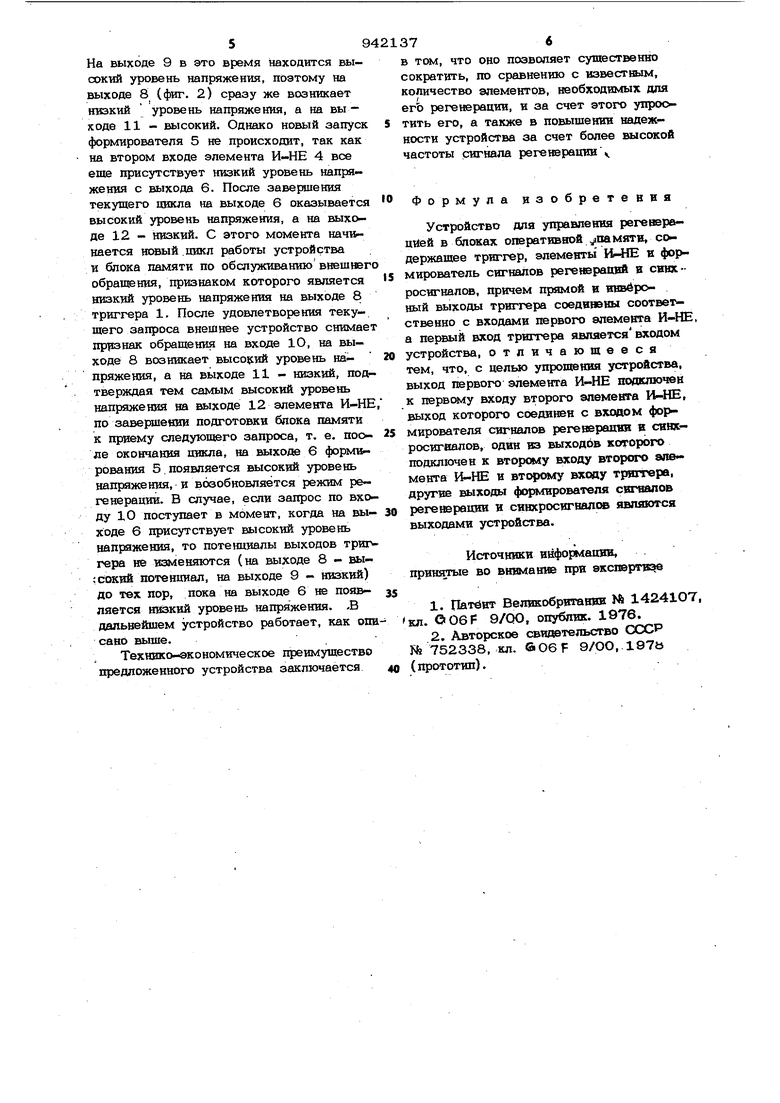

Изобретение относится к вычиспитепь технике va может быть использовано в качестве устройства местного управления оперативных накопителей, выполненных на элементахпамяти с ограниченным &ре менем хранения инфо{ыации. Известно устройство для управлешга регенерацией в блоках оперативной памар ти, содержащее формирователь сигналов регенерации, четыре одновибратора р&жима реГенераиии, четыре одновиб тора режима внешнего обращения, фо мвроеа- тель синхронизирующих сигналов, три и вертрра, два элемента 2И-НЕ и один элемент 4И-41Е 11. Недостаток устройства заключается в его сложности. Наиболее близким техническим решентюм к предлагаемому является уст ройство для управления регенерацией в блоках оперативной памяти, содержащее формирователь синхронизирующих сигна лов, формирователь сигналов регенерапии, триггер режима, управляющую шину, трипгер конца цикла и два элемента Й-НЕ, причем выхода, триггера режима соедине ны со входами первого элемента И-НЕ, выход которого соединен со входом фо1 мирователя синхронизирующих сигналов, входы триггера режима соединены соот ветственно с управляющей щиной и одним из входов второго элемента И-НЕ, с выходом того же элемента и выходом форм рователя сигналов регенерапии. Другой . вход второго элe 4гнтa И-НЕ соединен с единичным выходом триггера конца traK ла, входы которого соединены соответственно с управляющей шиной и выходом формирователя синхронизирующих СИГЕВлов f 2. Недостаток устройства - его спо ность, а также то, что при отсутствий обращенной по управляющей шине к запросов с формирователя сигналов регеюрвции, устройство не запускается и находится в выжидающем режиме, что сн жает его быстродействие. Цель кзобретеиия - упрощение устройства. . Поставленная цель достигается тем , что в устройстве для управления регене рацией в блоках оперативной памяти, сол держащем триггер, элементы и формирователь сигналов регенерации и синхросигналов, причем прямой и инверо ный выходы триггера соединены соответ cT-ieHHO со входами первого элемента И-НЕ, а первый вход триггера является входом устройства, выход первого элемента И-НЕ подключен к первому входу второго элемента И-НЕ, шлход которого соединен со входом формирователя сигна лов регенерации и синхросигналов, один из выходов которого Подключен ко второму входу второго элемента И-НЕ и вто .- рому входу триггера, другие выходы формирователя сигналов регенерации и синхросигналов являются выходами устройства. На фиг. 1 представлена функциональная схема устройства на фиг. 2 - временная диаграмма его работы. Устройство содержит триггер 1, выполненный на элементах И-НЕ 2, пер вый 3 и второй 4 элементы И-НЕ и формирователь 5 сигнале регенерации и синхг росвгшлов с одним из выходов 6 и другими выходами 7, выходы 8 и 9 и вход 1О триггера, выход 11 первого элемеврга JM-HE и выход 12 второго элемента Н-НЕ. Формирователь 5 построен на основе полупроводниковой линии задержки ( не показан).. . На фиг. 2 изображены сигналы на входе 10 устройства, на выходах 8 и 9 триггера, на выходе 11 первого элеме1ь. та И-НЕ, на выходе 12 второго .элемента И-НЕ и сигналы синхро1фэации на выходе б формирователя сигиалов регенерации и синхросигналов. I Устройство работает следующим образом. В исходное состояние при отсутстви обращенной к устройству на входе 3 присутствует низкий уровень напряжения, а на выходе 8 (фиг. 2) триггера 1 - вьи сокий. При появлении сигнала на входе формирователя 5 на его выходе 6 выдается сигнал в той же фазе спустя некоторое время t , равное половине длительное-, ти цикла блока оперативной памяти (под длительностью цикла понимается время, необходимое для записи или чтения информации и подготовки к приему следутощего запроса). Таким образом, в исходном состоянии получается замкнутая цепь из трех инвертирующих и одного не инвертирующего элемента (плечо триггера 1 элемента И-НЕ 3 и 4 к формирователь 5) в которой происходит генерация сигналов с периодом, равным длительности цикла tr , причем в каждом цикле формирователь 5 вырабатывает все необходимые сигналы для режима регенерации.. Таким образом, при отсутствии внешних обращений к блоку оперативной памяти происходит непрерывная регенерация информации в нем с максимально возможной частотой. Признаком режима регенерации являются отрицательные сигналы длительностью f на выходе 9 (фиг.2) триггера 1. При появлении положительного сигнала на выходе 6 (фиг. 2), передний фронт этого сигнала совпадает с моментом готовности блока памяти к приему следующего запроса), на выходе 9 вырабатывается низкий уровень напряжения, а на выходе 11 (фиг. 2) И-НЕ 3 - вбюокий, который затем поступает на первый вход элемента И-НЕ 4, на втором входе которого присутствует уровень с выхода 6 формирователя 5. 11фи этом на выходе 12 элемента И-НЕ 4 и на входе формирователя 5 оказывается низкий уровень напряжения. Формирователь 5 запускается и вырабатывает все сигналы, необходимые для режима регенерации. Спустя половину длительности цикла t низкий уровень напряжения с выхода элемента, . И-НЕ 4 проходит всю линию задержки формирователя 5 и оказывается на выхо де 6, после чего на выходе 12 вновь возникает высокий уровень напряжения. Одновременно сбрасывается низкий уровень напряжения на выходе 9. На входах элемента И-НЕ 3 оказываются высо сие уровни напряжения, а на его выхо--де 11 - низкий уровень напряжения, который поддерживает высокий уровень напряжения на выходе 12 (фиг. 2). Прохсиадение положительного сигнала через формирователь составляет вторую половину цикла tr, и при появлении этого сигнала на выходе б работа устройства повторяется, но уже для нового адреса регедарации. Рассмотрим работу устройства при поступлении запросов на его вход. Пусть в момент, когда на выходе б формирователя 5 присутствует низкий уровень напряжения, по входу 1О (фиг. 2) поступает запрос от внешня-о устройства. На выходе 9 в это время находится высокий уровень напряжения, поэтому на выходе 8 (фиг. 2) сразу же возникает низкий уровень напряжения, а на выходе 11 - высокий. Однако новый запуск формирователя 5 не происходит, так как на втором входе элемента И-НЕ 4 все еще присутствует низкий уровень напряжения с выхода 6. После завершения текущего цикла на выходе 6 оказывается высокий уровень напряжения, а на выходе 12 - низкий. С этого момента начинается нсдаый цикл работы устройства и блока памяти по обслуживанию внешнег обращения, признаком которого является низкий уровень напряжения на выходе 8 триггера 1. После удовлетворения текущего запроса внешнее устройство снимает признак обращения на входе Ю, на выходе 8 возникает уровень напряжения, а на выходе 11 - низкий, по/пь тверждая тем самым высокий уровень напряжения на выходе 12 элемента И-НЕ по завершении подготовки блока памяти к приему следующего запроса, т. е. пооле окончания цикла, на выходе 6 формирования 5.появляется высокий уровень напряжения, и возобновляется режим регенерации. В случае, если запрос по входу 10 поступает в момент, когда на вы- ходе 6 присутствует высокий уровень напряжения, то потенциалы выходов три гера не изменяются (на выходе 8 - вы:сокий потенциал, на выходе 9 - низкий) до тех пор, пока на выходе 6 не появляется нтакий уровень напряжения. .В дальнейшем устройство работает, как опв саво выше. Технико-экономическое преимущество предложенного устройства заключается в там, что оно позволяет существенно сократить, по сравнению с известным, количество элементов, необходимых для егЬ регенерации, и за счет этого упроотить его, а также в повыше mm надежности устройства за счет более высокой частоты сигнала регенерации Формула изобретения Устройство для управления регенерацией в блоках оперативной .jiUaMHTH, ct держащее триггер, элементы И-НЕ и фо{ мирователь сигналов регенераций и синхросигналов, причем прямой и инвёроный выходы триггера соединены соответственно с входами первого элемента И-НЕ, а пе{жый вход триггера является входом устройства, отличающееся тем, что, с целью упрощения устройства, выход первого элемента И-НЕ подключев к первому входу второгх элемента И-НЕ, выход которого соединен с входом формирователя сигналов регеверашш и синхросигналов, один из выходов которого подключен к второму входу второго ала- мента И-НЕ и второму входу триггера, другие выходы формирователя сигиапов perettepamra и синхросигналов являются выходами устройства. Источники информации, принятые во внимавиг при экспертизе 1.Цатёит Великобритании № 142410Т, кл. GO6F 9/QO, опублик. 1976. 2.Авторское свидетельство № 752338, кл. aO6F 9/ОО, 197b (прототип).

фуг. f

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Устройство для регенерации информации в динамической памяти | 1981 |

|

SU1012346A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОЙ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1994 |

|

RU2040809C1 |

| Устройство для управления регенерацией в полупроводниковой динамической памяти | 1991 |

|

SU1807521A1 |

| Устройство синхронизации памяти | 1982 |

|

SU1101805A1 |

| Устройство управления оперативной памятью | 1981 |

|

SU1051540A1 |

| Устройство для управления динамической памятью | 1981 |

|

SU997037A1 |

| Фотоэлектрическое считывающее устройство | 1988 |

|

SU1674181A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Авторы

Даты

1982-07-07—Публикация

1980-12-23—Подача