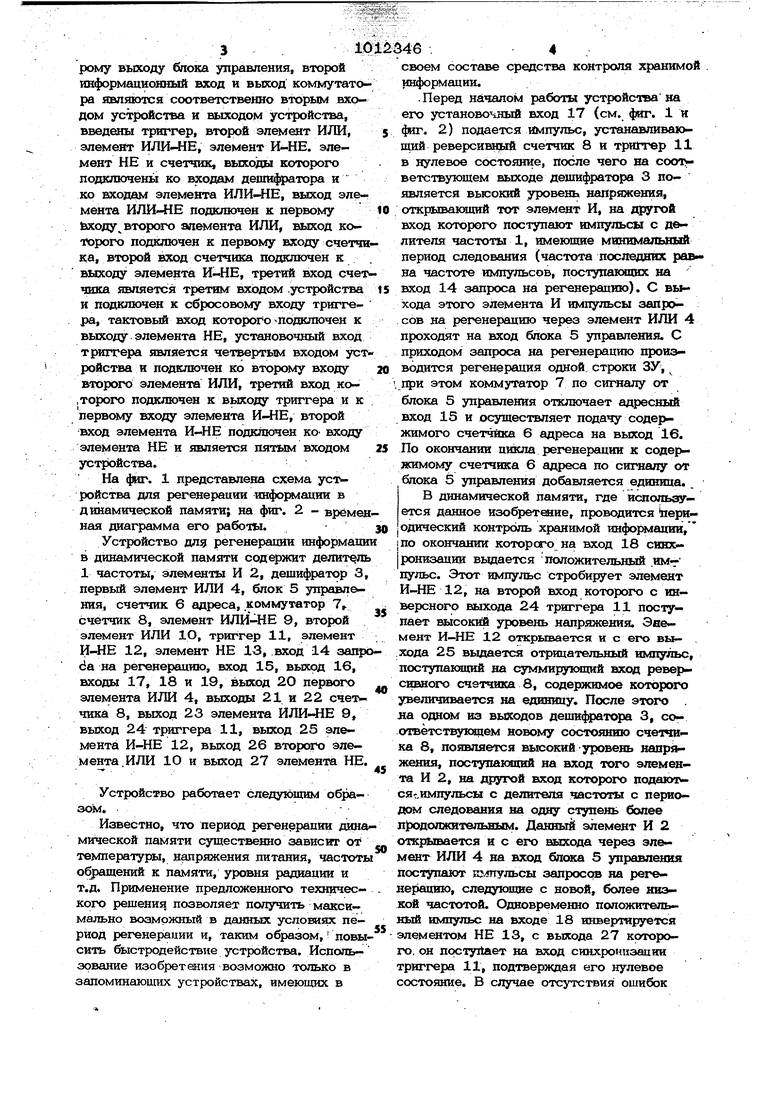

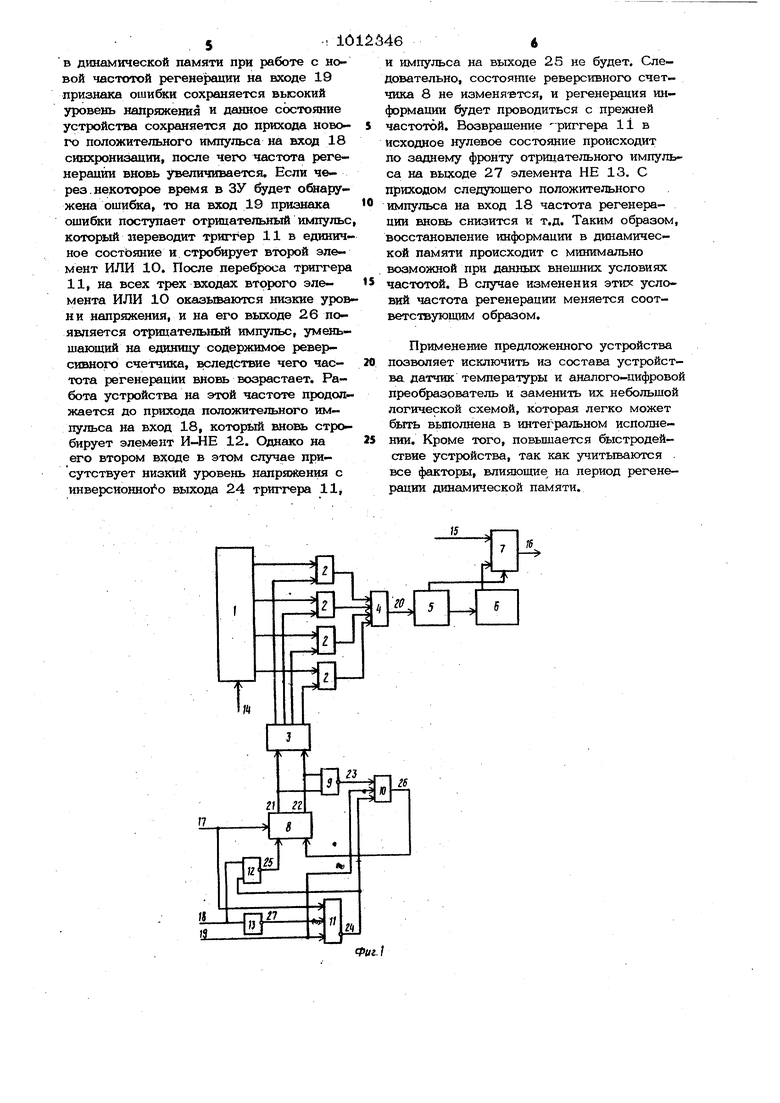

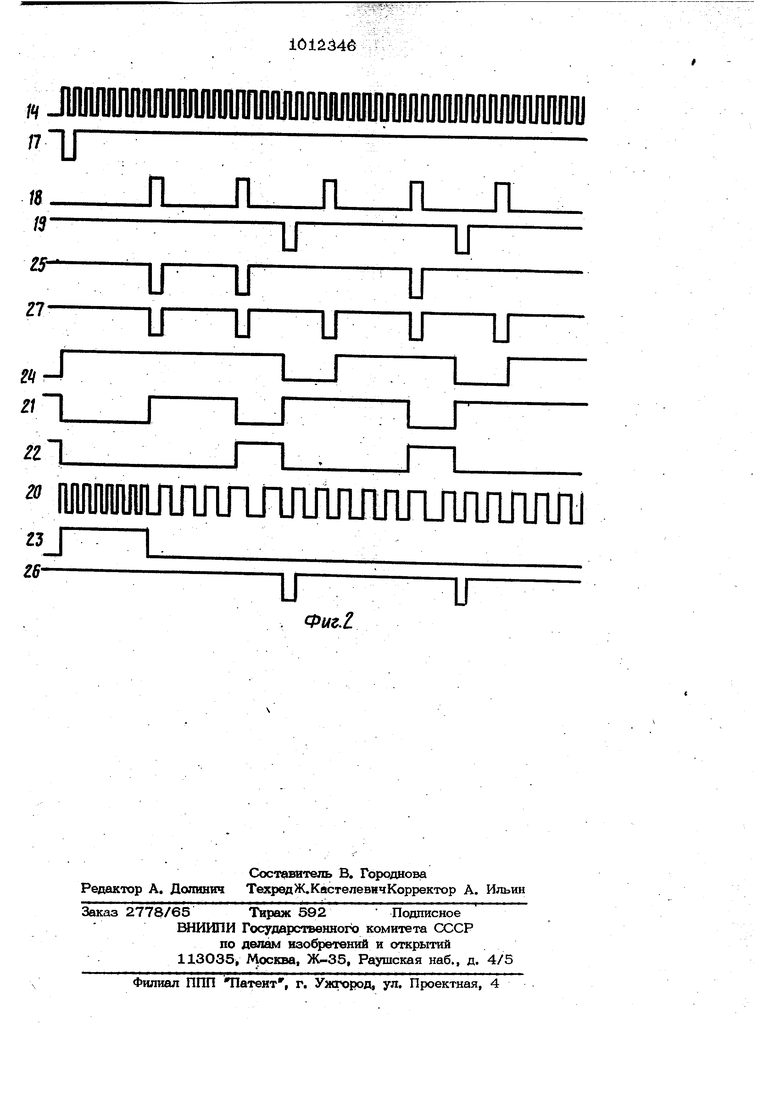

MaoejjeTemie относится к цифроэрй вычислител,ной технике и может б)ыть нспол ,овано в динамических запоминающих устройствах (ЗУ) со встроеншлм контре-, лем. Функционирование полупроводниковой динамической памяти основано периоди ческой регенерации хранимой информации. Организация этого режима требует.определенных затрат полезного времени и по. требляемой мощности, для уменьщения которых необходимо снижать число циклов регенерации, проводимых в единицу времени. Известно устройство для управления оперативной памятью, содержащее формирователь синхронизирующих сипшлов, формирователь сигналов регенерации, триггер конца шпсла, триггер режима и два элемента 2И-НЕ, причем выход формирователя синхронизирующих сигналов соединен со входом триггера конца цикла, выход которого соединен с первым входом первого элемента 2И-НЕ, второй вход которого соединен с первым входом триггера режима, с другим входом триггера конца цикла и со входом устройства, выход первого элемента 2И-НЕ соединен со вторым входом триггера режима, третий вход которого соединен с выходом формирователя регенерации, выходы триггера режима соединены со входами второго элемента 2И-НЕ, вых;од которого соединен со входом форми)рователя синхронизирующих сигналов. Режим регенерации в данном устройстве осуществляется по запросам с формирова теля сигналов регенерации, поступающим с фиксированной частотой, расчитанной на работу устройс:тва при максимально возможной температуре. Поскольку при снижении температуры частота: регенерации может бьпъ уменьшена, то устройст во проводит значительное «шсло лишних циклов регенерации, снижакшшх быстродействие и увеличивающих потребляемую мощность Наиболее близким техническим решением к изобретению 5шляется устройство для регенерации информации в данамичес кой памяти, содержащее входшью и выхо ные адресные шины, элемент пвмаегк, - блок управления, датчик температуры, аналого-Ш1фровой преобразователь, дещиф ратор, элементы И, делитель частоты, элемент ИЛИ, счетчик адреса и коммутатор адреса, причем первый выход блО( ка управления подключен ко входу-счетч чика адреса, выход которого подключен к одному из входов коммутатора адреса, другой вход которого подключен ко второму выходу блока управления, вход датчика температуры подключен к элементам памяти, вход аналого- :ифрового преобразователя подключен к выходу датчика температуры, вход дешифратора подключен к выходу аналого-41ифрового преобразователя, выходы которого подключены к одним из входов элементов И, другие входы которых подключены к соответствующим, выходам делителя частоты, вход которого является входом устройства, входь элемента ИЛИ подключены к выходам соответствующих элементов И, а выход - ко входу блока управления С 2 3 В этом устройстве датчик температуры формирует постоянное напряжение в соответствии с температурой нагрева элементов памяти. Аналого-цифровой преобразователь преобразовывает это напряжение в цифровой код, который дешифрируется дешифратором. При этом включается один из элементов И, на вход которого поступают импульсы запросов на регенерацию с частотой следования, соответствующей температуре нагрева элементов памяти. Через элемент . ИЛИ импульсы запросов на реге1юрацию поступают на вход блока управления. Таким образом, в устройстве осуществляется регулировка частоты следования запросов на регенерацшо в зависимости от температуры нагрева элементов памяти. Недостатком устройства для регенерации информации в динамической памяти является его сложность, определяемая наличием датчика температуры и аналогоцифрового преобразователя. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что устройство для регенерации информации в динамической памяти, содержащее делитель частоты, вход которого япвляется первым входом устройства, выходы делителя частоты подключены к первым входам элементов И, вторые входы которых подключены к выходам дешифратора, выходь элементов И подключены ко входам первого элемента ИЛИ, выход которого подключен ко входу блока управления, первый выход блока управления подключен ко входу счетчика адреса, выход которого подключен к первому информационному входу коммутатора, управляющий вход коммутатора подключен ко вто310рому выходу блока управления, второй информационный вход и выход коммутатора являются соответственно вторым входом устройства и выходом устройства, введены триггер, второй элемент ИЛИ, элемент ИЛИ-ЛЕ, элемент И-НЕ. элемент НЕ и счетчик, выходы которого подключены ко юсодам дешифратора и ко входам элемента ИЛИ-ЙЕ, выход элемента подключен к первому Ьходу второго зпемента ИЛИ, выход которого подключен к первому входу счетчи ка, второй вход счетчика подключен к выходу элемента И-НЕ, третий вход счет чика является тратим входом .устройства и подключен к сбросовому входу тркггера, тактовый вход которого подключен к выходу элемента НЕ, установочный вход триггера является четвертым входсяи устройства и подключен ко второму входу второго элемента ИЛИ, третий вход ко.торого подключен к выходу триггера и к первому входу элемента И-НЕ, второй вход элемента И-НЕ подключен ко- входу элемента НЕ и является пятым входом устройства. На фиг. 1 представлена схема устройства для регенерации информации в динамической памяти; на фиг. 2 - временная диаграмма его работы. Устройство ОД9 регенерации информации в динамической памяти содержит делитель 1 частоты, элементы И 2, деши4фатор 3, первый элемент ИЛИ 4, блок 5 управления, счетчик 6 адреса, коммутатор 7 счетчик 8, элемент ИЛИ-НЕ 9, второй элемент ИЛИ Ю, триггер 11, элемент И-НЕ 12, элемент НЕ 13, вход 14 запро da на регенерацию, вход 15, выход 16, входы 17, 18 и 19, выход 20 первого эпемеята ИЛИ 4, выходы 21 и 22 счетчика 8, выход 23 элемента ИЛИ-ЛЕ 9, выход 24 триггера 11, выход 25 элемента И-НЕ 12, выкод 26 второго элемента .И ЛИ 10 и выход 27 элемента НЕ. Устройство работает следу1бщим образом. Известно, что период регенерации дзинамической памяти существенно завис iw от температуры, напряжения питания, частоты обращений к памяти, уровня радиации и т.д. Применение предложенного технического решения позволяет получить максимально возможный в данных ycnoBHspc период регенерации и, таким образом, повысить быстродействие устройства. Исполь- зование изобретения возможно только в запоминающих устройствах, имеющих в 464 своем составе средства контроля хранимой информации. .Перед началом работы устройства на его установочный вход 17 (см. фипг. 1 и фиг. 2) подается импульс, устанавливающий реверсивш счетчик 8 и триггер 11 в нулевое состояние, после чего на соот ветствующем выходе дешифратора 3 по«шляется вьюокий уровень напряжения, открывающий тот элемент И, на другой вход которого поступают импульсы с делителя частоты 1, имеющие минимальный период следования (частота последних рав на частоте импульсов, поступаюошх на вход 14 запроса на регенерацию). С вькхода этого элемента И импульсы запро- сов на регенерацию через элемент ИЛИ 4 проходят на вход блока 5 управление С приходом запроса на регенерацию производится регенерация одной строки ЗУ, при этом коммутатор 7 по сигналу от блока 5 управления отключает адресный вход 15 и осуществляет подачу соде1 жимого счетчика 6 адреса на выход 16. По окончании цикла регенерации к содержимому счетчика 6 адреса по сигналу от блока 5 управления добавляется единица. В динамической памяти, где используется данное изобретение, проводится Апериодический контроль хранимой инфо|: дации, ino окончании которсго на вход 18 синх|ронизации вьщается положительный .им-г пульс. Этот импульс стробирует элемент И-НЕ 12, на второй вход которого с инверсногр выхода 24 триггера 11 nociyпает высокий уровень напряжения. Эяе- мент И-НЕ 12 открывается и с его выхода 25 вьщается отрицательный импульс, поступающий на суммирукнций вход реверсивнсмто счэтчшш 8, содержимое которого увеличивается на единицу. После этого ла одном из выходов дешифратора 3, соответствующем новому состоянию счетчика 8, появляется вьюокий-уровень напряжения, поступающий на вход того эпемекта И 2, на другой вход которого подаюо ся.импульсы с делителя частоты с периодом следования на одну ступень более л)родолжительным. Данный элемент И 2 открывается и с его выхода через элемент ИЛИ 4 на вход блока 5 управления поступают 1г.тульсы запросов на регенерацию, следующие с новой, более низкой частотой. Одновременно положительный импульс на входе 18 инвертируется элементом НЕ 13, с выхода 27 которого, он npciyilaeT на вход синхронизации триггера 11, подтверждая его нулевое состояние. В случае отсутствия ошибок 5: 10 в динамической памяти при работе с новой частотой регенерации на входе 19 признака ошибки сохраняется высокий уровень напр51жения и данное состояние устройства сохраняется до прихода нового положительного импульса на вход 18 синхронизации, после чего частота регенерации вновь увеличивается. Если через . некоторое время в ЗУ будет обнаружена ошибка, то на вход 19 признака ошибки поступает отрицательный импульс который а1ереводит триггер 11 в единичное состояние и стробирует второй элемент ИЛИ 10. После переброса триггера 11, на всех трех входах второго элемента ИЛИ 1О оказываются низкие уров ни напряжения, и на его выходе 26 появляется отрицательный импульс, уменьшающий на единицу содержимое реверсивного счетчика, вследствие чего частота регенерации вновь возрастает. Работа устройства на этой частоте продолжается до прихода положительного импульса на вход 18, который вновь стробирует элемент И-НЕ 12. Однако на его втором входе в этом случае присутствует низкий уровень напряжения с инверсионно1 о выхода 24 триггера 11, 46 и импульса на выходе 25 не будет. Следовательно, состояние реверсивного счетчика 8 не изменя-втся, и регенерация информации будет проводиться с прежней частотой. Возвращение -риггера 11 в исходное нулевое состояние происходит по заднему фронту отрицательного импульса на выходе 27 элемента НЕ 13. С приходом следующего положительного импульса на вход 18 частота регенерации вновь снизится и т.д. Таким образом, восстановление информации в динамической памяти происходит с минимально возможной при данных внешних условиях частотой. В случае изменения этих условий частота регенерации меняется соответствующим образом. Применение предложенного устройства позволяет исключить из состава устройства датчик температуры и аналого-цифровой преобразователь и заменить их небольшой логической схемой, которая легко может быть вьшолнена в интегральном исполнении. Кроме того, повьш1ается быстродействие устройства, так как учитываются . все факторы, влияющие на период регенерации динамической памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регенерации информации в динамической памяти | 1979 |

|

SU771728A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для регенерации информации | 1984 |

|

SU1238151A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1361615A1 |

УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ В ДИНАМИЧЕСКОЙ ПАМЯТИ, содержан|Ье делитель частоты, вход которого является первым входом устройства, выходы делителя частоты подключены к первым входам элементов И, вторые входы которьй подключены к выходам дешифратора, выходы элементов И подключены ко входам первого элемента ИЛИ, выход которого подключен к о входу блока управления, первый выход блока управления подключен ко входу счетчика адреса, выход которого подключен первому информационному входу комъ утатора, управляющий вход коммутатора подключен ко второму выходу блока управления, второй информационный вход н выход коммутатора являются со-г ответственно вторым входом и выходом устройства, отл. ичаЮщееся тем, что, с целью упрощения уст1Х йства, оно содержит триггер, второй элемент ИЛИ, элемент ИЛИ-НЕ, элемент И-НЕ, элемент НЕ и счетчик, выходы которого подключены ко входам дешифратора и входам элемента ИЛИ-НЕ, выход элемента ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ, выход которого подключен к первому входу счетчика,, второй вход счетчика подключен к выходу элемента. И-НЕ, третий вход счетчика является третьим входом устройства и подключен к сбросовому входу триггера, тактовый вход которого подключен к выходу элемента НЕ, установочный вход триггера является четвертым входе устройства rf подключен ко второму входу второго элемента ИЛИ, третий вход которого подключен к выходу тртптгера и к первому входу элемента И-НЕ, второй . вход элемента Й-НЕ подключен ко входу элемента НЕ и является пятым входом устройства.

шиишштгшл

j

Z6-

1Г

Фиг2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для регенерации информации в динамической памяти | 1979 |

|

SU771728A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-11—Подача