I Изобретение относится к вычислительной технике и может быть испол зовано в запоминающих устройствах, содержащих накопитель, выполненный на элементах памяти с ограниченным временем хранения информации (напри мер, динамическая память на элементах со структурой металл-диэлектрик-полупроводник) . Предлагаемое устройство может быть использовано в качестве устройства местного управления указанных накопителей. В одном из известных устройств установка режима регенерации производится по сигналам самого устройст для управления 1. Однако оно имеет сложную схему анализа запроса и выбора режима работы. Наиболее близким техническим решением к данному изобретению являет ся устройство для управления оперативной памятью, содержащее формирователь синхронизирующих сигналов, формирователь сигналов регенерации, выход которого соединен с первым вх дом триггера режима, второй вход ко торого подключен к одной из управляющих шин (2. Недостатком этого устройства являетсяналичие дополнительных шин управления, связывающих оперативную память с центральным процессором, по KOTophJM производится передача сигналов занятости оперативной памяти и команды установки режима регенерации либо обмена. Кроме того, в этом устройстве управления может возникнуть за,цержка запроса на входе оперативной памяти на время, превышающее период регенерации (например, при сбое в работе центрального процессора),при которой происходит разрушение информации в накопителе, т.е. данное устройство имеет недостаточную надежность . Цель изобретения - упрощение и повышение надежности устройства. Поставленная цель достигается тем, что устройство содержит триггер конца цикла и элементы И-НЕ, причем выходы триггера режима соединены со входами первого элемента И-НЕ, выход которого подключен ко входу формирователя синхронизирующих сигналов, третий вход триггера режима соединен с выходом второго элемента И-НЕ,входы которого подключены соответственно к управляющей шине и единичному выходу триггера конца цикла, входы которого соединены соответственно с выходом формирователя синхронизирующих сигналов ,и управляющей шиной.

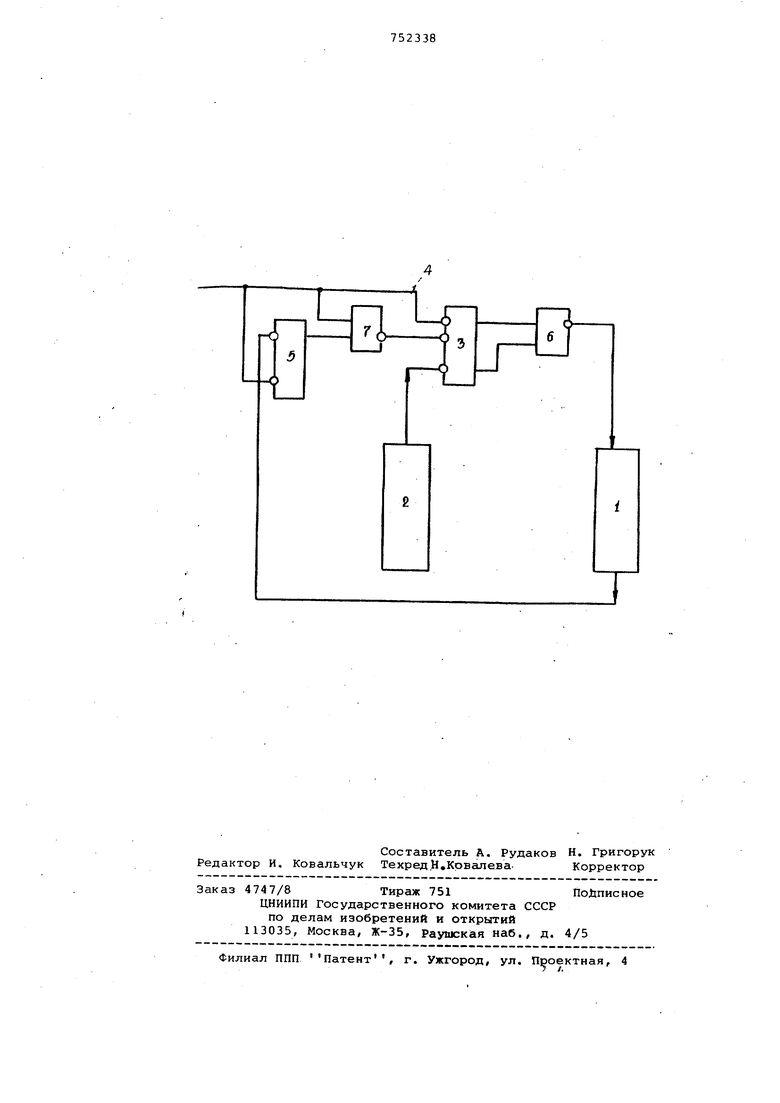

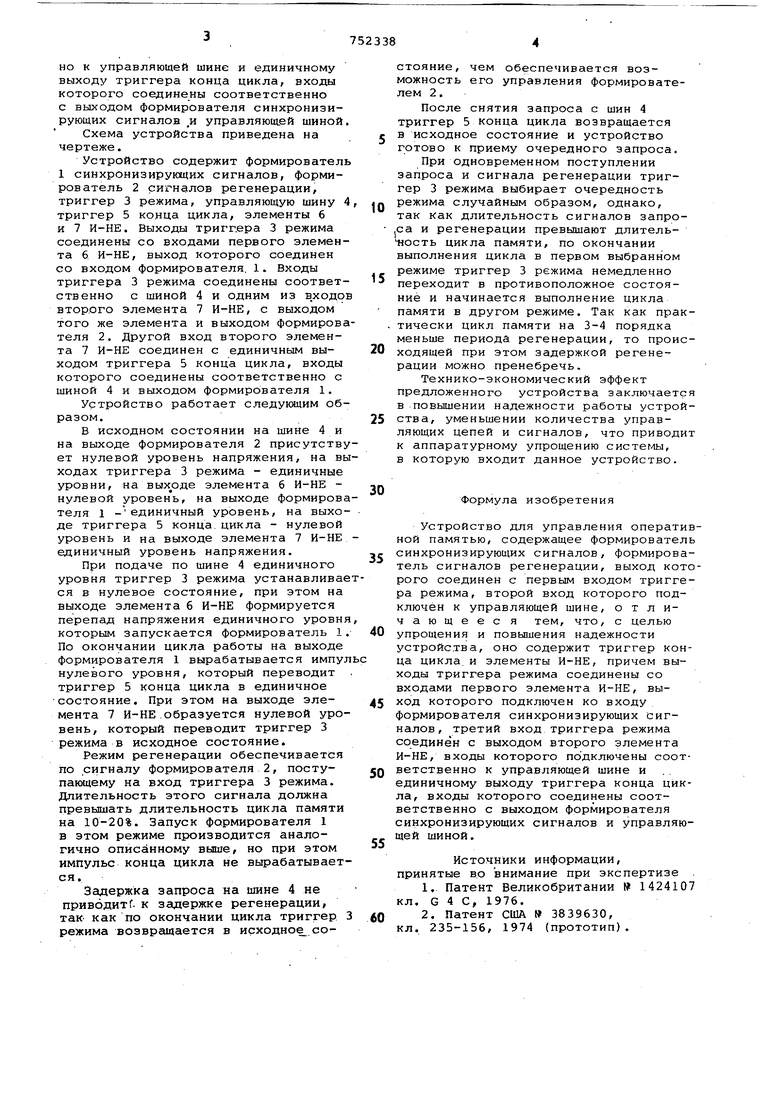

Схема устройства приведена на чертеже.

Устройство содержит формирователь 1 синхронизирующих сигналов, формирователь 2 сигналов регенерации, триггер 3 режима, управляющую шину 4 триггер 5 конца цикла, элементы 6 и 7 И-НЕ. Выходы триггера 3 режима соединены со входами первого элемента 6 И-НЕ, выход которого соединен со входом формирователя. 1. Входы триггера 3 режима соединены соответственно с шиной 4 и одним из в.ходов второго элемента 7 И-НЕ, с выходом того же элемента и выходом формирователя 2. Другой вход второго элемента 7 И-НЕ соединен с единичным выходом триггера 5 конца цикла, входы которого соединены соответственно с шиной 4 и выходом формирователя 1.

Устройство работает следующим образом.

В исходном состоянии на шине 4 и на выходе формирователя 2 присутствует нулевой уровень напряжения, на выходах триггера 3 режима - единичные уровни, на элемента б И-НЕ нулевой уровень, на выходе формирователя 1 -единичный уровень, на выходе триггера 5 конца.цикла - нулевой уровень и на выходе элемента 7 И-НЕ единичный уровень напряжения.

При подаче по шине 4 единичного уровня триггер 3 режима устанавливаеся в нулевое состояние, при этом на выходе элемента 6 И-НЕ формируется перепад напряжения единичного уровня которым запускается формирователь 1. По окончании цикла работы на выходе формирователя 1 вырабатывается импул нулевого уровня, который переводит триггер 5 конца цикла в единичное состояние. При этом на выходе элемента 7 И-НЕ.образуется нулевой уровень, который переводит триггер 3 режима в исходное состояние.

Режим регенерации обеспечивается по сигналу формирователя 2, поступающему на вход триггера 3 режима. Длительность этого сигнала должна превышать длительность цикла памяти на 10-20%. Запуск формирователя 1 в этом режиме производится аналогично описанному выше, но при этом импульс конца цикла не вырабатывается.

Задержка запроса на шине 4 не приводитf- к задержке регенерации, так как по окончании цикла триггер 3 режима возвращается в исходное состояние, чем обеспечивается возможность его управления формирователем 2.

После снятия запроса с шин 4 триггер 5 конца цикла возвращается в исходное состояние и устройство готово к приему очередного запроса.

При одновременном поступлении запроса и сигнала регенерации триггер 3 режима выбирает очередность режима случайным образом, однако, так как длительность сигналов запроСа и регенерации превышают длительяость цикла памяти, по окончании выполнения цикла в первом выбранном режиме триггер 3 режима немедленно переходит в противоположное состояние и начинается выполнение цикла памяти в другом режиме. Так как практически цикл памяти на 3-4 порядка меньше периода регенерации, то происходящей при этом задержкой регенерации можно пренебречь.

Технико-экономический эффект предложенного устройства заключается в повышении надежности работы устройства, уменьшении количества управляющих цепей и сигналов, что приводит к аппаратурному упрощению систеглы, в которую входит данное устройство.

Формула изобретения

Устройство для управления оперативной памятью, содержащее формирователь синхронизирующих сигналов, формирователь сигналов регенерации, выход которого соединен с первым входом триггера режима, второй вход которого подключен к управляющей шине, о т л ичающеес я тем, что, с целью упрощения и повьпиения надежности устройс.тва, оно содержит триггер конца цикла.и элементы И-НЕ, причем выходы триггера режима соединены со входами первого элемента И-НЕ, выход которого подключен ко входу формирователя синхронизирующих сигналов, третий вход триггера режима соединён с выходом второго элемента И-НЕ, входы которого подключены соответственно к управляющей шине и единичному выходу триггера конца цикла, входы которого соединены соответственно с выходом формирователя синхронизирующих сигналов и управляющей шиной.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании № 1424107 кл. G 4 С, 1976.

2.Патент США 3839630, кл. 235-156, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления оперативной памятью | 1981 |

|

SU1051540A1 |

| Устройство для управления регенерацией в блоках оперативной памяти | 1980 |

|

SU942137A1 |

| Устройство для управления динамической памятью | 1981 |

|

SU997037A1 |

| Устройство для управления регенерацией в полупроводниковой динамической памяти | 1991 |

|

SU1807521A1 |

| Устройство для регенерации информации в динамической памяти | 1981 |

|

SU1012346A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-27—Подача