(54 ) ИЗМЕРИТЕЛЬНАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для цифровой магнитной записи | 1989 |

|

SU1647634A2 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

Изобретение относится к эксперн- ментальной ядерной .физике и может быть, использовано в информационноизмерительных системах при .изучении механизмов протекания термоядерных реакций.

Известна измерительная система, содержащая аналого-цифровой преобразователь, включаюишй в себя входной усилитель и измерительный блок, и устройство для его управления, осуществляющее измере }ие интервгшов между замерами в зависимости от величины первой производной измеряемого . сигнала. Такое устройство позволяет сократить объем избыточной информации, передаваемой во внешнее запоминающее устройство измерительным (inoKOM аналогот-цифрового прербразователя за счет уменьшения числа замеров, когда входная величина меняется недостаточно 11.

Недостатками данной измерительной систекы являются неполное исключение числа избыточных замеров,а также невозможность воспроизведения по результатам измерения фор1«:1 измеряемого сигнала, так как время выполнения отдельных замеров неизвестно.

Известна измерительная система, содержащая аналого-цифровой преобра зоватёль, вход которого соединен с входной шиной устройства. Разрядные выходя анашого-цифрового преобразовагтеля соединены с входами устройства сравнения, выход управления и разрядные выходы которого соединены соответственно принятая выборка дан10ных ) с входами адреса и записи и с первой группой информационных входов запоминёиощего устройства, вторая группа информационных входов которого соединена с разрядными выхо-;

15 дами счётчику адреса (САК). Выходы адреса запои накнцего устройства соединены с входами устройства обнаружения запоминания памяти. Выход блока управления приемом данных сое20динен с. входом управления устройства сравнения, вход синхронизации которс го соеда нен с выходом синхронизатора и с входом счетчика адресов кангшов (синхронизация выборок).

25 Вход синхронизатора и вход управления аналого-цифрового преобразователя соединены с выходом генератора. Такое устройство с помощью устройств ва сравнения исключает повторякмцие30ся коды, последовательно поступающие с выхода аналого-цифрового преобразователя, и записывает в запоминающее устройство только значащие выборки вместе с их временной координатой , поступающей с выхода счетчика адресов каналов.

Требуемое быстродействие всех элементов устройства определяется тактовой частотой, вырабатываемой генератором, а объем запоминающего устройства - числом фиксируемых в нем за один цикл измерения значащих выборок, причем при высокой тактовой частоте, необходимой для обеспечения требуемой точности измерения формы сигнала, большую часть обмена памяти занимает адресная координата выборки t2.

Недостатком известной измерительной системы является ее низкая надежность, поскольку для обеспечения высокой точности измерений о.на требует быстродействующего многозарядного запоминающего устройства большого объема.

Цель изобретения - повышение надежности измерительной система.

Поставленная цель достигается тем, что в измерительную систему, содержащую аналого-цифровой преобразователь, разрядные выходы которого через блок сравнения соединены с первой группой информационных входов первого запоминающего устройства, входы записи и адреса которого соединены с выходом управления блока сравнения, вход управления которого соединен с выходом блока управления приемом данных, вход управления аналого-цифрового преобразователя соединен с выходом генератора и с . входом синхронизатора, выход которого соединен с входом синхронизации блока сравнения и с входом счетчика адреса, группа младших разрядов которого соединена с второй группой информационных входов первого запоминающего устройства, выходы адреса которого соединены с входами первого устройства обнаружения заполнения памяти, а первая и вторая группы выходов первого запоминающего устройства соединены соответственно с первой и второй группами выходных шин, введены второе запоминающее устройство, второе устройство обнаружения заполнения памяти, триггер, элемент ИЛИ, два элемента Зсщержки и три формирователя, причем выход старшего разряда группы, младших разрядов счетчика адреса через первый формиоователь соединен с первым входом триггера и с входом первого элемента задержки, выход которого через второй формирователь соединен с входом записи второго запоминающего устройства, информационные входы кото рого соединены с выходами группы

старших разрядов счетчика адреса, а выходы - с входами второго устройства обнаружения заполнения памяти, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого у ройства обнаружения заполнения памяти, выход - с входом блока управления приемом данных, выход управления блока сравнения через второй элемент задержки соединен с вторым входом триггера, выход которого сое динен с дополнительным информационным входом первого запоминающего устройства и через третий формирователь с входом адреса второго запоминающего устройства, выходы которого соединены с третьей группой выходных шин и с дополнительной выходной шиной устройства, при этом дополнительный выход первого запоминающего устройства соединен с дополнительной выходной шиной.

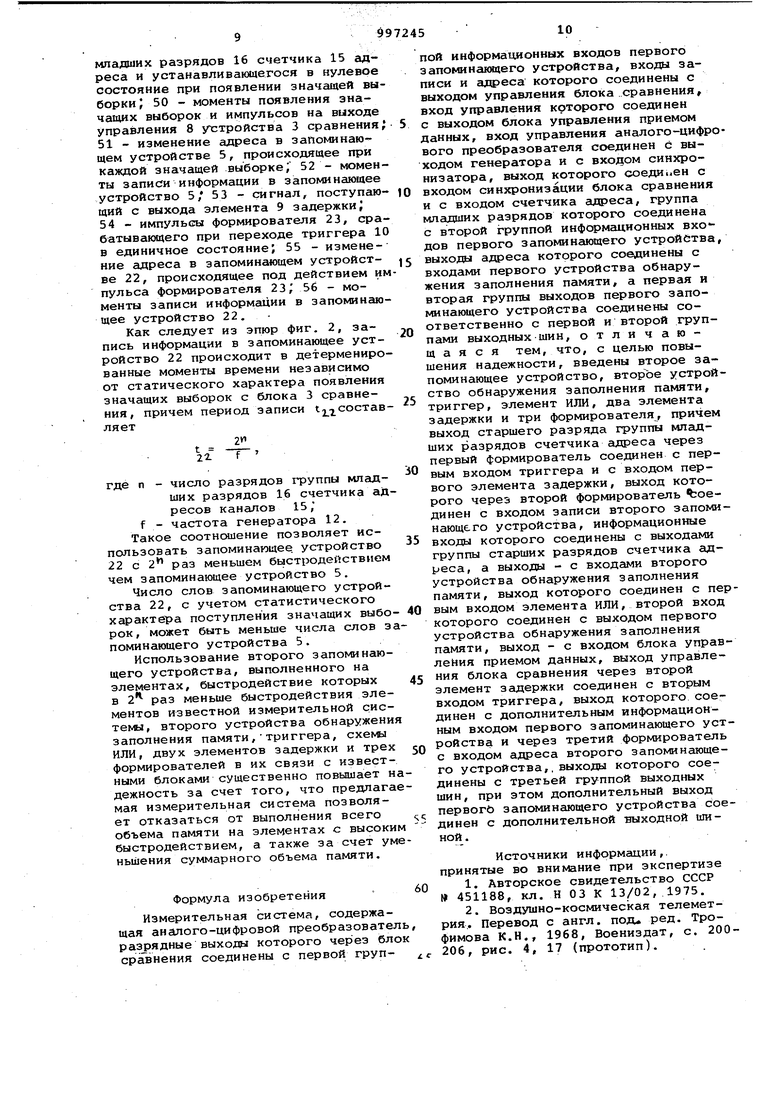

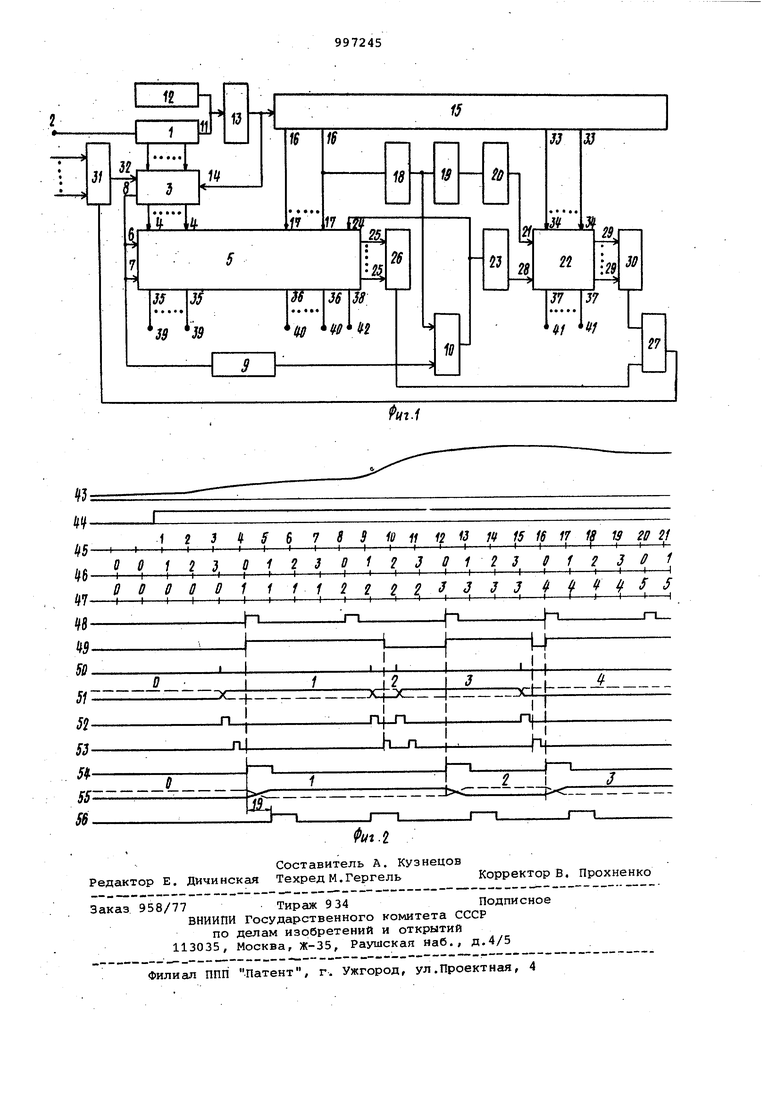

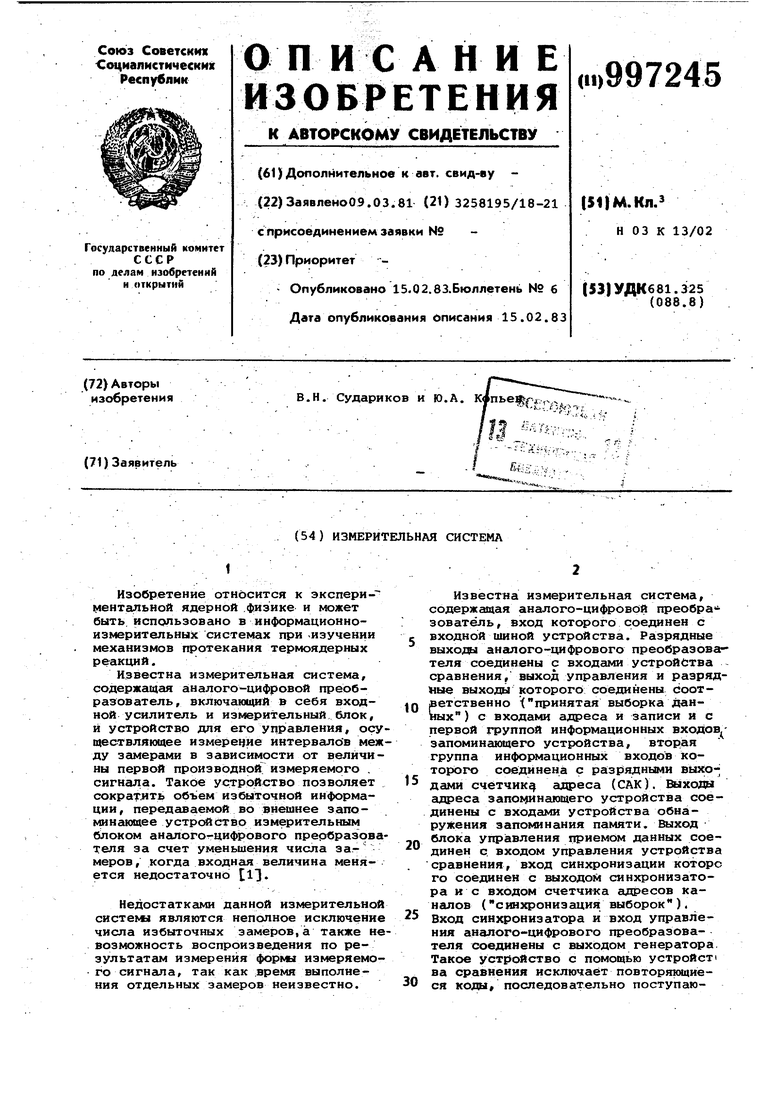

На фиг. 1 представлена структурная схема измерительной cHCTeNM, На фиг. 2 - временные графики, поясняющие ее работу.

Измерительная система содержит аналого-цифровой преобразователь 1, входную шину 2, блок 3 сравнения, иформационные входы 4, первое запоминающее устройство 5, вход записи 6, вход адреса 7, выход управления элемент 9 задержки, триггер 10, вхо управления 11, генератор 12, синхронизатор 13, вход синхронизации 14, счетчик 15 адреса, группу 16 младших разрядов, информационные вхды 17, первый формирователь 18, элемент задержки 19, второй формирователь 20, вход записи 21, второе запоминающее устройство 22, третий Фdpмирователь 23, дополнительный информационный вход 24, выходы адреса 25, первое устройство 26 обнаружения заполнения памяти, элемент ИЛИ 27, вход адреса 28,.выход адреса 29, второе устройство 30 обнаружения заполнения памяти, блок 31 упраления приемом данных, вход управления 32, группу 33 старших разрядов, информационные входы 34, группу выходов 35, группы выходов 36 и 37, дополнительный выход 38, группу выходных шин 39 - 41, дополнительную выходную шину 42.

При этом вход ан 1лого-цифрового преобразователя 1 соединен с входной шиной 2, а разрядные выходы с входами блока 3 сравнения, выходы которого соединены с группой информационных входов 4 запоминающего усройства 5, вход записи 6 и вход адреса 7 которого соединены с выходом управления 8 блока 3 сравнения и через элемент 9 задержки с вторым входом триггера 10. Вход управления 11 аналого-цифрового преобразователя 1

соединен с выходом генератора 12 и с входом синхронизатора 13,.выход кторого соединен с входом синхронизации 14 блока 3 сравнения и с входом счетчика 15 адреса. Группа 16 ,. младших разрядов счетчика 15 адреса соединена с группой информационных входов 17 запоминающего устройства 5. Выход старшего разряда группы 16 через формирователь 18 соединен с первым входом триггера 10 и с входом элемента задержки 19, выход которого формирователь 20 соединен с входом записи-21 запоминающего устройства 22. Выход триггера 10 соединен с входом формирователя 23 и с дополнительным информационным входом 24 запоминающего устройства 5, выходы адреса 25 которог соединены с входами устройства 26 обнаружения заполнения памяти, вых.од которого соединен с вторым входом элемента ИЛИ 27. Выход формирователя 23 соединен с входом адреса 28 запоминающего устройства 22, выходы сщреса 29 которого соединены с входами устройства 30 обнаружения заполнения памяти, выход которого соединен с первым входом элемента ИЛИ 27. Выход элемента ИЛИ 27 соединен с входом блока 31 управления приемом данных, выход которого соединен с входом управления 32 блока 3 сравнения. Группа старших разрядов 33 счетчика 15 адреса соединена с информационными входами 34 запоминающего устройства 22. Группа выходов 35 запоминающего устройства 5 соответствующая группе входов 4, группа выходов 36 запоминакнцего устройства 5, соответствующая групп входов 17, группа выходов 37 запоминающего устройства 22 и дополнительный выход 38 запоминающего устройства 5, соответствующий дополнительному информационному входу 24, соединена соответственно с группами выходных шин 39 - 41 и с дополнительной выходной шиной 42,

Измерительная система работает следующим образом. .

Перед началом измерения по внешней команде, поступающей на блок 31 управления приемом данных, последний с помощью входа управления 32 блокирует работу блока 3 сравнения. Запомингиощие устройства 5 к 22 устанавливаются внешними сигналами в исходные состояния и переводятся в режим записи.

По внешней команде, поступающей на блок 31 управления приемом данных, последний с помощью входа управления 32 разблокирует работу блока 3 сравнения и переводит измерительную систему в режим измерения.

В режиме измерения входной сигна поступает через входную шину 2 на

вход аналого-цифрового преобразователя 1, В момент прихода импульса с выхода генератора 12 на вход управления 11 аналого-цифрового преобразователя 1 последний выдает зарегистрированный им код величины входного сигнала на вход блока 3 сравнения. Импульсы генератора 12, пройдя через синхронизатор 13,,осуществляющий их временную трансформацию, поступает на вход счетчика 15 адреса, увеличивая всякий раз.его состояния на , единицу, и на вход синхронизации 1А, синхронизируя прием кода с аналогоцифрового преобразователя 1 блока 3

сравнения. Если код, полученный в данный момент времени блоком 3 срав-i нения, отличается от полученного им ранее, что соответствует появлению значащей выборки, блок 3 сравнения

передает значащий код на группу информационных входов 4 запоминающего устройства 5, на группу информационных входов 17 которого поступает информация с группы младших разрядов 16 счетчика 15 адреса. Вместе с тем на выходе управления 8 блока 3 сравнения вырабатывается импульс, поступающий на вход адреса 7 запоминающего устройства 5, изменяющий в нем адрес, а также поступающий на

его вход записи. 6 и осуществляющий запись в запоминающее устройство 5 по новому адресу величины сигнала с группы информационных входов 4 и младшую часть ее временного адреса с

группы информационных входов 17. Одновременно с дополнительного информационного входа 24 в дополнительный разряд запоминающего устройства 5 записывается состояние триггера 10.

с выхода 8 блока 3 сравнения импульс поступает через элемент 9 задержки на вход триггера 10, устанавливая его в нулевое состояние после записи информации в запоминающее устройство 5.

.При переполнении группы младших разрядов 16 счетчика адреса 15, от старшего разряда этой группы срабатывает формирователь 18, Импульс формирователя 18 устанавливает триггер 10 в состояние 1. При этом срабатывает формирователь 23, импульс которого поступает на вход адреса 28 запоминающего устройства 22 и устанавливает в нем новый адрес. Через время, определяемое элементом задержки 19, и необходимое для установки адреса, запускается формирователь 20. Импульс формирователя 20 поступает

на вход записи 21 запоминающего устройства 22, осуществляя запись по установленному в нем адресу состояния группы старших разрядов 33 счетчика 15 адреса, поступающего на информационные входы 34. В дальнейшем при отсутствии знач щих выборок и импульсов на выходе управления 8 устройства 3 сравнения по мере появления переполнений груп пы младших разрядов 16 счетчика 15 адреса . срабатывает формирователь 18, импульс которого.подтверждает единичное состояние- триггера 10 и, пройдя элемент задержки 19 и формирователь 20,. поступает на вход заПи си 21 запоминающего устройст ва-22. При этом в .запоминсцощее-устройство 22 всякий раз по одному и; тому же адресу, последовательно замещая дру друга, записывается .состояние группы старших разрядов 33 счетчика 15 адреса При появлении значащей выборки н выходе управления 8 блока 3 сравнения появляется импульс,осуществляющий записьвеличины сигнала- и младшей части адреса в запоминающее устройство 5. По.дополнительному ин формационному входу. 24 при этом записывается 1. Пройдя элемент 9 задержки, импульс с выхода управления 8 блока 3 сравнения после оконч ния записи в запоминающее устройство 5 срабатывает триггер 10 в нулевое состояние. В случае, когда за время между двумя, последовательными зна чащими выборками переполнения группы младших разрядов 16 счетчика 15 адреса не происходит, информация записывается только в запоминающее .устройст во.5, причем с дополнительного информационного входа 24 записываетСЯ О.: Таким образом, срабатывание форм рователя 18- и запись информации в запоминающее устройство 22 производит ся периодически при каждом переполн нии группы младших разрядов 16 счет чика 15 адресов, причем изменение адреса, предшествующее записи, производится только в случае, когда пе реполнению группы 16 младших разрядов предшествовало появление значащей выборки, записываемой в запоминающее устройство 5. Адрес, по которому производится .запись информации в запоминающее ус ройство 5 с выхода адреса 25, посту пает в устройство 26 обнаружения за полнения памяти , Адрес, по которому производится запись в запоминаю щее устройство 22, с выхода адреса 29 поступает в устройство обнаружения заполнения памяти 30. При запол йении одного из запоминающих устройств 5, 22 сигнал с выхода устройства заполнения памяти 26 или 30 через элемент ИЛИ 27 поступает на вход блока 31 управления приемом данных, который через вход управления 32 блокирует работу блока 3 сравнения и прекращает процесс изме рения. Внешняя команда, поступающая на блок управления приемом данных 31, подтверждает блокировку блока 3 сравнения, после чего запоминающие устройства 5 и 2,2 переводятся висходные состояния и устанавливаются в режим считывания,. Считывание, информации производится следующим образом. Информация, считанная по первому адресу запоминающего устройства 5 с группы выходных шин 39, соответствует первому значению величины измеряемого сигнала А..Информация, считанная по этому же .адресу с группы выходнйх шин 40;, соответствует младшим разрядам временного адреса. Если с дополнительной выходной шины 42 при этом считан.О, то старшие разряды временного адреса берутся из предыдущего считывания при считывании первой, выборки принима1ются равными нулю). Если с дополнительной выходной шины считана 1, то старшие разряды временного адреса данной значащей выборки считываются с выходных шин 41 по.первому адресу запоминающего устройства 22. Затем адрес в запоминающем устройст- ве 5 увеличивается на 1, а если производилось считывание информации с выходцых цдан 41,- то увелич.ивается и адрес в запоминающем устройстве 22. Аналогичным образом производится считывание информации из запоминающих устройств 5 и 22 до извлечения всех з.начащих выборок,. количество которых ограничивается объемом запоминающих устройств 5 и 22. Временная диаграмма, иллюстрирующая работу устройства, в режиме измерения приведена на фиг. 2 (43-56), где 43 - измеряе№1Й входной- сигнал, поступающий на входную шину 2; 44 поступление по внешней команде с блока управления.приемом данных 31 на вход управления 32 блока 3 сравнения разрешающего сигнала, начинающего процесс измеренияf 45 - моменты поступлёни.я синхроимпульсов с выхода генератора 12 и появления кодов На выходах аналого-цифрового преобразователя 1; 46 - изменение млад ших разрядов 16 счетчика 15 адреса для случая, когда группа 16 содер|жит два разряда величина необходимой задпржки относительно импульсов генератора 12. обеспечивается синхронизатором 13); 47 - изменение старших разрядов 33.счетчика адреса 15, 48 - импульсы формирователя 18, срабатывгиощего при каждом переполнении младших разрядов 16 счетчика 15 адреса, 49 - изменение состояния дополнительного информационного входа 24 запоминающе5го устройства 5 и триггера 10, устанавливающегося в единичное состояние при каждом переполнении младших разрядов 16 счетчика 15 адреса и устанавливаквдегося в нулевое состояние при появлении значащей вы борки , 50 - моменты появления значащих выборок и импульсов на выходе управления 8 ух;тройства 3 сравнения 51 - изменение адреса в запоминающем устройстве 5, происходящее при каждой значащей выборке; 52 - момен ты записи информации в запоминающее устройство 5/ 53 - сигнал, поступаю щий с выхода элемента 9 задержкиi 54 - импульсы формирователя 23, сра батывающего при переходе триггера 10 в единичное состояние; 55 - изменение адреса в запоминающем устройстве 22, происходящее под действием им пульса формирователя 23; 56 - моменты записи информадии в запоминаю щее устройство 22.Как следует из эпюр фиг, 2, запись информации в запоминающее устройство 22 происходит в детерменированные моменты времени независимо от статического характера появления значащих выборок с блока 3 сравнения, причем период записи tj составл нет где п - число разрядов группы млащших разрядов 16 счетчика ад ресов каналов 15, f - частота генератора 12. Такое соотнсяпение позволяет использовать запоминающее устройство 22 с 2 раз меньшем быстродействием чем запоминающее устройство 5. Число слов запоминающего устройства 22, с учетом статистического характера поступления значащих выбо рок, может быть меньше числа слов з поминающего устройства 5. Использование второго запоминающего устройства, выполненного на элементах, быстродействие которых в 2 раз меньше быстродействия элементов известной измерительной ристекы, второго устройства обнаружения заполнения памяти,триггера, схемы ИЛИ, двух элементов задержки и трех формирователей в их связи с известными блоками существенно повышает н дежность за счет того, что предлагае мая измерительная система позволяет отказаться от выполнения всего объема памяти на элементах с высоким быстродействием, а также за счет уме ньшения суммарного объема памяти. Формула изобретения Измерительная система, содержащая аналого-цифровой преобразовател разрядные выходы которого через бло сравнения соединены с первой группой информащ{онных входов первого запоминающего устройства, входы записи и адреса которого соединены с выходом управления блока сравнения, вход управления которого соединен с выходом блока управления приемом данных, вход управления аналого-цифрового преобразователя соединен с выходом генератора и с входом синхронизатора, выход которого соеди.ен с входом синхронизации блока сравнения и с входом счетчика адреса, группа младших разрядов которого соединена с второй группой информационных входов первого запоминающего устройства, выходы адреса которого соединены с входами первого устройства обнаружения заполнения памяти, а первая и вторая группы выходов первого запоминающего устройства соединены соответственно с первой и второй группами выходных-шин, отличающаяся тем, что, с целью повышения надежности, введены второе запоминающее устройство, второе устройство обнаружения заполнения памяти, триггер, элемент ИЛИ, два элемента задержки и три формирователя, причем выход старшего разряда группы младших разрядов счетчика адреса через первый формирователь соединен с первым входом триггера и с входом первого элемента задержки, выход которого через второй формирователь Соединен с входом записи второго запоминающего устройства, информационные входы которого соединены с выходами группы старших разрядов счетчика адреса, а выходы - с входами второго устройства обнаружения заполнения памяти, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого устройства обнаружения заполнения памяти, выход - с входом блока управления приемом данных, выход управления блока сравнения через второй элемент задержки соединен с вторым входом триггера, выход которого соединен с дополнительным информационным входом первого запоминающего устройства и через третий формирователь с входом адреса второго запоминающего устройства,, выходы которого соединены с третьей группой выходных шин, при этом дополнительный выход первого запоминающего устройства соединен с дополнительной выходной шиной . Источники информации,. принятые во внимание при экспертизе 1.Авторское свидетельство СССР 451188, кл. Н 03 К 13/02, 1975. 2.Воздушно-космическая телеметрия. Перевод с англ, под, ред. Трофимова К.Н., 1968, Воениздат, с. 200206, рис. 4, 17 (прототип). 2 3 1 S 6 7 8 9 il) Ifg111(-I1111111 0 1 2 3 0 1 2 00 123 000001 i11222 H111111111 Д I/i , 5/:D(, 11 12 13 IV IS 16 17 IS 13 20 21 1111111F1113 0 1 2 3 012301, 111 -1(f l111 I JJ 1)C±:{l

Авторы

Даты

1983-02-15—Публикация

1981-03-09—Подача