(Л

со

00

о 4;

ел

1

Изобретение относится к вычислительной технике, а именно к устройствам контроля матриц памяти на цилиндрических магнитных пленках (ЦМП), обладающих свойством неразрушающего считывания.

Цель изобретения - повыщение быстро- действия устройства.

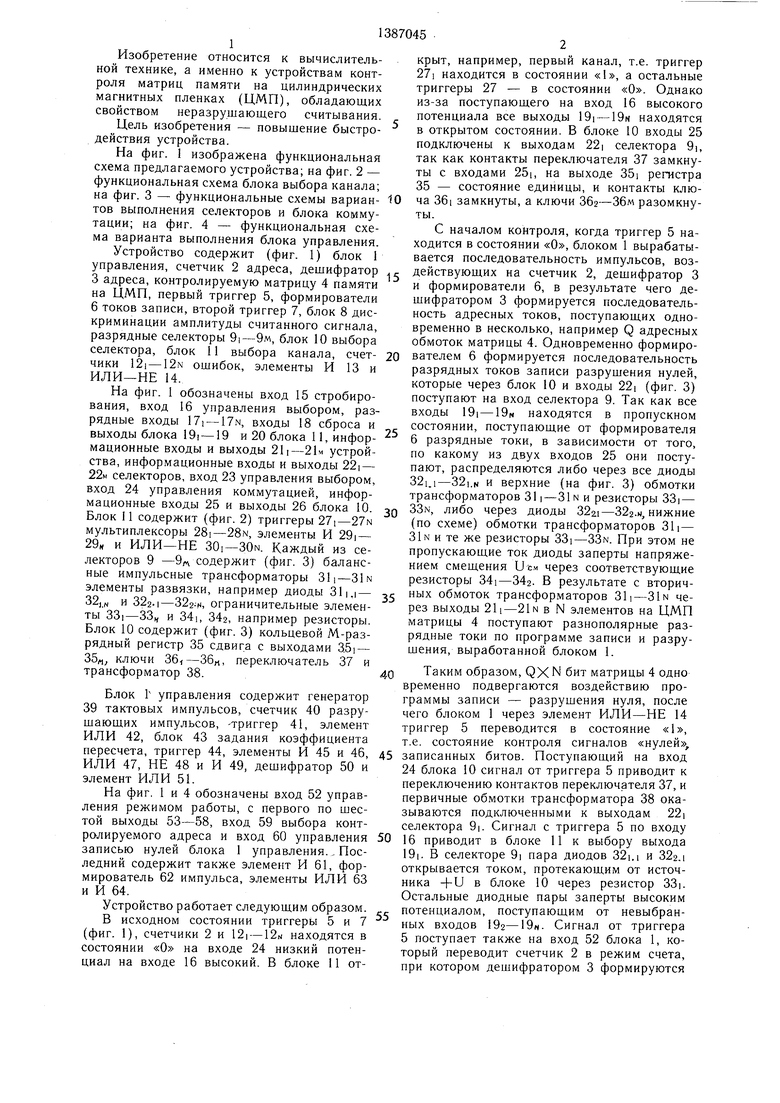

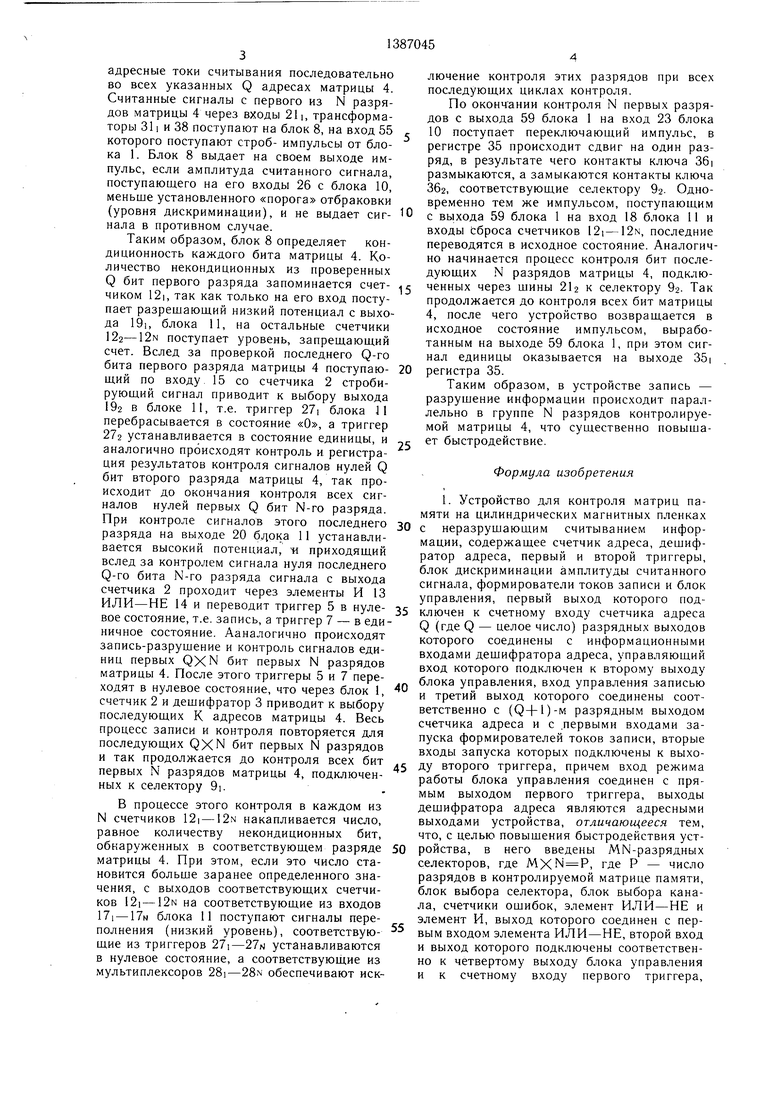

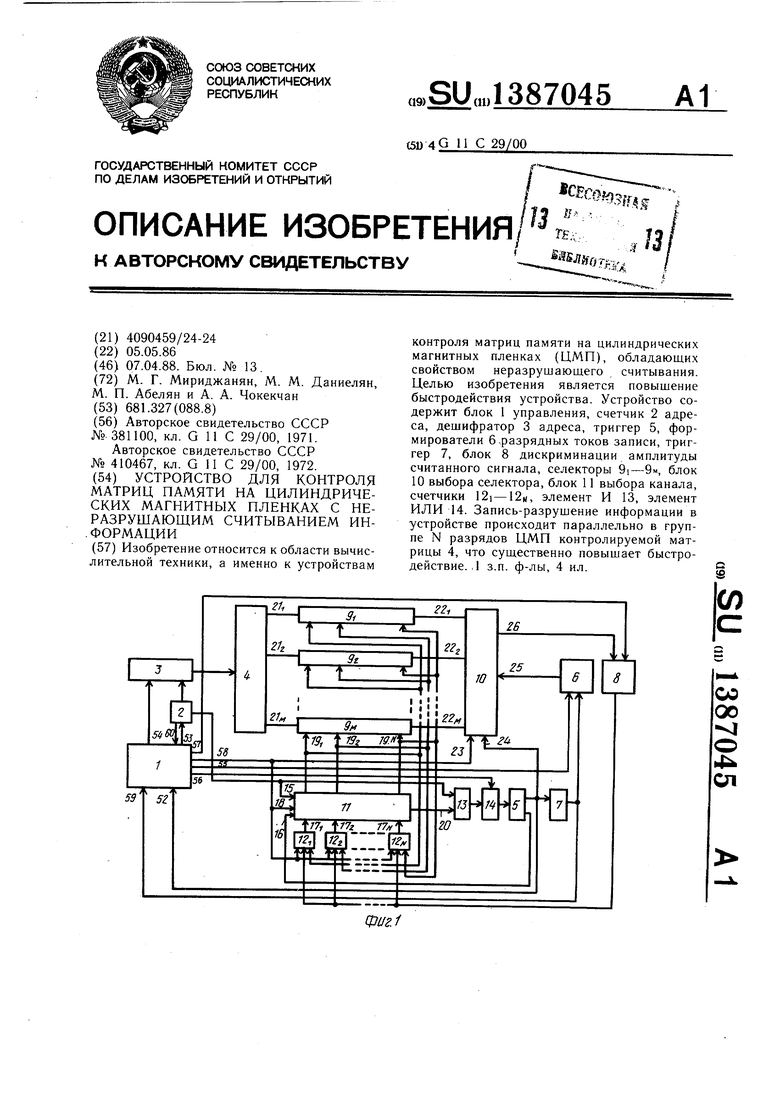

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока выбора канала;

крыт, например, первый канал, т.е. триггер 27i находится в состоянии «1, а остальные триггеры 27 - в состоянии «О. Однако из-за поступающего на вход 16 высокого потенциала все выходы 19i -19« находятся в открытом состоянии. В блоке 10 входы 25 подключены к выходам 22: селектора 9i, так как контакты переключателя 37 замкнуты с входами 25i, на выходе 35i регистра 35 - состояние единицы, и контакты клюты.

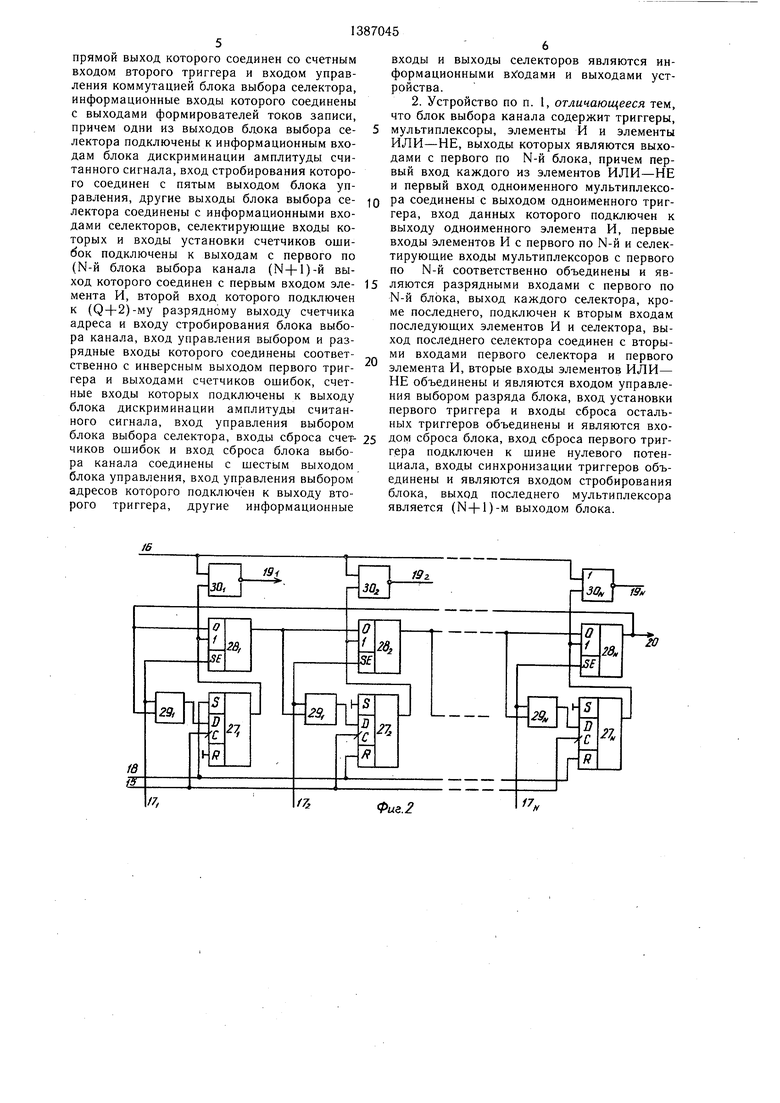

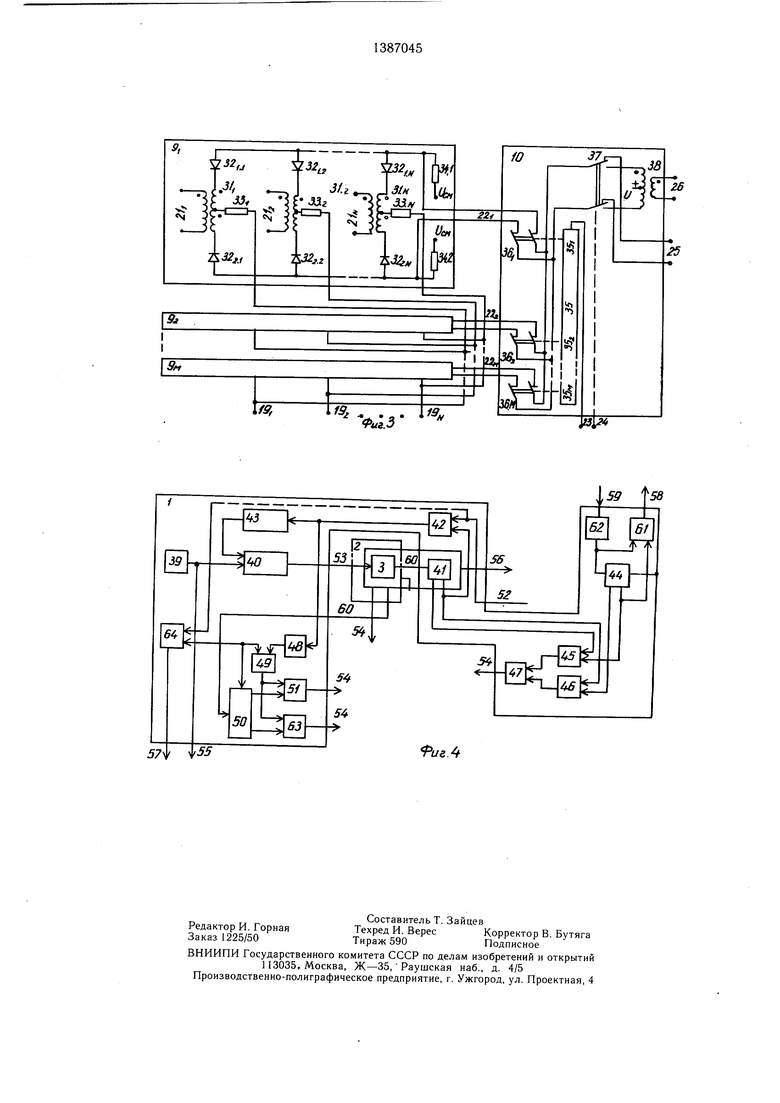

на фиг. 3 - функциональные схемы вариан- 10 ча 36i замкнуты, а ключи Зб2-36м разомкну- тов выполнения селекторов и блока коммутации; на фиг. 4 - функциональная схема варианта выполнения блока управления. Устройство содержит (фиг. 1) блок 1

С началом контроля, когда триггер 5 находится в состоянии «О, блоком 1 вырабатывается последовательность импульсов, возуправления, счетчик 2 адреса, дешифратор . действующих на счетчик 2, дешифратор 3

3 адреса, контролируемую матрицу 4 памяти на ЦМП, первый триггер 5, формирователи 6 токов записи, второй триггер 7, блок 8 дискриминации амплитуды считанного сигнала, разрядные селекторы 9i-9м, блок 10 выбора

и формирователи б, в результате чего дешифратором 3 формируется последовательность адресных токов, поступающих одновременно в несколько, например Q адресных обмоток матрицы 4. Одновременно формироселектора, блок 11 выбора канала, счет- 20 вателем 6 формируется последовательность 12i - 12N ошибок, элементы И

25

чики ошибок, элементы И 13 и ИЛИ-НЕ 14.

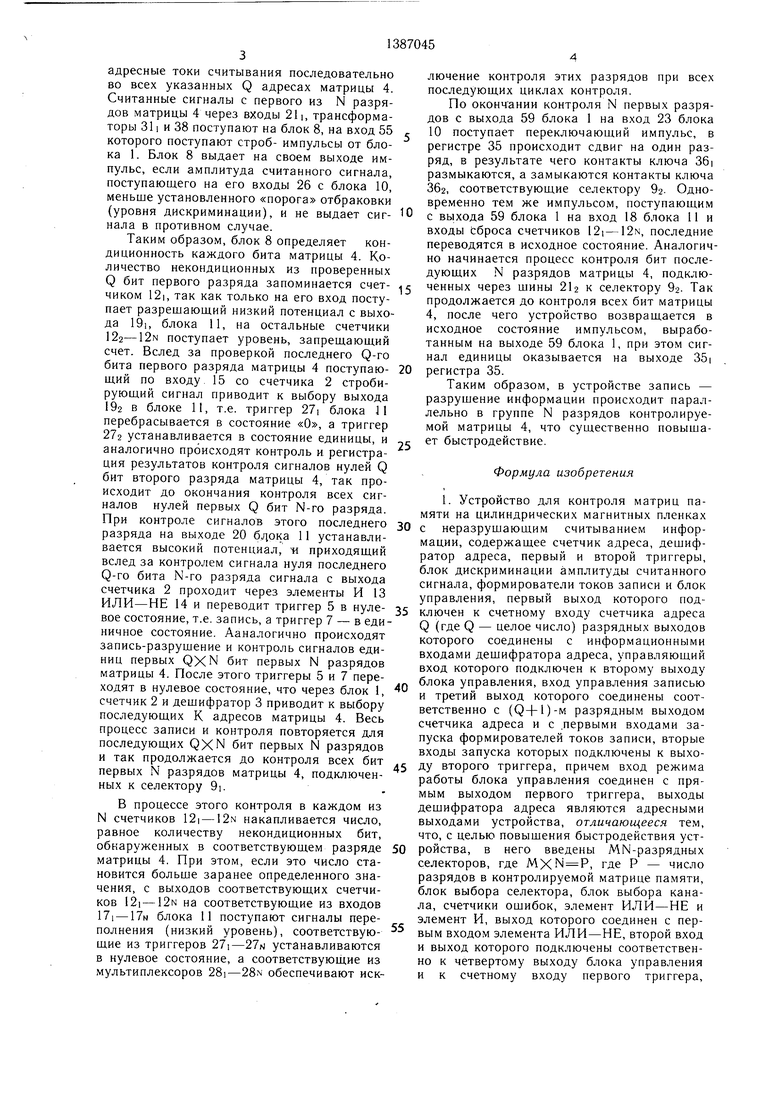

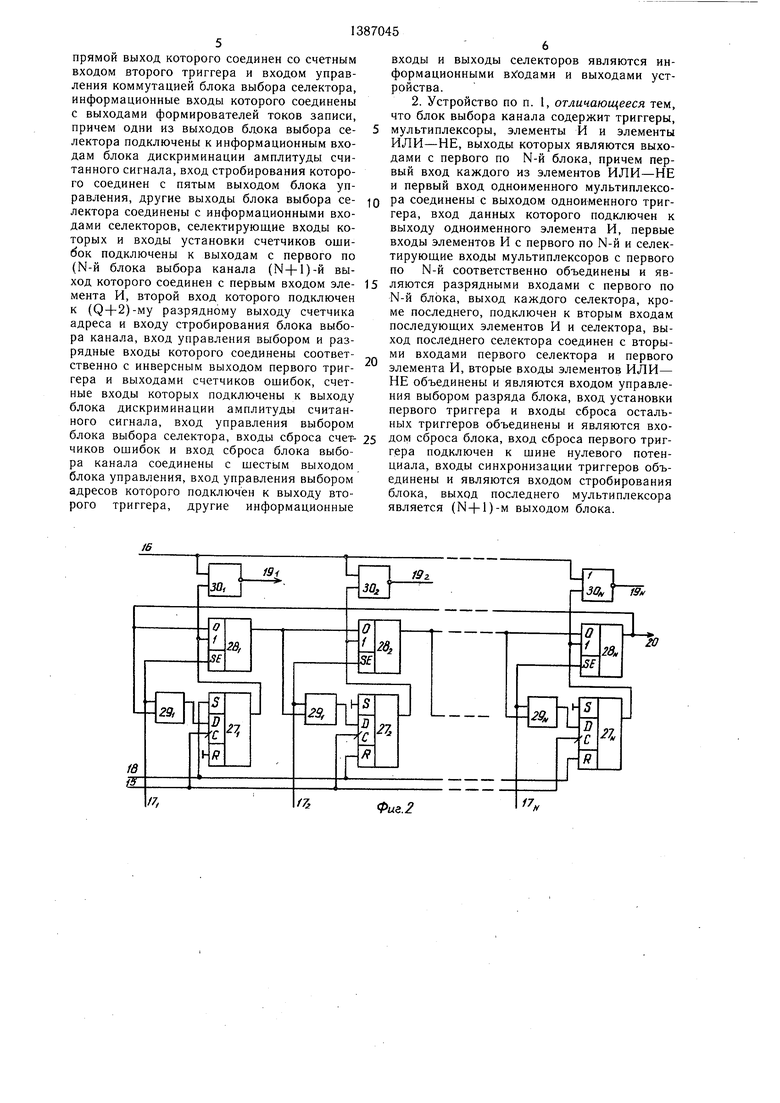

На фиг. 1 обозначены вход 15 стробиро- вания, вход 16 управления выбором, разрядные входы 7i -17N, входы 18 сброса и выходы блока 19i -19 и 20 блока 11, информационные входы и выходы 211-21м устройства, информационные входы и выходы 22i - 22м селекторов, вход 23 управления выбором, вход 24 управления коммутацией, информационные входы 25 и выходы 26 блока 10. Блок 11 содержит (фиг. 2) триггеры 27i-27N мультиплексоры 28i-28N, элементы И 29i - 29к и ИЛИ-НЕ 301--30N. Каждый из селекторов 9 -9л содержит (фиг. 3) балансные импульсные трансформаторы 311-31 N элементы развязки, например диоды 31 и- ,г 32,л и 322-1-322:м, ограничительные элементы 33|-33 и 34), 342, например резисторы. Блок 10 содержит (фиг. 3) кольцевой М-разрядный регистр 35 сдвига с выходами 35)- 35п, ключи 36i-Зби, переключатель 37 и трансформатор 38.

разрядных токов записи разрушения нулей, которые через блок 10 и входы 22i (фиг. 3) поступают на вход селектора 9. Так как все входы 19i-19ri находятся в пропускном состоянии, поступающие от формирователя 6 разрядные токи, в зависимости от того, по какому из двух входов 25 они поступают, распределяются либо через все диоды 32i.i-32i.N и верхние (на фиг. 3) обмотки трансформаторов 31:-31 N и резисторы 33 - 30 33N, либо через диоды 32 1-З22.м, нижние (по схеме) обмотки трансформаторов 311- 31N и те же резисторы 33i-33N. При этом не пропускающие ток диоды заперты напряжением смещения UtM через соответствующие резисторы 34i-342. В результате с вторичных обмоток трансформаторов 311-31 N через выходы 211-21N в N элементов на ЦМП матрицы 4 поступают разнополярные разрядные токи по программе записи и разрушения, выработанной блоком 1.

40 Таким образом, QX N бит матрицы 4 одно временно подвергаются воздействию программы записи - разрушения нуля, после чего блоком 1 через элемент ИЛИ-НЕ 14 триггер 5 переводится в состояние «1, т.е. состояние контроля сигналов «нулей.

40 Таким образом, QX N бит матрицы 4 одно временно подвергаются воздействию программы записи - разрушения нуля, после чего блоком 1 через элемент ИЛИ-НЕ 14 триггер 5 переводится в состояние «1, т.е. состояние контроля сигналов «нулей.

Блок 1 управления содержит генератор 39 тактовых импульсов, счетчик 40 разрушающих импульсов, -триггер 41, элемент ИЛИ 42, блок 43 задания коэффициента

пересчета, триггер 44, элементы И 45 и 46, 45 записанных битов. Поступающий на вход ИЛИ 47, НЕ 48 и И 49, дешифратор 50 и 24 блока 10 сигнал от триггера 5 приводит к элемент ИЛИ 51.переключению контактов переключателя 37, и

На фиг. 1 и 4 обозначены вход 52 управ- первичные обмотки трансформатора 38 ока- ления режимом работы, с первого по шее- зываются подключенными к выходам 22i той выходы 53-58, вход 59 выбора конт- селектора 9|. Сигнал с триггера 5 по входу ралируемого адреса и вход 60 управления 50 16 приводит в блоке 11 к выбору выхода записью нулей блока 1 управления.,Пос19i. В селекторе 9i пара диодов 32i.i и 322.1 открывается током, протекающим от источника + U в блоке 10 через резистор 33|. Остальные диодные пары заперты высоким Устройство работает следующим образом.потенциалом, поступающим от невыбранВ исходном состоянии триггеры 5 и 7 - ных входов 192-19н. Сигнал от триггера (фиг. 1), счетчики 2 и 12i -12« находятся в состоянии «О на входе 24 низкий потенледний содержит также элемент И 61, формирователь 62 импульса, элементы ИЛИ 63 и И 64.

5 поступает также на вход 52 блока 1, который переводит счетчик 2 в режим счета, при котором дешифратором 3 формируются

циал на входе 16 высокий. В блоке 11 от1387045

крыт, например, первый канал, т.е. триггер 27i находится в состоянии «1, а остальные триггеры 27 - в состоянии «О. Однако из-за поступающего на вход 16 высокого потенциала все выходы 19i -19« находятся в открытом состоянии. В блоке 10 входы 25 подключены к выходам 22: селектора 9i, так как контакты переключателя 37 замкнуты с входами 25i, на выходе 35i регистра 35 - состояние единицы, и контакты клюты.

ча 3

ча 36i замкнуты, а ключи Зб2-36м разомкну-

С началом контроля, когда триггер 5 находится в состоянии «О, блоком 1 вырабатывается последовательность импульсов, воздействующих на счетчик 2, дешифратор 3

действующих на счетчик 2, дешифратор 3

и формирователи б, в результате чего дешифратором 3 формируется последовательность адресных токов, поступающих одновременно в несколько, например Q адресных обмоток матрицы 4. Одновременно формиро вателем 6 формируется последовательность

вателем 6 формируется последовательность

разрядных токов записи разрушения нулей, которые через блок 10 и входы 22i (фиг. 3) поступают на вход селектора 9. Так как все входы 19i-19ri находятся в пропускном состоянии, поступающие от формирователя 6 разрядные токи, в зависимости от того, по какому из двух входов 25 они поступают, распределяются либо через все диоды 32i.i-32i.N и верхние (на фиг. 3) обмотки трансформаторов 31:-31 N и резисторы 33 - 33N, либо через диоды 32 1-З22.м, нижние (по схеме) обмотки трансформаторов 311- 31N и те же резисторы 33i-33N. При этом не пропускающие ток диоды заперты напряжением смещения UtM через соответствующие резисторы 34i-342. В результате с вторичных обмоток трансформаторов 311-31 N через выходы 211-21N в N элементов на ЦМП матрицы 4 поступают разнополярные разрядные токи по программе записи и разрушения, выработанной блоком 1.

Таким образом, QX N бит матрицы 4 одно временно подвергаются воздействию программы записи - разрушения нуля, после чего блоком 1 через элемент ИЛИ-НЕ 14 триггер 5 переводится в состояние «1, т.е. состояние контроля сигналов «нулей.

записанных битов. Поступающий на вход 24 блока 10 сигнал от триггера 5 приводит к переключению контактов переключателя 37, и

ных входов 192-19н. Сигнал от триггера

5 поступает также на вход 52 блока 1, который переводит счетчик 2 в режим счета, при котором дешифратором 3 формируются

адресные токи считывания последовательно во всех указанных Q адресах матрицы 4. Считанные сигналы с первого из N разрядов матрицы 4 через входы 211, трансформаторы 311 и 38 поступают на блок 8, на вход 55 которого поступают строб- импульсы от блока 1. Блок 8 выдает на своем выходе импульс, если амплитуда считанного сигнала, поступающего на его входы 26 с блока 10, меньше установленного «порога отбраковки (уровня дискриминации), и не выдает сигнала в противном случае.

Таким образом, блок 8 определяет кондиционность каждого бита матрицы 4. Количество некондиционных из проверенных Q бит первого разряда запоминается счетчиком 12|, так как только на его вход поступает разрешающий низкий потенциал с выхода 19i, блока 11, на остальные счетчики 122-12N поступает уровень, запрещаюш,ий счет. Вслед за проверкой последнего Q-ro бита первого разряда матрицы 4 поступаю- Ш.ИЙ по входу 15 со счетчика 2 строби- рующий сигнал приводит к выбору выхода 192 в блоке II, т.е. триггер 27} блока 11 перебрасывается в состояние «О, а триггер 272 устанавливается в состояние единицы, и аналогично происходят контроль и регистрация результатов контроля сигналов нулей Q бит второго разряда матрицы 4, так происходит до окончания контроля всех сигналов нулей первых Q бит N-ro разряда. При контроле сигналов этого последнего разряда на выходе 20 бдока 11 устанавливается высокий потенциал, -и приходяший вслед за контролем сигнала нуля последнего Q-ro бита N-ro разряда сигнала с выхода счетчика 2 проходит через элементы И 13 ИЛИ-НЕ 14 и переводит триггер 5 в нулевое состояние, т.е. запись, а триггер 7 - в единичное состояние. Ааналогично происходят запись-разрушение и контроль сигналов единиц первых QXN бит первых N разрядов матрицы 4. После этого триггеры 5 и 7 переходят в нулевое состояние, что через блок 1, счетчик 2 и дешифратор 3 приводит к выбору последуюш,их К адресов матрицы 4. Весь процесс записи и контроля повторяется для последующих QXN бит первых N разрядов и так продолжается до контроля всех бит первых N разрядов матрицы 4, подключенных к селектору 9i.

В процессе этого контроля в каждом из N счетчиков 12i-12N накапливается число, равное количеству некондиционных бит, обнаруженных в соответствующем разряде матрицы 4. При этом, если это число становится больше заранее определенного значения, с выходов соответствующих счетчиков 12i - 12N на соответствующие из входов 17i - 17м блока 11 поступают сигналы переполнения (низкий уровень), соответствующие из триггеров 27i-27ц устанавливаются в нулевое состояние, а соответствующие из мультиплексоров 28i-28N обеспечивают иск0

5

0

5

0

5

0

5

0

5

лючение контроля этих разрядов при всех последующих циклах контроля.

По окончании контроля N первых разрядов с выхода 59 блока 1 на вход 23 блока 10 поступает переключающий импульс, в регистре 35 происходит сдвиг на один разряд, в результате чего контакты ключа Зб| размыкаются, а замыкаются контакты ключа Зб2, соответствующие селектору 92. Одновременно тем же импульсом, поступающим с выхода 59 блока 1 на вход 18 блока 11 и входы сброса счетчиков 12i-12N, последние переводятся в исходное состояние. Аналогично начинается процесс контроля бит последующих N разрядов матрицы 4, подключенных через щины 212 к селектору 92. Так продолжается до контроля всех бит матрицы 4, после чего устройство возвращается в исходное состояние импульсом, выработанным на выходе 59 блока 1, при этом сигнал единицы оказывается на выходе 35: регистра 35.

Таким образом, в устройстве запись - разрушение информации происходит параллельно в группе N разрядов контролируемой матрицы 4, что существенно повышает быстродействие.

Формула изобретения

1. Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации, содержащее счетчик адреса, дешифратор адреса, первый и второй триггеры, блок дискриминации амплитуды считанного сигнала, формирователи токов записи и блок управления, первый выход которого подключен к счетному входу счетчика адреса Q (где Q - целое число) разрядных выходов которого соединены с информационными входами дешифратора адреса, управляющий вход которого подключен к второму выходу блока управления, вход управления записью и третий выход которого соединены соответственно с (Q+1)-M разрядным выходом счетчика адреса и с .первыми входами запуска формирователей токов записи, вторые входы запуска которых подключены к выходу второго триггера, причем вход режима работы блока управления соединен с прямым выходом первого триггера, выходы дешифратора адреса являются адресными выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены MN-разрядных селекторов, где , где Р - число разрядов в контролируемой матрице памяти, блок выбора селектора, блок выбора канала, счетчики ошибок, элемент ИЛИ-НЕ и элемент И, выход которого соединен с первым входом элемента ИЛИ-НЕ, второй вход и выход которого подключены соответственно к четвертому выходу блока управления и к счетному входу первого триггера.

прямой выход которого соединен со счетным входом второго триггера и входом управления коммутацией блока выбора селектора, информационные входы которого соединены с выходами формирователей токов записи, причем одни из выходов блока выбора се- лектора подключены к информационным входам блока дискриминации амплитуды считанного сигнала, вход стробирования которого соединен с пятым выходом блока управления, другие выходы блока выбора се- лектора соединены с информационными входами селекторов, селектирующие входы которых и входы установки счетчиков оши- doK подключены к выходам с первого по (N-й блока выбора канала (Ы+1)-й выход которого соединен с первым входом эле- мента И, второй вход которого подключен к (Q-|-2)-My разрядному выходу счетчика адреса и входу стробирования блока выбора канала, вход управления выбором и разрядные входы которого соединены соответственно с инверсным выходом первого триггера и выходами счетчиков ошибок, счетные входы которых подключены к выходу блока дискриминации амплитуды считанного сигнала, вход управления выбором блока выбора селектора, входы сброса счет- чиков ошибок и вход сброса блока выбора канала соединены с шестым выходом блока управления, вход управления выбором адресов которого подключен к выходу второго триггера, другие информационные

входы и выходы селекторов являются информационными вх одами и выходами устройства.

2. Устройство по п. 1, отличающееся тем, что блок выбора канала содержит триггеры, мультиплексоры, элементы И и элементы ИЛИ-НЕ, выходы которых являются выходами с первого по N-й блока, причем первый вход каждого из элементов ИЛИ-НЕ и первый вход одноименного мультиплексора соединены с выходом одноименного триггера, вход данных которого подключен к выходу одноименного элемента И, первые входы элементов И с первого по N-й и селектирующие входы мультиплексоров с первого по N-й соответственно объединены и являются разрядными входами с первого по N-й блока, выход каждого селектора, кроме последнего, подключен к вторым входам последующих элементов И и селектора, выход последнего селектора соединен с вторыми входами первого селектора и первого элемента И, вторые входы элементов ИЛИ- НЕ объединены и являются входом управления выбором разряда блока, вход установки первого триггера и входы сброса остальных триггеров объединены и являются входом сброса блока, вход сброса первого триггера подключен к шине нулевого потенциала, входы синхронизации триггеров объединены и являются входом стробирования блока, выход последнего мультиплексора является (N+1)-M выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Буферное запоминающее устройство | 1978 |

|

SU769620A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Изобретение относится к области вычислительной техники, а именно к устройствам контроля матриц памяти на цилиндрических магнитных пленках (ЦМП), обладающих свойством неразрушающего считывания. Целью изобретения является повыщение быстродействия устройства. Устройство содержит блок 1 управления, счетчик 2 адреса, дешифратор 3 адреса, триггер 5, формирователи 6-разрядных токов записи, триггер 7, блок 8 дискриминации амплитуды считанного сигнала, селекторы 9i-9м, блок 10 выбора селектора, блок 11 выбора канала, счетчики 12i -12, элемент И 13, элемент ИЛИ 14. Запись-разрушение информации в устройстве происходит параллельно в группе N разрядов ЦМП контролируемой матрицы 4, что существенно повышает быстродействие. Л з.п. ф-лы, 4 ил.

ffff

..,. 1«5.

Фиг.о

57

fue/t

| 15СЕСОЮЗНАЯ | 0 |

|

SU381100A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| 1972 |

|

SU410467A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-07—Публикация

1986-05-05—Подача