1

Изобретение относится к постоянным запоминакнцим устройствам и мо жат быть использовано в автоматике и вычислительной технике.

Известно программируемое постоянное запоминающее устройство, содержащее микросхемы программируемой постоянной памяти, одноименные разрядные выходы которых объединены и подключены к выходным шинам ,

Известно программируемое постоянное запоминающее устройство, содержащее в качеству запоминающих элементов многоэмиттерные транзисторы, эмиттеры которых подключены к-соответствующим разрядным шинам через плавкие (нихромовые) перемычки 2.

Недостатком известных устройств является их сравнительно низкая надежность, обусловленная, в частности, явлением последующего восстановления плавких (нихромовых) перемычек, пережигаемых при записи информации (например, при записи 1 в

микросхемах КР55бРТ4). При большом количестве пережиганий увеличивается также вероятность ошибок и время занесения информации в микросхемы прю-. граммируемой постоянной памяти, что снижает технологичность программиром вания и уменьшает коэффициент программируемости. микросхем программируемой постоянной памяти.

Наиболее близким по технической сущности и схемному решению является программируемое постоянное запоминающее устройство, содержащее модули памяти, дешифратор, блок формирювателей четности и позволяющее маскировать дефектные биты на основе метода поразрядного кодирования. Информация о необходимости инвертирования хранится вОДНОМ из разрядов модулей памяти ГЗТ.

Недостатком указанного устройства является то, что возможно попадание дефектного на дополнительный разряд, либр бит не прожжеться, либо

39

перемычка может восстановиться. Все это снижает надежность работы устройства.

Цель изобретения - повышение надежности программируемого постоянного запоминающего устройства.

Эта цель достигается тем, что программируемое постоянное запоминающее устройство, содержащее модули памяти адресные входы которых соединены с входами дешифратора и являются входами устройства, выходы дешифратора соединеныс входами выборки соответствующих модулей.памяти, выходы которых соединены с входами первой группы блока формирователей четности, выходы которого являются выходами устройства, содержит дополнительный модуль памяти, адресные входы которого соединены с входами устройства, а выходы -те входами второй

группы блока формирователей четнос-ти I.

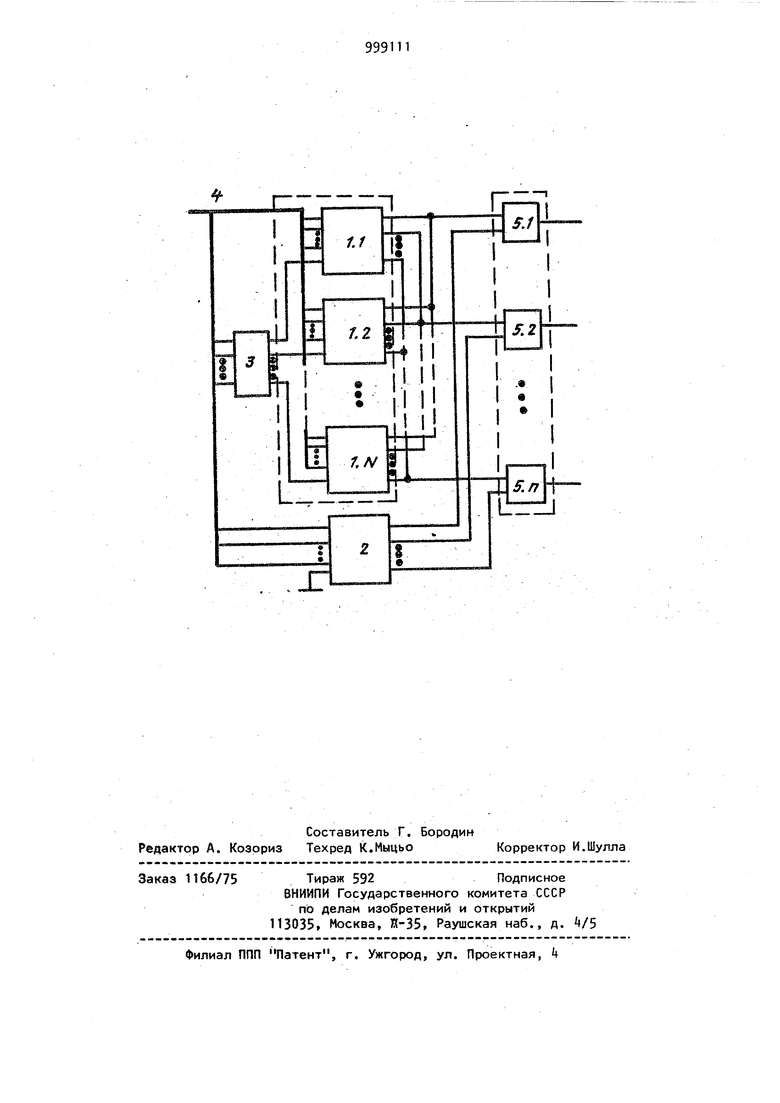

На чертеже представлена блок-схем

программируемого постоянного запоминающего устройства.

Программируемое постоянное запоминающее устройство содержит N модулей 1 памяти и дополнительный модуль 2 памяти с п разрядными выходами и дешифратор 3, выходы которого соединены с входами выборки соответствующих модулей 1 памяти. Вход выборки дополнительного модуля 2 памяти соединен с шиной разрешающего потенциала. Адресные входы модулей.1 памяти, входы дешифратора 3 и адресные входы дополнительного модуля 2 памяти соединены с кодовыми шинами k адреса. Одноименные разрядные выходы основных модулей 1 памяти соединены с входами первой группы блока 5 формирователей четности. Разрядные выходы дополнительного модуля 2 памяти соединены с входами второй группы блока. 5 формирователей четности, выходы которых являются выходами,устройства

Программируемое постоянное запоминающее устройство работает следующим образом,S

При поступлении на кодовые шины k адреса сигналов кода адреса выбирается соответствующий модуль 1 памяти и считывается записанная по поступившему адресу информация и параллельно - информация из дополнительного модуля 2 памяти, относящаяся к соответствующей группе адресов (слов модулей 1 памяти.

14

Информация на выход устройства поступает из выбранного модуля I памяти в прямом коде в тех разрядах, по которым в дополнительном модуле 2 памяти записаны О, и - в обратном коде, если в соответствующих разряда дополнительного модуля 2 записаны 1, В дополнительном модуле 2 памяти записаноSNn-разрядных кодов, где S - количество групп адресов (схгав) в-модуле 1 памяти.

Таким образом-, считывание информации из программируемого постоянного запоминающего устройства в каждом разряде групп адресов определяется функцией

1 .

где X. - бит в данном разряде основной микросхемы 1; X,- - бит в данном разряде дополнительной микросхемы 2 и таблицей истинности:

X X f i

3Yo позволяет информацию в группах адресов (слов) модулей 1 памяти в разрядах с преобладающим количеством 1 (для записи которых нужно пережигать перемычки) записывать в обратном коде. .

Пусть, например, модуль (N 1) имеет емкость 6 бита (iG-t) и в нее необходимо записать информацию: 0000

0001

0010

0011

0100

0101

ОНО

0111

1000

1001

1010

1011

1100

1101

1110

1111

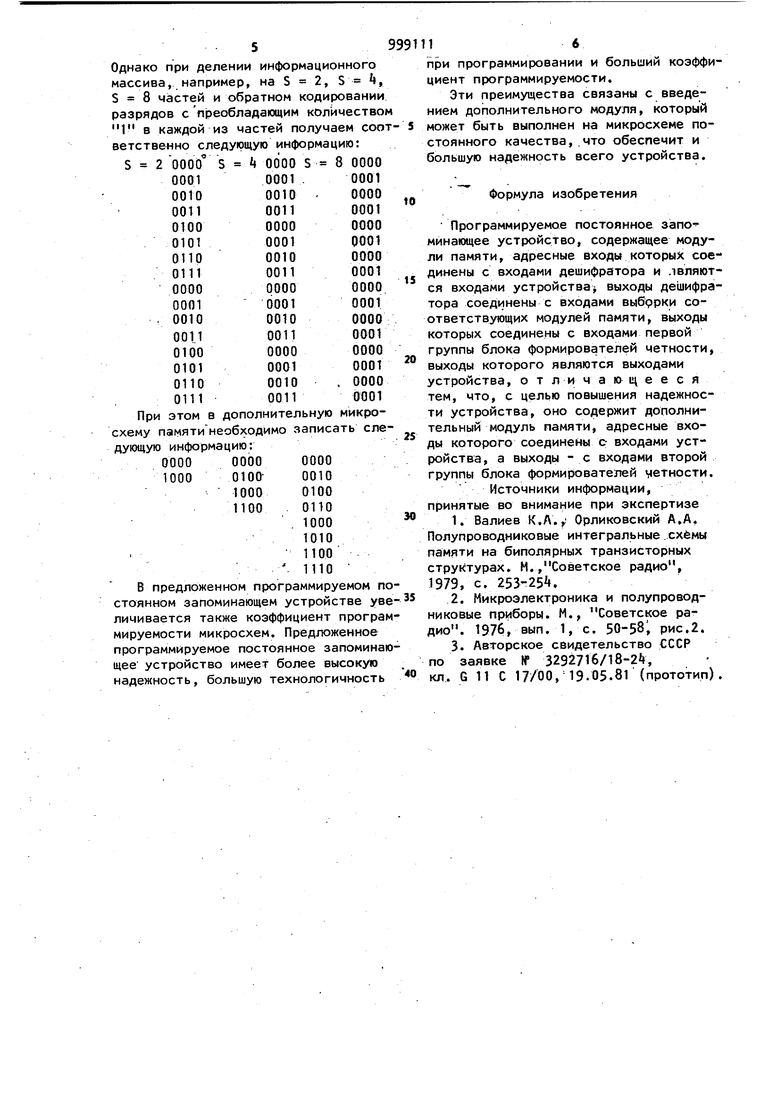

Количество 1 в каждом разряде равно 8 и обратное кодирование разрядов всех 16 слов не имеет смысла. 5 Однако при делении информационного массива, например, на S 2, S k, S 8 частей и обратном кодировании разрядов с п|эеобладающим количеством 1 в каждой из частей получаем соот ветственно следующую информацию: 5 2 0000 S 8 0000 0001 0001 .0001 OOrO 0010 .0000 0011 00110001 010000000000 010100010001 01100010 0000 01110011 0001 00000000 0000 00010001 0001 . 001000100000 001.1ООП0001 010000000000 010100010001 01100010 . 0000 01110011 0001 При этом в дополнительную микросхему памятинеобходимо записать еледующую информацию: 0000 0000 0000 1000 0100- 0010 1000 0100 1100 0110 1000 1010 1100 1110 в предложенном программируемом по стоянном запоминающем устройстве уве личивается также коэффициент програм мируемое ти микросхем. Предложенное программируемое постоянное запоминаю щее устройство имеет более высокую надежность, большую технологичность 16 при программировании и больший коэффициент программируемости. Эти преимущества связаны с введением дополнительного модуля, который может быть выполнен на микросхеме постоянного качества,.что обеспечит и большую надежность всего устройства. Формула изобретения Программируемое постоянное запо минающее устройство, содержащее модули памяти, адресные входы которых соединены с входами дешифратора и лвляются входами устройства выходы дешифратора соединены с входами выбррки соответствующих модулей памяти, выходы которых соединены с входами первой группы блока формирователей четности, выходы которого являются выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный модуль памяти, адресные входы которого соединены с входами устройства, а выходы - с входами второй группы блока формирователей четности. Источники информации, принятые во внимание при экспертизе 1.Валиев К.Л., Орликовский А,А, Полупроводниковые интегральные.схемы памяти на биполярных транзисторных структурах. М.,Советское радио, 1979,0.253-25. 2.Микроэлектроника и полупроводниковые приборы. М., Советское радио. 1976, вып. 1, с. 50-58i, рис.2. 3.Авторское свидетельство СССР по заявке Jf 3292716/18-24, кл. G 11 С 17/00,49.05.81 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU972595A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU1080214A1 |

| Устройство для разбраковки микросхем | 1981 |

|

SU968852A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

Авторы

Даты

1983-02-23—Публикация

1981-07-20—Подача