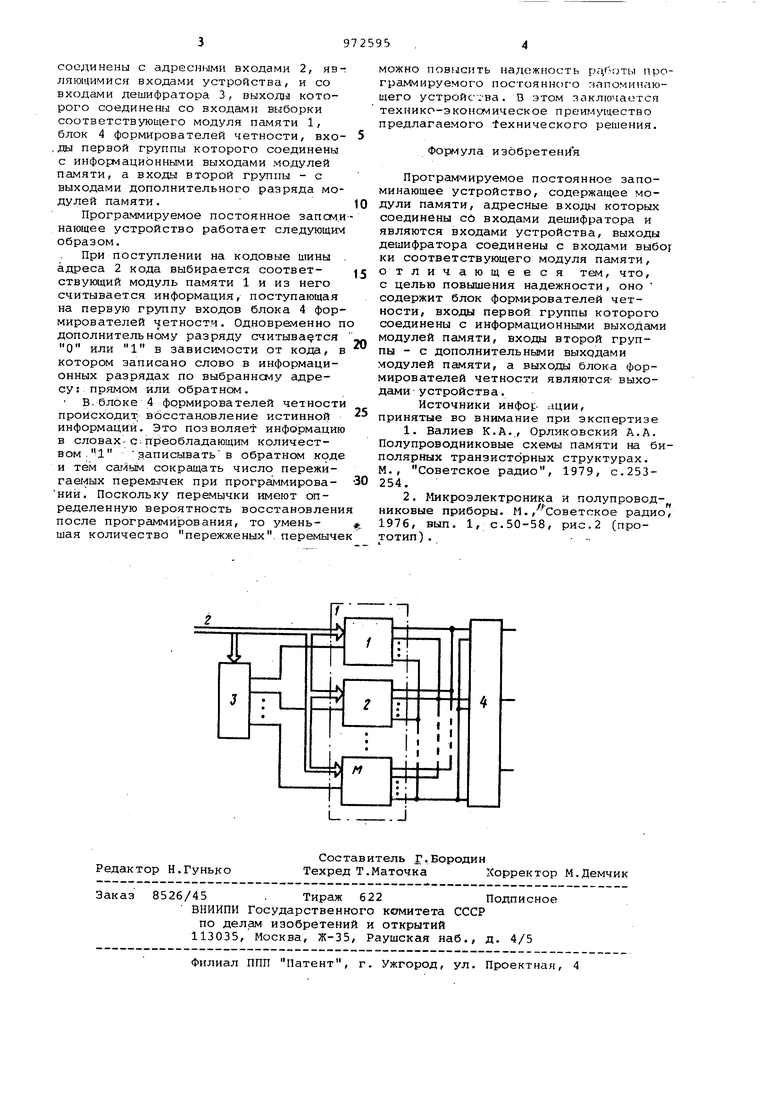

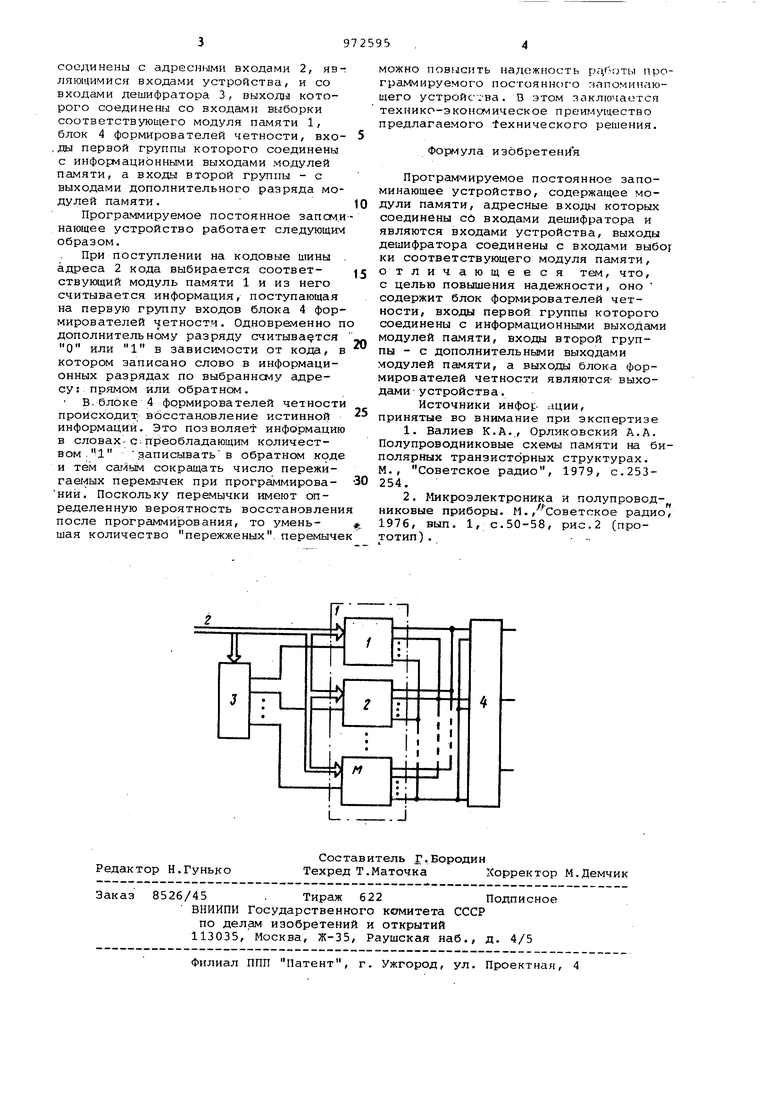

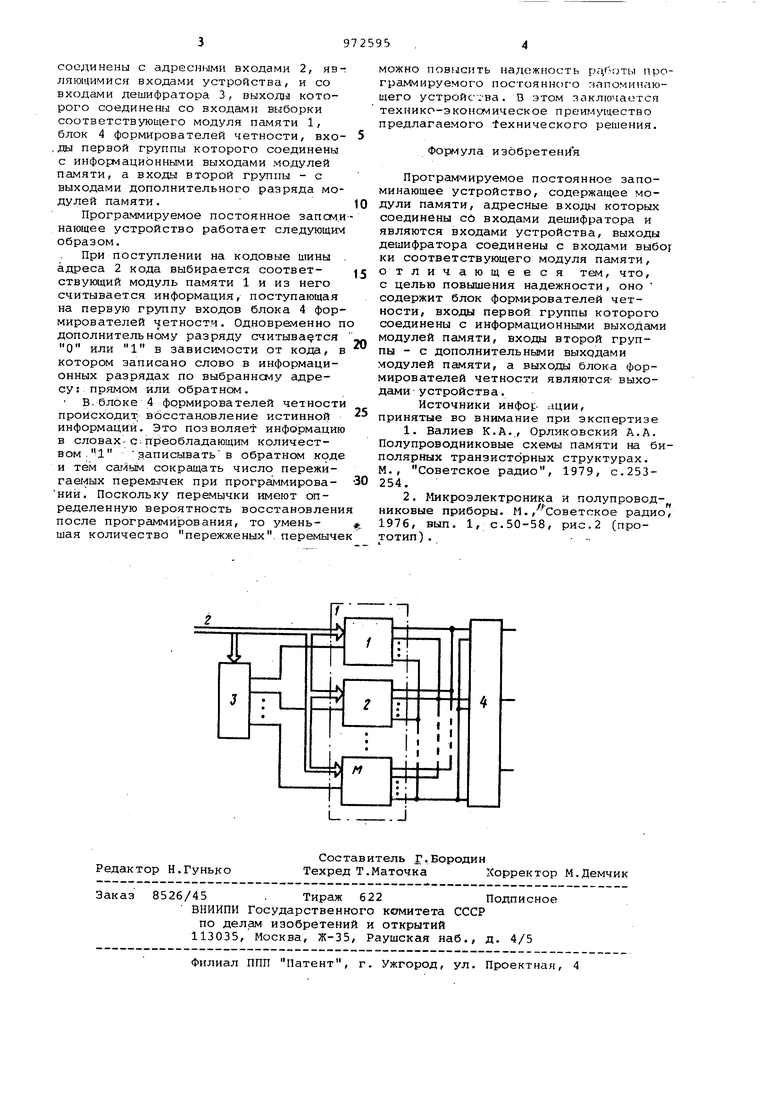

Изобретение относится к вычислительной технике, а именно к организации постоянных запоминающих устройств на интегральных микросхемах. Известно программируемое постоянное запоминающее устройство, содержащее микросхемы программируемой постоянной памяти, одноименные разрядные ВЫХО.ЦЫ которых объединены и подключены к выходным шинам 1 . Недостатком указанного устройства является невозможность использова ния микросхем с дефектными битами на основе поразрядного обратного код рования . Наиболее близким по технической сущности к предлагаемому является постоянное запоминающее устройство содержащее микросхемы постоянной памяти и дешифратор, выходы которого соединены со входом выбора микросхемы 2. Недостатком указанного устройства является невозможность использования I метода поразрядного обратного кодиро вания с целью уменьшения коли ества прожигаемых перемычек использовать ми1сросхемы- с дефектными битами. Целью изобретения является повышение надежности за счет обеспечения возможности использования метода поразрядного обратного кодирования при построении запоминающего устройства, что уменьшит количество пережигаемых перемычек и уменьшит вероятность и:: восстановления. Указанная цель достигается тем,что программируемое постоянное запоминающее устройство, содержащее модули памяти, адресные входы которых соединены со входами дешифратора и являются входами устройства, выходы дешифратора соединены с входами выборки соответствующего модуля памяти, дополнительно содержит блок формирователей четности, входы первой группы.которого соединены с информационными входами модулей памяти, входы второй группы - с дополнительными выходами модулей памяти, а выходы блока формирователей четности являются выходами устройства. На чертеже представлена блок-схема предлагаемого программируемого постоянного запоминающего устройства. Программируемое постоянное запоминающее устройство содержит модули памяти 1, адресные входы которых соединены с aflpecHFJMH входами 2, являющимися входами устройства, и со входами дешифратора 3, выходы которого соединены со входами выборки соответствующего модуля памяти 1, блок 4 формирователей четности, вхо ,ды первой группы которого соединены с информационными выходами модулей памяти, а входы второй группы - с выходами дополнительного разряда мо дулей памяти. Программируемое постоянное запом. нающее устройство работает следующим образом. При поступлении на кодовые шины адреса 2 кода выбирается соответствующий модуль памяти 1 и из него считывается информация, поступающая на первую группу входов блока 4 фор мирователей четностм. Одновременно дополнительному разряду считывается О или 1 в зависимости от кода, котором записано слово в информационных разрядах по выбранному адресу: прямом или обратнся. В,блоке 4 формирователей четност ПРОИСХОДИТ; вбсстааовление истинной информации. Это позволяет информацию в словах-д пр еобладающим количеством .Ч записывать в обратном код и тем самым сокращать числс пережигаемых перемычек при программировании. Поскольку перамычки имеют определенную вероятность восстановлен после программирования, то уменьшая количество пережженых, перемыч можно повысить надежЕЮсть рс,боты программируемого постоянного запоминающего устройства. В этом заключается технико-экономическое преимущество предлагаемого технического решения. Формула изобретения Программируемое постоянное запоминающее устройство, содержащее модули памяти, адресные входы которых соединены ей входами дешифратора и являются входами устройства, выходы дешифратора соединены с входами выбор ки соответствующего модуля памяти, отличающее ся тем, что, с целью повышения надежности, оно содержит блок формирователей четности, входы первой группы которого соединены с информационными выходами модулей памяти, входы второй группы - с дополнительными выходами модулей памяти, а выходы блока формирователей четности являются- выходами устройства. Источники инфор ации, принятые во внимание при экспертизе 1.Валиев К.А., Орликовский А.А. Полупроводниковые схемы памяти на биполярных транзисторных структурах. М., Советское радио, 1979, с.253254. 2.Микроэлектроника и полупроводниковые приборы. М., советское радио, 1976, вып. 1, с.50-58, рис.2 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU999111A1 |

| Устройство для разбраковки микросхем | 1981 |

|

SU968852A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

Авторы

Даты

1982-11-07—Публикация

1981-05-19—Подача