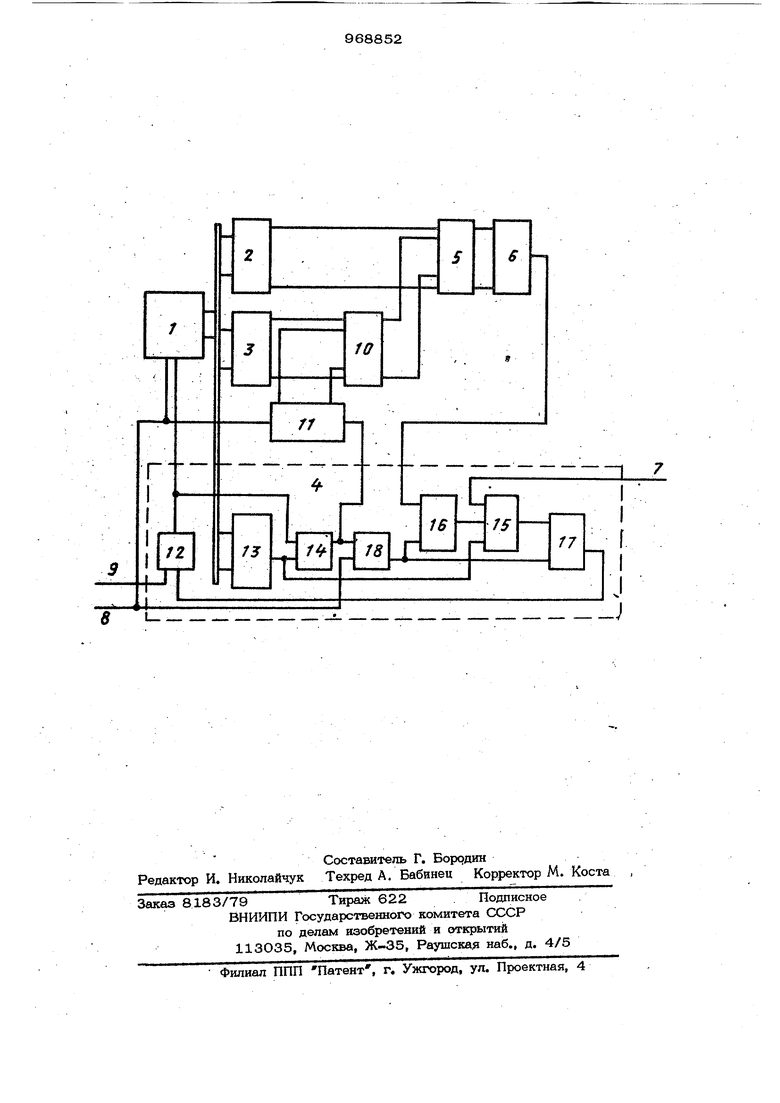

,.; 1 Изобретение относится к вычислительной технике, а именно к устройствам для разбраковки микросхем постоянной памяти с дефектными битами. Известно устройство для разбраковки микросхем постоянной памяти, осуществляющее подбор информации из эталонного накопителя в накопитель программируемой постоянной памяти, что позволяет использовать микросхемы постоянной памяти с дефектными битами Q 1 3 Наиболее близким по технической сущности к предлагаемому является устройство для .разбраковки микросхем постоянной памяти, содержащее блок оперативной памяти для хранения эталонной информдо ции и устройство сравнения и осушествля щее подбор микросхем постоянной памяти с дефектными битами под эталонную информацию 2 J.. Недостатком известных устройств для разбраковки микросхем является сравнительно малая возможность подбора микро схем программируемой постоянной памяти с дефектными битами из-оа сравнения с эталонной информацией, считываемой в прямом коде. Однако путем инверсии информации части кшссива микросхемы памяти можно было бы увеличить процент подбора программируемых микросхем и увеличить быстродействие у стройства, Цельк) изобретения является повышение стродействия устройства, а именно обеспечение возможности подборе микросхем памяти с дефектными битами и с учетом инвертирования части записываемой информации на основе метода поразрядного обратного кодирования. Указанная цель достигается тем, что устройство для разбраковки микросхем, содержащее адресный счетчик, выходы которого соединены с первым входом блока управления и $тляются выходами устройства, блок элементов И, входы первой грушш которого являются одними информационными входами устройства, а выховыход которого соединен с вторым входом блока упразаления, третий, четвертый, пятый входы которого являются соответственно первым, вторым, третьим управляющими входами устройства, счетный вход адресного счетчика соединен с nep-i вым выходом блока управления, а установочный вход - с четвертым входом блока управления, дополнительно содержит счетчик циклов и блок формирователей четности, выходы которого соединены с входами второй группы блока элементов И, первые входы блока формирователей четности являются другими информационными входами устройства, а вторые входы соединены с выходами счетчика циклов, счетный вход которого соединен, с вторым входом блока управления, а установочный вход соединен с четвертым входом блока управления. На чертеже представлена блок-схема устройства для разбраковки микросхем. Устройство содержит адресный счетчи 1, выходы которого соединены с первыми группами Контактов первого 2 и вто рого 3 блока контактов и блока 4 управ ления, вторая группа контактов первого блока 2 контактов соединена с первыми входами блока элементов И 5, выходы которого соединены с вxoдa Ш элемента ИЛИ 6, выход которого соединен с вторым входом блока 4 управления, третий, четвертый, пятый входы которого являются соответственно первым 7, вторым 8, третьим 9 управляющими входами устройства, счетный вход адресного счет чика 1 соединен с первым выходом блока 4 управления, а установочный вход с четвертым входом блока 4 управления выходы блока 10 формирователей четнос соединены с вторыми входами блока элементов И 5, перзвые входы блока 10 формирователей четности соединены с вт рой группой контактов второго блока 3 контактов, а вторые входы соединены с выходами счетчика 11 шослов, счетный вход которого соединен с вторым выходом блока 4 управления, а установочный вход соединен с четвертым входом блока 4 управления. , Блок 4 управления содержит первый 12, второй 13, третий 14 и четвертый 15 элементы И, первый 16 и второй 17 триггеры и элемент ИЛИ 18. Устройство для разбраковки микросхе работает следующим образом. Микросхема с эталонной информацией устанавливается во второй блок 3 контами - в первый блок 2 контактов. В исходном состоянии счетчики lull, триггеры 16 и 17 находятся в нулевом состоянии. На пятый вход блока 4 управления подаются тактовые сигналы. При подаче на четвертый вход блока 4 управления разрешающего потенциала начинается работа адресного счетчика 1 в 0 режиме счета тактовых сигналов. При этом происходит последовательный перебор адресов микросхем, установленных в первый 2 и второй 3 блоки контактов. и выборка содержащейся по этим адресам информации. Информация из микросхемы с дефектными битами считывается всегда в прямом коде и поступает на первые входы блока элементов И 5 С помощью счетчика 11 циклов, нулевые выходы которого соединены с вторыми входами блока 1О формирователей четности, происходит инвертирование информации, считываемой из микросхемы с эталонной информацией, которая поступает на вторые входы блока элементов И 5. Блок элементов И 5 производит поразрядное сравнение поступающих кодов. При этом признак сравнения вырабатывается тогда, когда в одном из разрядов микросхемы с дефектными битами находится 1 (исходное состояние О), а ъ этом же разрвде микросхемы с эталонной информацией находится О, Тогда на выходе элемента ИЛИ 6 вырабатывается сигнал 1, который устанавливает триггер 16 в единичное состояние, инверсный выход которого не позволит перейти в конце полного цикла проверки р единичное состояние триггера 17. Разрешающий потенциал на инверсном выходе триггера 17 разрешит дальнейшую работу по проверке, а именно в счетчик 11 циклов с выхода элемента И 14 в конце,первого цикла поступит сигнал, переводящий счетчик 11 в состояние 00...01. После этого вновь произойдет цикл проверки с той лишь разницей, что по первому разряду информация в блоке элементов И 5 сравнивается в прямых кодах. Если информация, считываемая из микросхемы с дефектными битами, не подошла под информацию, считываемую из микросхемы с эталонной информацией, то в счетчик 11 вновь добавляется еди- ница, и он переходит в состо5шие О0..,10. Таким образом, циклы сравнения с новыми видами эталонной информации повторяются , до тех пор, пока не будет подобран вариант, соответствующий положению дёфектных битов или пока не переберутся все варианты. В последнем случае данное сочетание микросхем с эталонной ин формацией и дефектными битами не реал зуется и одна из них должна быть заменена. Таким образом, в предложенном устройстве возможность подбора микросхем с дефектными битами увеличивается в несколько раз, если микросхемы исцояьзуются в постоянных запоминающих устройствах с поразрядным обратным кодир ванием. Технико-економическое преимущество предложенного технического решения заключается либо в больщем проценте использования микросхем с дефектными би тами, либо в более быстром подборе микросхем с эталонной информацией и микросхем с дефектными битами, что существенно увеличиваетпроизводительность труда при разбраковке микросхем памяти. Формула изобрете ни я Устройство для разбраковки микросхе содержащее адресный счетчик, выходы которого соединены с первым входом блока управления и являются выходами устройства, блок элементов И, входыпервой группы которого являются одними информационными входами устройства, а выходы соединены с йходами элемента ИЛИ, выход которого соединен с вторым входом блока управления, третий, четвертый, пятый входы которогчэ являются соответственно первым, вторым, третьим управляющими входами устройства, сч.ётный вход адресного счетчика соединен с первым выходом блока управления, а установочный вход - с четвертым входом блока управления, отличающеес я тем, что, с целью повыщения быстродействия, в него введены счетчик циклов и блок формирователей четности, выходы которого соединены с входами второй группы б/1ока элементов И, первые входы блока формирователей четности являются другими информационными входами устройства, а вторые входы соединены с выходами счетчикг циклов, счетный вход которого соединен с вторым входом блока управления, а установочный вход соединен с четвертым входом блока управления. Источники информации, принятые во внимание при экспертизе 1.Устройство для записи блоков постоянной памяти Ц52729.000.15 ВУС-32-ОО1. 2.Авторское свидетельство СССР по заявке № 2773895/24, кл. Gil С 17/00, 01.06.79 (прототип).

Авторы

Даты

1982-10-23—Публикация

1981-04-06—Подача