Изобретение относится к вычислительной технике, а именно к запоминающим устройствам модульного типа и может быть использовано при построении высоконадежных запоминающих устройств с коррекцией разрядных оиш&ж и обнаружением адресных ошибок большой кратности.

Известно запоминающее устройство с автономным контролем содержащее полусумматор для определения суммы по модулю два данных и соответствующих им адресов. В нем для хранения информации о четности (нечетности) используется дополнительный разряд даданных 111.

Недостатком этого устройства является невозможность обнаружения четных многократ- . ных адресных ошибок, исправление разрядных ошибок и отделение адресных ошибок от разрядных.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство с автономным контролем, содержащее модульный накопитель, соединенный со средствами обнаружения и коррекш1И многократных модульных ошибок 2.Недостатком зтого устройства является невозможность обнаружения адресных ошибок, возникающих при отказах адресных цепей, что снижает достоверность выборки информации из накопителя. Действительно, объем электроники обрамления накопителя в зависимости от типа запоминающего устройства достигает 10-15% от объема электроники накопителя. Следовательно, при одинаковой интенсивности отказов электрорадиозлементов, выполненных на основе идентичной технологйи каждый 9-10 отказ будет приходиться на отказ электроники обрамления. Причем ащ)есные блоки, реализованные на современной элементной базе, также могут приводить к многократным ошибкам в соседних (принадлежащих одной микросхеме) разрядах кода адреса.

Цель изобретения - повышение надежности устройства за счет повышения достоверности выборки информации из запоминающего устройства, что достигается обнаружением ошибок в адресных цепях.

Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее накопитель, входы первой группы которого являются адресными входами устройства, входы второй группы соединены с входами первого блока формирования сигналов четности и входами первого блока формирования контрольных сигналов по нечетному модулю и являются числовыми входами устройства, выходы первого блока формирования сигаалов четности соедииены с входами третьей группы накопителя, выходы первой группы которого соединены с входами второго блока формирования контрольных сигналов по нечетному модулю и одни1 ш из входов регистра числа, выходы которого являются числовыми выходами устройства, другие входы регистра числа соединены с выходами мультиплексора, одни из информационных входов которого соединены с выходами дешифратора, одни из входов которого соединены с выходами первого блока сравнения, одни из входов которого соединены с выходами второй группы накопителя, выходы третьей группы которого соединены с одним из входов второго блока сравнения, другие входы которого соединены с выходами второго блока формирования сигналов четности, а выходы соединены с другими информационными входами мультиплексора и другими входами дешифратора, введены третий блок сравнения, первый и второй элементы ИЛИ, третий и четвертый блоки формирования сигналов четности и шифратор, входы которого соеданены с адресными входами устройства, а выходы с одними из входов .третьего и четвертого блоков формирования сигналов четности, другие входы третьего блока формирования сигналов чётности соединены с выi ходами первого блока формирования конт ролььш1х сигналов по нечетному модулю, а выходы - с входами четвертой группы накопителя, другие входы четвертого блока формирования сигналов четности соединены с выходами второго блока формирования контрольных сигналов по нечетному модулю, а выходы соединены с другими входами первого блока сравнения, первый вход третьего блока сравнения соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами первого блока сравнения, второй вход третьего блока сравнения соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами второго блока сравнения, а выход третьего блока сравнения соединен с управляющим входом мультиплексора и является контрольным выходом устройства.

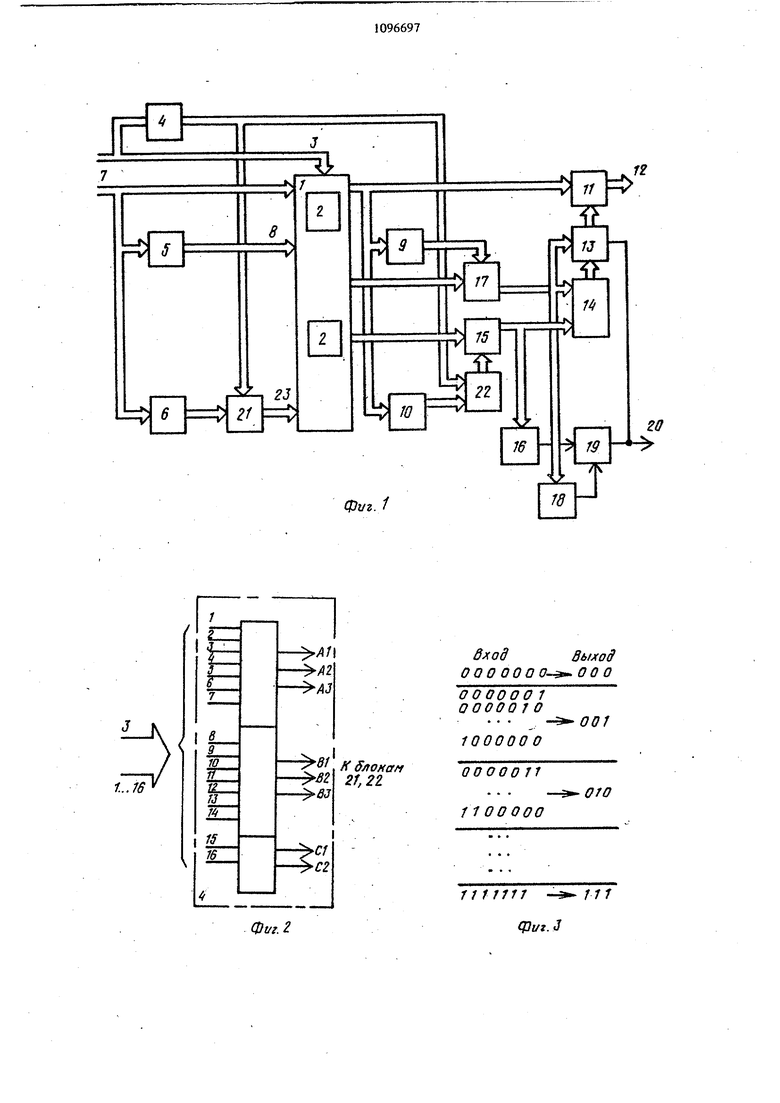

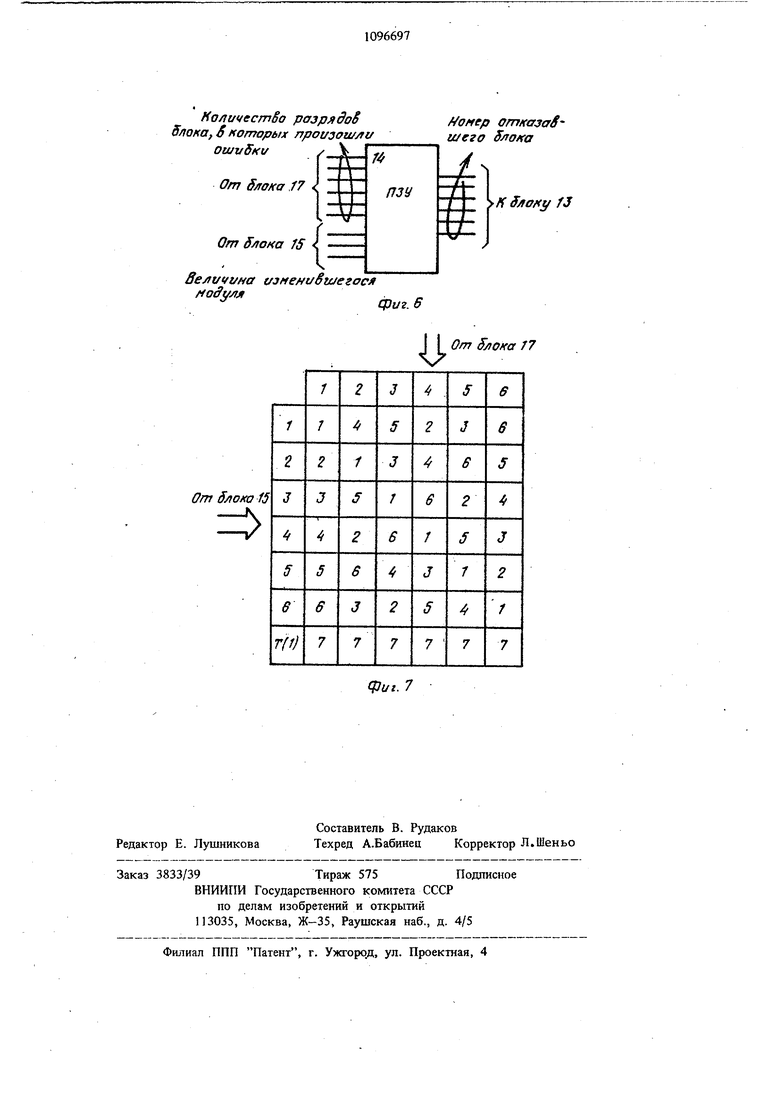

На фиг. 1 представлена структурная схема запоминающего устройства с автономным контролем; на фиг. 2 - пример реализации шифратора на основе микросхем К556РТ4 для случая 16 адресных шин; на фиг. 3 алгоритм кодирования информации в шифраторе; на фиг. 4 - пример реализации блоков формирования контрольных сигналов по модулю 7 (для 36 информационных разрядов) на фиг. 5 - пример реализации блоков формирования сигналов четности; На фиг. 6 - пример реализации дешифратора на основе 3 постоянного запоминающего устройства (ПЗУ а на фиг. 7 таблица декодирования дешифратора для модуля 7. Запоминающее устройство с автономным контролем, содержит накопитель 1, состоящий из блоков 2 памяти, входы первой группы 3 накопителя 1 соединены с входам шифратора 4 и являются адресными входами устройства, входы второй группы накопителя 1 соединены с входами первого блока 5 фо мирования сигналов четности, с входами первого блока 6 формирования контрольных / сигналов по нечетному модулю и является числовыми входами 7 устройства, выходы пе вого блока 5 формирования сигналов четности соединены с входами третьей группы 8 накопителя 1, выходы первой группы которого соединены с входами второго блока 9 формирования сигналов четности, входами второго блока 10 формирования контрольных сигналов по нечетному модулю и с одним из входов регистра 11 числа, выходы которого являются числовыми выходами 12 устройства, а другие входы соединены с выходами мультиплексора 13, один из информационных входов соединен с выходами дешифратора 14, одни из входов которого соединены с выходакш первого блока 15 сравнения и входами первого элемента ИЛИ 16, другие входы дешифратора 14 соединены с выходами вторюго блока 17 сравнения, дрзггн МИ информационными входами мультиплексора 13 и входами второго элемента ИЛИ 18 выходы первого 16 и второго 18 элементов ИЛИ соединены соответственно с первым и вторым входами третьего блока 19 сравнения, выход которой соединен с управляющим входом мультиплексора 13 и является контрольным выходом 20 устройства, один и входов первого 15 и второго 17 блоков сравнения соединены соответственно с выходами второй и третьей группы накопителя 1. Устройство содержит третий 21 и четвертьш 22 блоки формирования сигналов четности, один из входов которых объединены и соединены с выходами шифратора 4, а выходы соединены соответственно с входами четвертой группы 23 накопителя 1 и другими входами первого блока 15 сравнения, выходы второго блока 9 формирования сигналов четности соединены с другими входами второго блока 17 сравнения. Устройство работает следующим образом. В каждом цикле записи на адресные входы 3 поступает код адреса, по которому необходимо произвести запись числа. В это время по числовым входам 7 поступает код 97 числа, подлежащий записи в данном цикле записи. При этом информашюнные разряды записываются в накопитель 1 по входам второй группы. По входам третьей группы 8 накопителя 1 записываются признаки четности, которые вырабатываются следующим образом: для всех первых информационных разрядов с каждого блока памяти образуется первый признак четности (нечетности), для всех вторых разрядов - второй и т.д. Количество таких разрядов равно разрядности блока памяти и определяется величиной выбранного нечетного модуля А. Для А-7 имеем разрядность К 4 равную 6. Для других значений А значения К можно найти из таблицы. В блоке 6 образуется вычет по модулю А (фиг. 4). Принцип получения вычета следующий: если А - нечетный выбранный модуль, то количество блоков памяти и их разрядность (максимальная для выбранного значсршя А) определяется величиной (А-1). Количество контрольных разрядов, вырабатываемых блоком 6, определяется из выражения ,где Cog,jA - целая часть числа) и вырабатьгеаются они последующему алгоритму. Всем (А-1) разрядам с первого блока памяти присваивается вес 1. Всем (А-1) разрядам с второго блока памяти присваивается вес 2, и т.д. Всем (А-1) разрядам (А-1) блока памяти присваивается вес (А-1). Разряды кода числа в соответствии с присвоенными весами поступают на вход соответствующего формирователя, определяющего значение контрольного разряда выбранного модуля А. Для получения веса не равного степени двойк:и, необходимо разряд с таким весом подать на несколько входов с различными имеющимися весами. Получет1ый вычет поступает на один из входов блока 21, на другие входы которого поступают контрольные разряды с шифратора 4, полученные на основе алгоритма, приведенного на фиг.-3, или ему аналогочному. На фиг. 5 представлен пример, показывающий принцип соединения выходов с блоков 6 и 4 и приншш получения контрольных разрядов, записываемых по входам четвертой группы 23 накопителя. Таким образом, после записи имеем: информационн те разряды, количество которых (A-l)x(A-l), ко1ггрольные разряды, количество которых К4 + Ai-, Aj. В таблице приведены различные характеристики, которые позволяют вь1брать нужный модуль для коррекции ошибки при заданном

количестве информационных разрядов. При считывании код числа поступает в регистр 11 и на блоки 9 и 10. На входы блоков 15 и 17 из накопителя 1 поступают значения контрольных разрядов: на блок 15 , , а на блок 17- контрольных разрядов.

На дрзтие входы блоков 15 и 17 поступают сформированные из считанных информационных разрядов контрольные разряды. После поразрядного сравнения в блоках 15 и 17 определяется код изменившегося модуля в блоке 15 и номера отказавшихся разрядов в блоке 17, которые поступают на элементы ИЛИ 16 и 18, и на входы дешифратора 14. В дешифраторе 14 происходит (фиг. 7) опред ление номера отказавшего блока памяти, а в мультиплексоре 13 происходят подключение отказавших разрядов к тому блоку памяти, в котором они произошли. В рЬгистре И по соответствуюшим входам производится коррекадя информации. Элементы ИЛИ 16, 18 и блок 19 сравнения используются для отделения адресных ошибок от разрядных и блокировки коррекции, когда произошла адресная ошибка. Действительно, если произошла

ошибка в информационных разрядах.то дол-

жен быть код как на выходе блока 15, так и на выходе блока 17, тогда злементы ИЛИ 16 и 18 вырабатывают логические единицы и блок 19 выдает сигнал сравнения. Если ошибка произошла в адресных целях, то код будет только на выходе блока 15. Следовательно, логическую единицу вырабатьтать будет только элемент ИЛИ 16 и блок 19 выдаст сигнал сравнения. Если ошибка про. изошла в адресных целях, то код будет только на выходе блока 15. Следовательно, логическую единицу вырабатывать будет только злемент ИЛИ 16 и блок 19 выдаст сигнал несравнения,, который блокирует работу мультиплексора 13 и известит внешнее устройство (на фиг, 1 не показано) или оператора о наличии ошибки в выборке числа по выходу 20. В зависимости от принятого алгоритма всей системы возможно либо повторное считывание, либо останов, либо чтолибо другое.

I

Техннко- экономическое преимущество предлагаемого устройства по сравнению с прототипом заключается в возможности обнаружения адресных ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Запоминающее устройство с коррекцией ошибок (его варианты) | 1984 |

|

SU1188790A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее накопитель, входы первой группы которого являются адресными входами устройства, входы вто-( рой группы соединены с входами первого блока формирования сигналов четности и входами niepsoro блока формирования контрольных сигналов по .нечетному модулю и являются числовыми входами устройства, выходы/первого блока формирования сигналов четности соединены с входами третьей группы накопителя, выходы первой группы которого соединены с входами второго блока форми1юва1шя сигналов четности, входами второго блока формирования контрольных сигналов по нечетно. му модулю и одними из входов регистра числа, выходы которого являются числовыми выходами устройства, другие входы регистра числа соединены с выходами мультиплексора, одни из информационных входов которого соединены с выходами дешифратора, один из входов которого соединены с выходами первого блока сравнения, одни из входов которого соединены с выходами второй группы накопителя, выходы третьей группы которого соединены с одним из входов второго лока сравнения, другие входы которого соединены С выходами второго блока формирования сигналов четности, а выходы соединены с другими информацио1шыми входами мультиплексора и другими входами дешифратора, отличающееся тем, что, с целью повышения его надежности за счет повыше1{ия достоверности выборки информации, в него введены третий блок сравне1шя, первый и второй злементы ИЛИ, третий и четвертый блоки формирования сигналов четности и шифратор, входы которого соединены с адресными вхо- дами устройства, а выходь - с одним jf входов третьего и четвертого блоков форми(Л рования сигналов четности, другие входы третьего блока формирования сигналов четс ности соединены с выходами первого блока формирования контрольных сигналов по неS четному модулю, а выходы - с входами четвертой группы накопителя, другие входы четвертого блока формирования сигналов чет:О 3: ности соещщены с выходами второго блока формирования контрольных сигналов по нечетному модулю, а выходы соединетг с Другими входами первого блока сравнения, пер:О вый вход третьего блока сравнения соединен с выходом первого злемента ИЛИ, входы которого соединены с выходами первого блока сравнения, второй вход третьего блока сравнения соединен с выходом второго злемента ИЛИ, входы которого соединены с выхода- , ми второго блока сравнения, а выход третьего .блока сравнения соединен с управляюищм входом мультиплексора и является контрольным выходом устройства.

Кратность исправляемой ошибки, количество возможных блоков памяти

Кратность обнаруживаемой адресной ошибки

Относительная избыточность

18

16

10

12

2i-l 0,110,08 0,07

Фиг. 2

Сриг. J

Seel Ж/

дес Sec 2 От 5лока 6

К 5л оку 21

Н 5лону 1

Количество разрлдоВ лакаf 6 которых npotf3ou//tif owvSKv

От S/ro/fff /7

От f/fOf a 15

Be/ftft/t/Ha изненившегосл

ноду/гл

фиг. о

отказавшего S/Jotfa

К ff/iof y /J

От /lOffO 77

фиг. 7

| Т | |||

| Патент США N 3573728, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-06-07—Публикация

1982-07-23—Подача