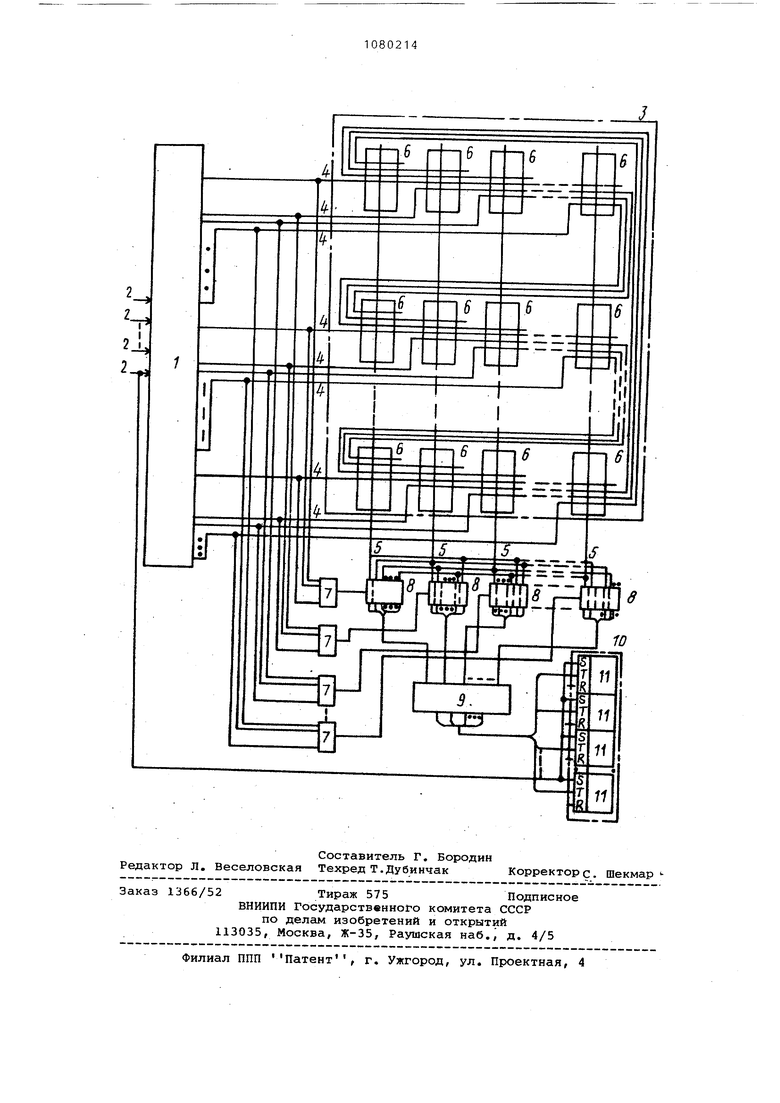

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах хранения дискретной информации и при построе нии модулей специализированных процессоров, а также в устройствах защиты, шифрования и передачи информации. Известно запоминающее устройство с хранением фиксированной информации, содержащее дешифратор адреса, элементы И, входы которых подключены к соответствующим выходным шинам накопителя, а их выходы поразрядно соединены с входами группы элементо ИЛИ 1. Недостатком этого устройства является сложность, обусловленная наличием большого числа запоминающих элементов в накопителе, что приводи также к снижению информационной емкости устройства и надежности его работы. Наиболее близким к предложенному по технической сущности является постоянное запоминающее устройство, содержащее дешифратор адреса, входы которого подключены к адресным шинам накопитель, в пересечении входных и выходных шин которого расположены запоминающие элементы, группу элементов ИЛИ, входы которых поразрядно соединены с выходами элементов И соответствующих групп, управляющие входы которых подключены к выходам элементов ИЛИ, входы которых соединены с соответствующими выходами дешифраторов адреса, подключенными к входным шинам накопителя, и регист числа 23. Известное устройство не позволяе производить дальнейшее упрощение накопителя и повышение информационной емкости и надежности устройства на основе метода поразрядного обрат ного кодирования. В накопителе такого устройства для хранения одного бита информации требуется один запоминающий элемент, а при хранении полупостоянной информации требуется использование одного запоминающего элемента на каждый бит хранимой информации. Преобразование кодов слов информации с преобладающим количест вом нулей, хранящихся в накопителе, в коды слов с преобладаквдим количеством единиц производится путем дополнительной поразрядной записи кодов единиц в определенные разряды считанных из накопителя слов информации. Дополнительная поразрядная запись единиц к считанным из накопителя словам осуществляется путем распределения каждого выхода дешифратора адреса по входам элементов ИЛИ адресной части устройства, что требует больших затрат оборудования При хранении всех наборов кодов определенной разрядности схема такого устройства теряет свои преимущества по затратам оборудования по сравнению с обычной схемой постоянного запоминакхцего устройства с хранением информации без использования поразрядного метода обратного кодирования. Все это усложняет устройство, что приводит к снижению его надежности и препятствует повышению его информационной емкости. . Целью изобретения является упрощение устройства и повышение его информационной емкости путем уменьшения числа ячеек памяти, необходимых для хранения одного бита информации. Поставленная цель достигается тем, что в постоянном запоминающем устройстве, содержащем накопитель и дешифратор адреса, входы которого являются адресными входами устройства, а выходы соединены с адресными шинами накопителя и входами соответствующих элементов ИЛИ первой группы, выходы которых подключены к управляющим входам элементов И соответствующих групп, выходы которых соединены с соответствукадими входами элементов ИЛИ второй группы, регистр числа, выходы элементов ИЛИ второй группы подключены к соответствующим входам регистра числа, установочные входы которого соединены с адресным входом старшего разряда адреса дешифратора адреса, разрядные шины накопителя соединены с входами элементов И соответствующих групп в соответствии с формулой М (S + Р) rood п, где М - номер выходной строки накопителя;S - номер..элемента И (,1,2,... ...,п-1), Р 0,1,2,...,п-1; п - разрядность хранимых слов. В накопителе, содержащем в пересечении адресных и разрядных шин элементы памяти, входы п-1 элементов памяти, расположенных в каждой строке, начиная с второго элемента, соединены с входами п-1 элементов памяти последующей строки, начиная с первого элемента. На чертеже представлена функциональная схема предложенного устройства. Устройство содержит дешифратор адреса 1, входы которого подключены к адресным шинам 2, накопитель 3, в пересечении входных 4 и выходных 5 шин которого расположены запоминаквдие элементы 6, элементы ИЛИ 7 первой группы, элементы И 8 соответствукнцих групп, элементы ИЛИ 9 второй группы и регистр 10 числа, состоящий из счетных триггеров 11. Выходы дешифратора адреса 1 подключены, к соответствукадим входным шинам 4 накопителя 3 и к входам соответствующих элементов ИЛИ 7 перво группы, выходами соединенных с управляющими входами элементов И 8 соответствующих групп, выходы которых поразрядно соединены с соответствующими входами элементов ИЛИ 9 второй группы, выходы которых пораз рядно подключены к счетным входам триггеров 11 регистра 10 числа, еди ничные входы триггеров которого сое динены с адресной шиной старшего разряда адреса 2, Накопитель устройства содержит р- выходных шин и по п запоминающих эли-1ентов в каждой строке. При этом входные шины, объединяющие запоминающих элементов предыдущей стр ки накопителя, начиная со второго элемента, и запоминающих элементов очередной строки накопителя, начиная с первого элемента, проложе ны со сдвигом вправо с шагом на оди запоминающий элемент. Выходные шины накопителя скоммутированы на информационные входы элементов И в соответствии с формулойМ {S + Р) mod п, где М - номер выходной шины накопителя;S - номер элемента И. (S 0,l,2,3,..n-:i) ; Р 0,1,2,3, ..., n-1 ; п - разрядность хранимых слов. Такая организация накопителя позволяет во всем его объеме хранит информацию в сжатой форме так, что каждое очередное сжатое слово отли чается от предыдущего значением од ного разряда, а данное соединение выходных шин накопителя с информационными входами элементов И 8 обе печивает на выходе п .элементов ИЛИ сдвиг п-разрядного i-ro слова отн сит(ельно (i-l)-ro на один разряд вправо. В накопителе устройства хранятс прямые коды слов информации, записанных в сжатой форме, другие комб нации слов могут быть образованы путем инверсий. Так, например,при рассмотрении всех возможных четыре разрядных кодовых комбинаций оказы вается, что кодовые комбинации 0000, 0001, 0010, 0101, 1011, ОНО, 1100, 1000 можно рассматривать как комбинации 1111, 1110, 1101, 1010, 0100, 1001, ООН, 0111. Отсюда следует, что для хранения половины комбинаций слов запоминающие элементы не нужны, так как они могут быть сформированы из комбинаций слов, записанных в прямом коде. Следовательно, кодам слов, хранящихся в накопителе, будут соответствовать адреса, содержащие в старшем разряде нуль, а кодам слов, образуемым путем инверсий, соответствуют адреса, содержгицие в старшем разряде адреса единицу. Устройство работает следующим образом. После расшифровки адреса (старший разряд адреса содержит О) на соответствукяцем выходе дешифратора возникает сигнал, который возбуждает определенную входную шину накопителя, а через соответствующий элемент ИЛИ 7 первой группы открывает определенный элемент ИВ. При этом считывается прямой код слова, хранящегося в запоминающих элементах, охваченных возбужденной входной шиной накопителя. Считанное слово через открытый элемент И 8 и г элементов ИЛИ 9 второй группы поступает на счетные входы триггеров 11 регистра 10 числа. При формировании обратных кодов слов (старший разряд адреса содержит ) сигналом логической единицы старшего разряда адреса устанавливаются в триггеры всех разрядов регистра 10 числа. Одновременно расшифровывается згщанный гщрес и аналогичным образом считывается из накопителя соответствующее слово, после-занесения которого по счетным входам триггеров 11 на регистр 10 числа в нем образуется обратный код этого слова. Технико-экономический эффект от использования предложенного устройства заключается в упрощении устройства и повышении его информационной емкости и надежности в результате уменьшения числа запоминающих элементов в накопителе при хранении в нем одного и того же объема информации и уменьшения количества входов в элементах ИЛИ адресной части устройства, так как исключена дополнительная поразрядная запись единиц в определенные разряды считанных из накопителя слов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство | 1978 |

|

SU781974A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

1. ПОСТОЯННОЕ 3AnOMHHAR»lEE УСТРОЙСТВО, содержащее накопитель и дешифратор адреса, входы которого являются адресными входами устройства, а выходы соединены с адресными шинами накопителя и входами соответ- ствуивдих элементов ИЛИ первой группы, выходы которых подключены к управляющим входам элементов И соответствующих групп, выходы которых соединены с соответотвукядими входами элементов ИЛИ второй группы, регистр числа, отличающееся тем, что, с целью упрощения устройстваи повышения его надежности путемуменьшения числа ячеек памяти, необходимых для хранения одного бита информации, выходы элементов ИЛИ второй группы подключены к соответ- ствукицим входам регистра числа, установочные входы которого соединены с адресным входом старшего разряда адреса дешифратора адреса, разрядные шины накопителя соединены с входами элементов И соответствующих групп в соответствии с формулойM=(S-«-P|modn ,где М - номер выходной строки накопителя; 5 - номер элемента И

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1974 |

|

SU526020A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU652616A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-03-15—Публикация

1980-03-20—Подача