,.:;. .-, Г V - / .:-, :/

Изобретение относятся к обласги вычислигельной техивки и можетр быть использовано в аь1числит«л{ ных усГройсгвах различного назначения.

Известны мик ропроиессорные вычислительные с жестким управлением (1| и 2, содержащие арифмегическо-логичесжий блок, блок .регистре®, блок дешифрации команд, блоки обмена ииформадиеи, регистр сзоса-ояний и узел распределения синхросигналов. Однако наращивание разГрадности обрабатываемой информации и-таких микропроцессорных вычислительных-системах приводит к значительному снижению их быстродействия, в изменение ей стемы команд невозможно.

Известна также микропроцессорная вычислительная система с м0кропрограм{у1ш 1М управлением vp, содержащая однотипные устройства выполнения ошрапий в однотипные устройства микропрограммного уюК) ления, причем Каждое однотипное устройство выполнения операций содержит ариф метическо-логичеокий блок, сдригатель.

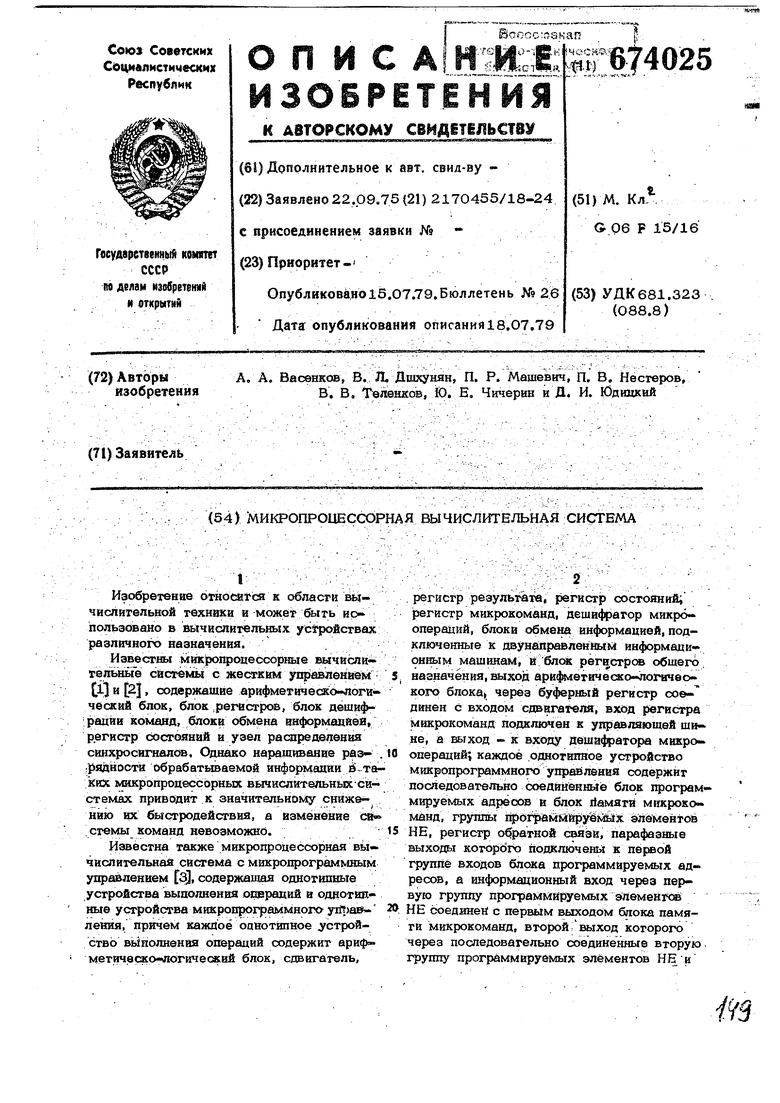

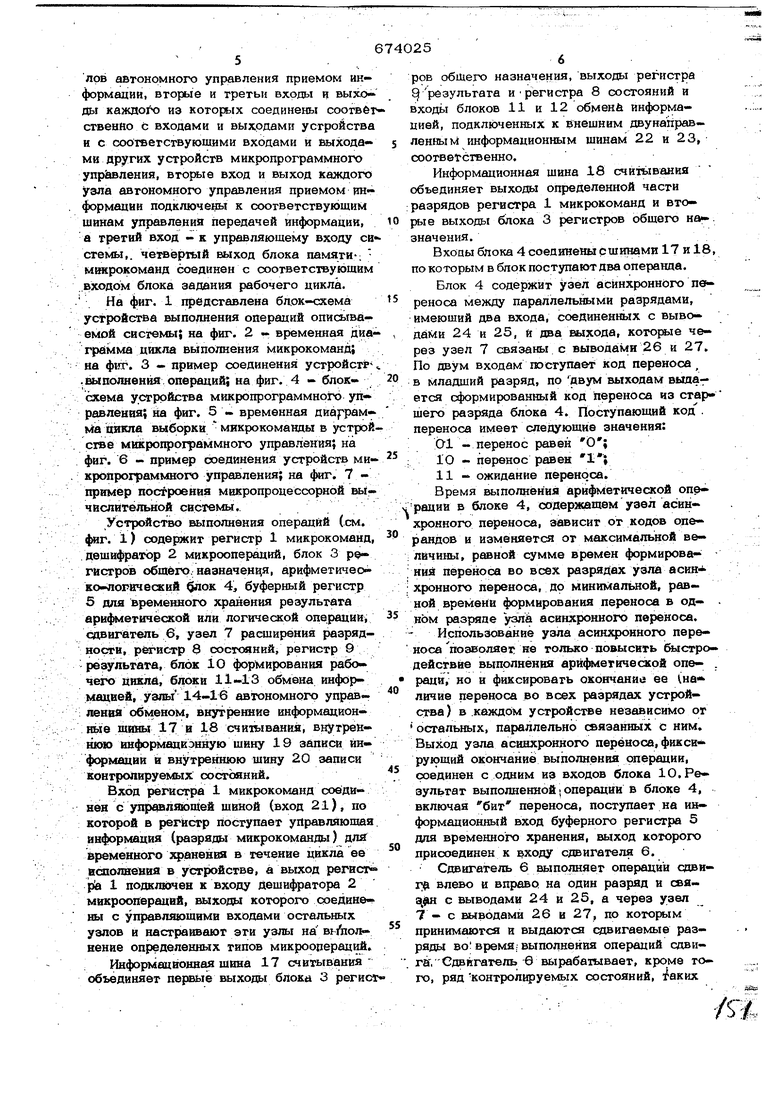

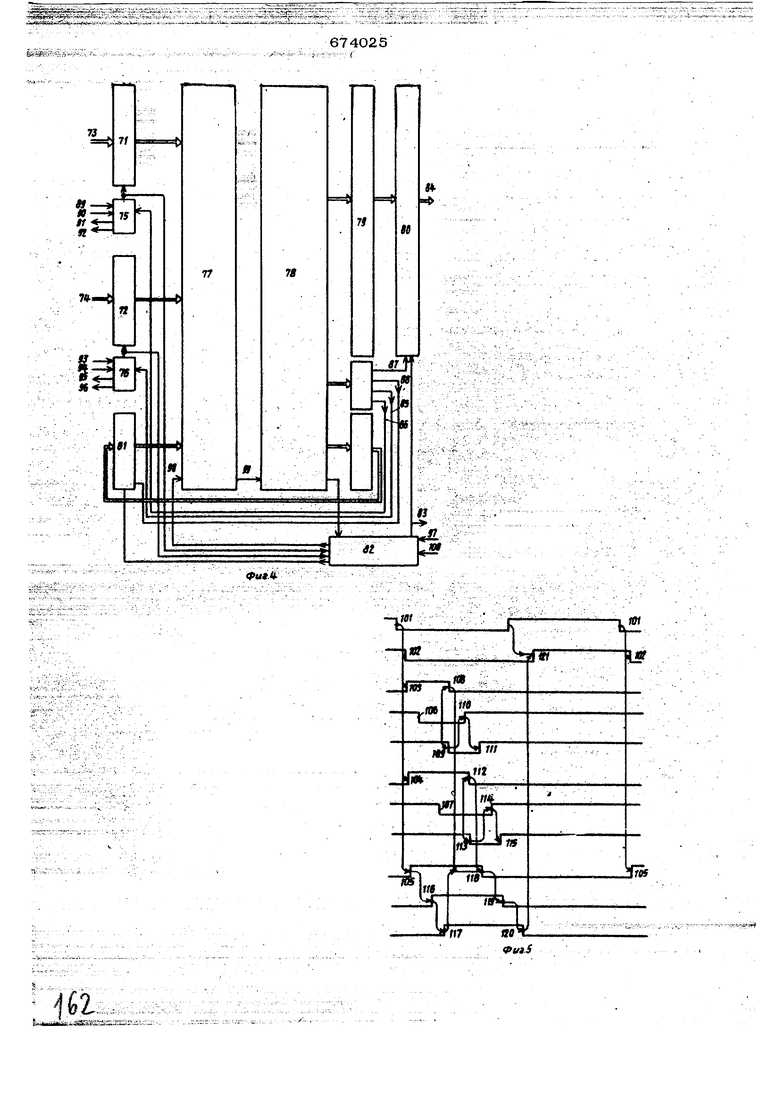

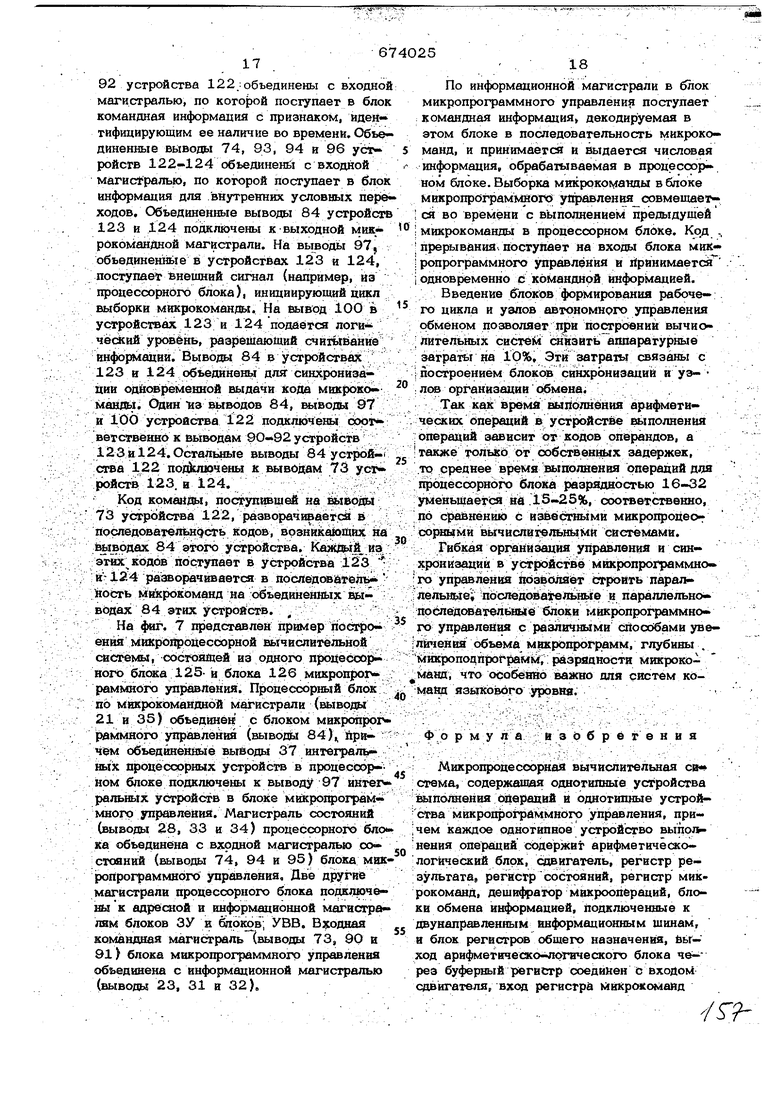

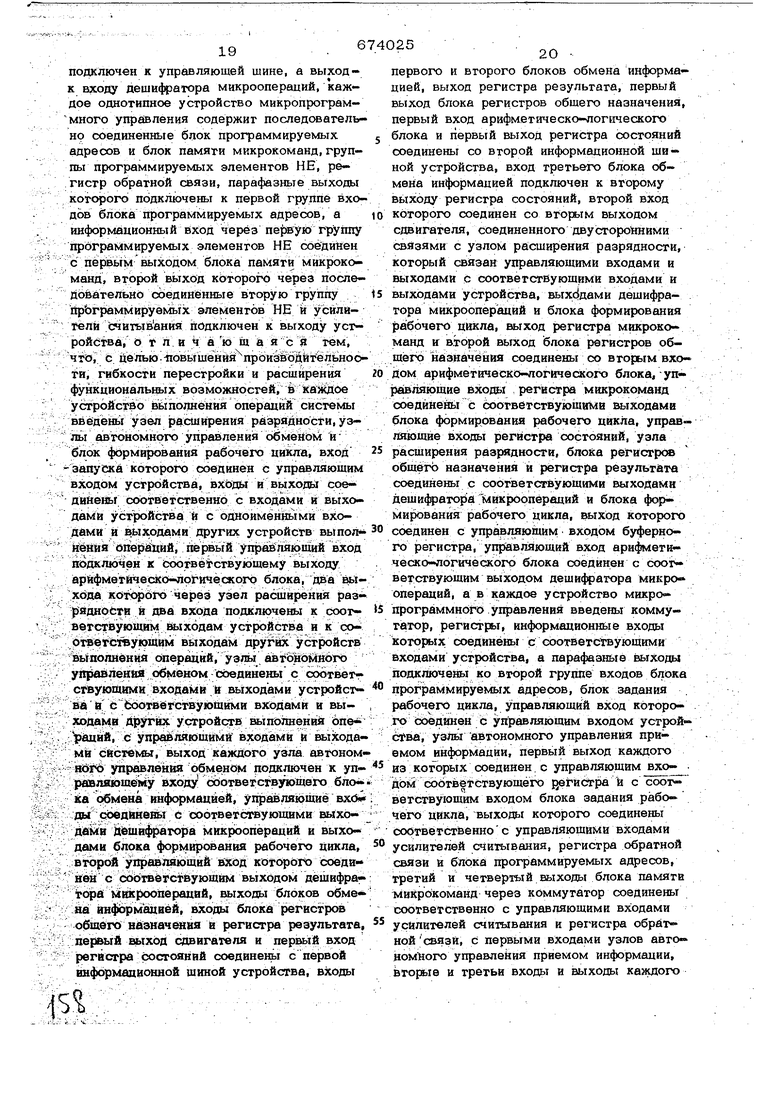

. регистр результата, регистр состояний; регистр микрокоманд, дешифратор микроопераций, блоки обмена информацией, подкл{0ченные к двунаправленным информаиионвым машинам, и блок регистре общего назначения, выход арифметическо-логичео кого блокад через буферный регистр соединен С входом сдвигагеЛЯ, вход регистра микрокоманд подключен к упр авляющей шине, а выход - к входу йвшафратора микроопераций; каждое однотипное устройство микропрограммного управления содержит последовательно соединенные блок программируемых адресов и блок йамяти микрокоманд, группь прОг1|й1мй1 руёШх ЙЛй 1енто& НЕ, регистр обратной связи, парафазные выходад которого подключен. к первой группе входов блока программируемых адресов, а информационный вход через первую группу программируемых элементов НЕ соединей с первым выходом блока памяти микрокоманд, второй; выход которого через последовательно соединенные вторую группу программируемых элементов Н13и убилители считывания подключен к выходу устройства. Основными недостатками этой микропроцессорной вычислительной системы являются значительное количест- во дополнительных схем в эаконченцой микропроцессорной. ш 1числительной сйсте ме, необходимых для выработки такговых синхросигналов, для организааии логики сопряжения и синхронизации с другП1Ми блоками ЭВМ; снижение быстродействия пр|й расширении разрядности обьедйн€ НиеМ; овнотипных устройств выйШйёйияб1т:ёра« ций в параллельный процессорньтй блок за dfet последовательного прохождения сигналов переноса; отсутстеие функциональной гибкости однотипного устройсива микропрограммного управления лри расширении разрядности микрокоманды и нараишваний объема Мйкрог рограмм. Целью изобретения является повышение производительности, гибкости Перестройки и расширение функциональньгх возможностей системь. Это Достигается тем, что в каждое устройство выполнения операций предлагаемой системы введены узел расши psaws разрядности, узлы автономного управления обменом и блок формирования рабочв- го цикла, вход запуска яоторогч соединен с управляющим входом .устройсма, вхоjtBji и выходы соединены соответственно с входами и шлходами устройства и с одноШ6й№ Ш входами и выходами других устройств выполнения операций, первый управляющий вход подключей к соответствующему вызюду арифметическо-льгического блока, два выхода которого череЪ узел расширения разрядно ;ти и даа вгюда подключены к соотбетстаующимвьтходам устройства и к соответстеуйшим выходам других устройств выполнения операций, узлы автономного управления обменом сое динены с ооответствующими входами ивы ходами устройства и с соответствующими входами и выходами других устройс№ вы волнения операций, с управляющими входа ми и выходами системы, выход каждого узла автономного управления обменом под ключен к управляющему входу соответствующего блока обмена информацией, управ ляющие входа соединень с соответстдаующйми выходами дешифратора микроопера(ций и выходами блока формирования рабо чего цикла, второй управляющий вход ко- тё Е ШвШ ёй е боЬтвбТеётвующйм выходом д эшифрагора микроопераций, выходы блоков обмша информацией, входы бпокй регистров общетчэ назначения И регистра результата/первый аыход сдайгателя и первый вход регистра состояний соединены с первой информационной шиной устройства, входы первого и второго блоков обмена информацией, выход регистра результата, первый выход блока регистров общего назначения, первый вход арифметичеоко-логического блока и первый выход регистра состояний соединены со второй информационной шиной устройства, вход третьего блока обмена информацией подключен к второму выходу регистра состояний, второй вход которотчэ соединен со вторым выходом слв.игателя, соединенного двусто роннимй связями с узлом расширения разрядности, который связан управляющими входами и выходами с соответствующими входаМи и выходами устройства, ыь;1;коДа- ми дешифратора микроопераций и блока формирования рабочего цикла, выход регистра МШсрЬкоманд и в горой ньгход блока регистров общего назначения соедйнень со Вторым входом арифметическо-логичесн. кого блока, управляющие входы регистра микрокоманд соединены с оэответствующйми выходами блока формирования рабрче- : го цвклд, управляющие входы регистра со стояний, узла расширения разрядности, блока регистров общего назначения в регист- ра результата соединены с соответствулошимв выходами дешифратора микроопераций и блока формирования рабочего цикла, выход которого соединен с управляющим входом буферного регистра, управляющий вход арифметическо-логичесЛсого блока ооединбн с Соответствующим выходом дешифратора микроопераций, а в каждое устройство микропрограммного управления ввв день коммутатсф, регистры, информационные входы которых соединены с сортеет - сюующАми входами устройства, а парафаань выходы подключены ко второй группе входов блокапрограммируемых адресе, блок задания рабочего цикла, управляющий вход соединен с Управляющим входом устройства, узлы автономного управления приемом информации, первый вьтход каждого из которых соединен с управляющим йходом соответствующего регистра и с соответствующим входом блока задания рабочего цикла, выходы которого соединены соответственно с управляющими входами усилителей считывания, регистра обратной связи и блока программируемых адресов, третий и четвертый выходы блока памяти микрокоманд через коммутатор соединены соо1ветственно с управляющими входами усилителей считывания и регист- . ра обратной связи, с перы,1ми входами узлов автономного управления приемом информации, вторые и третьи входы и выходы каждого из которых соединены соотве ственно с входами и выходами устройства и с соответствующими входами и выходами других устройств микропрограммного упр звления, вторые вход и выход каждого узла автономного управления приемом янформации подключены к соответствующим шинам управления передачей информации, а третий вход - к управляющему входу си стемы,. четвёртый выход блока памятимикрокоманд соединен с соответствующим входом блока задания рабочего цикла. На фиг, 1 представлена блок-схема устройства выполнения операций описываемой системы; на фиг. 2 - временная диа грамма цикла выполнения микрокоманд; на фиг. 3 - пример соединения устройст1Р .выполнения операций; на фиг. 4 - блоксхема устройства микропрограммного управления; на фиг. 5 - временная диаррам- ма цякла выборки микрокоманды в устрой сгее микрогфограммного управления; на фиг. 6 - пример соединения устройств микропрограммного управления; на фиг. 7 пример построения микропроцессорной вь1- числительной системы. Устройство выполнения операций (см. 4«г. 1) содержит регистр 1 микрокоманд, дешифратор 2 микроопераций, блок 3 регистров общего назначенця, арифметинеокo- Roгкчecкий ок 4, буферный регистр 5 для временного хранения результата арифметической или логической операции сдвигатель 6, узел 7 расширения разрядности, регистр 8 состоа1ний, регистр 9 результата, блок 1о фор ирования рабочего цикли, блоки 11-13 обмена информацией, у апьг 14-16 автономного управленвя обменом, внутренние информацион- Hbie шноны 17 в 18 считывания, внутреннюю информационную шину 19 записи йнфс мации в внутреннюю шину 20 записи контролируемых состояний. Вход регистра 1 микрокоманд соединен с управляющей шиной (вход 21), по которой в регистр поступает управляющая информация (разряды микрокоманды) для временного хранения в течение ее нсполневия в устройстве, а выход регисг « 1 подключен к входу дешифратора 2 микроопераций, иыходы которого соединены с управляющими входами остальных узлов и настраивбиот эти узлы на вьйголнение определенных типов микроопераций. Информационная шина 17 считывания объединяет ne ffibie выходы блока 3 регист ров общего назначения, выходы регистра результата ирегистра 8 состояний и входь блоков 11 и 12 обмени информацией, подключенных к внещним двунаправ- ленньш информационным шинам 22 и 23, соответственно. Информационная шина 18 счигьшания объединяет выходы определенной части разрядов регистра 1 микрокоманд и втоjbie выходы блока 3 регистров общего на«-. значения. Вхоаы блока 4 соединены сшинами 17 и 18, по которым в блок поступают два операнда. Блок 4 содержит Узел асинхронного переноса между параллельными разрядами, имеюший два входа, соединенных с выводами 24 и 25, d два выхода, которые через узел 7 связаны с выводами 26 и 27. По Двум входам поступает код переноса, в младший разряд, по двум вь1ходам выдается сформированный код переноса из старшего разряда блока 4. Поступающий код . переноса имеет следующие значения: О1 - перенос равен О; 10 - перенос равен 11 - ожидание переноса. Время выполнения арифметической опэ- рации в блоке 4, содержащем узел асинхронного переноса, зависит от кодов операндов и изменяется от максимальной веЛИЧИНЫ, равной сумме времен формирования переноса во всех разрядах узла асинхронного переноса, до минимальной, равной времени формирования переноса в од- . ном разряде узла асинхронного переноса. Использование узла асинхронного переноса позволяет не только повысить &ь1стродействие выполнения арифметической операци, но и фиксировать окончание ее (на« личие переноса во всех разрядах устройства) в .каждом устройстве независимо от остальных, параллельно связанны:х с ним. Выход узла асинхронного переноса, фнксиру1ощий окончание выполнения операции, соединен с одним из входов блока 10. Результат выполненнойоперации в блоке 4, включая бит переноса, поступает на информационный вход буферного регистра 5 для временного хранения, выход которого присоединен к входу сдвигателя 6. Сдвигатель 6 выполняет операции сдви1 влево и вправо на один разряд и свя(Ut с выводами 24 и 25, а через узел 7 - с выводами 26 и 27, по которым принимаются и выдаются сдвигаемые разряды во времЯ: выполнения операций сдвига, Сдввгатель 6 вырабатывает, кроме того, ряд контрол1фуемых состояний, как Знак, Переполиение, Переноо-Заем, Ноль результата, Разрядь сдвига, Четность результата и т.д. Выход сдви гателя 6, связанный с выдачей контроли руемькх состояний, подключен к шине 20, а выход,связанный с выдачей результата операции, - к шине 19. Регистр 8 имеет два направления записи первое из которых евязанЬ с1з&Пйсью контролируемых состояний, а второес записью информации по шине 19. По uikне 19 происходит или запись результата дпер1аций с вьгхода сдвигателя6, или запись информации, поступающей извне через блоки 11-13 в приемники информации Приемниками информации по шине 19 яв1 ляются регистр 9 результата,.любой из ; гистров блока 3 и регистр 8. Выдача информации происходит через блоки 11 и 12 из источников информации, связанных с шиной 17 т.е. из регистров 9 и 8 и из любого регистра блока 3. Выдача tmформации во внешнюю двунаправленную йн формационную шину 28 происходит через блок 13 обмена из регистра 8 состояний, Уз1&| 14-16 автономного упрааЯенйя oeivie M уйравйяют асй ах{йШШй Мрйё- мом и асинхронной ш.шачей информации через соответствующие, связаниъ1е с нимн- блоки 11-13 обмена. Каждый из узлов 14-16 автономнотх) управления обме; 1(1Ьй связан с двУмн внешними даунаправ лённы ми выводам и модуля,, соответственно 29 и 30, 31, и 32, 33 и 34. По вь1водам 29, 31 и 33 поступает во время приема инфоркл&цйи и выдаетсй во ёремя бьтдачи приэнйк, указывающий на наличие иНформацин на соответствующих двунадравленных информационных шинах 22,23 и 28. По выводам 30, 32 и 34 шлдаетейво вирами приема и принимается во вре мя выдачи признак, указывающий на окон- чение приема яостулившей или выдававмой информации а тем самым на отклЬчение соответствующего блбка обмена от внешней магистрали. Выводы 30, 32 и / 33 подключены к входам блока 10. Каждай из узле автономного управления об меном имеет тайжечёШре входа и даа вьгхода, связанных с внутренними блока«м уееро&ееъа. ПерШё два входа оэединё . ны с выходами дешифратора 2 микроопе- раций|| Декодирующего наличие ярйзнаков приема или выдачи через соответствую . щий блок обмена в кбде пбступающей микрокоманды. Вторые два входа схзедйнены с выходами блока 10, ЁЬч-брьгв являются исгочниками сигналов, синхро-

Г

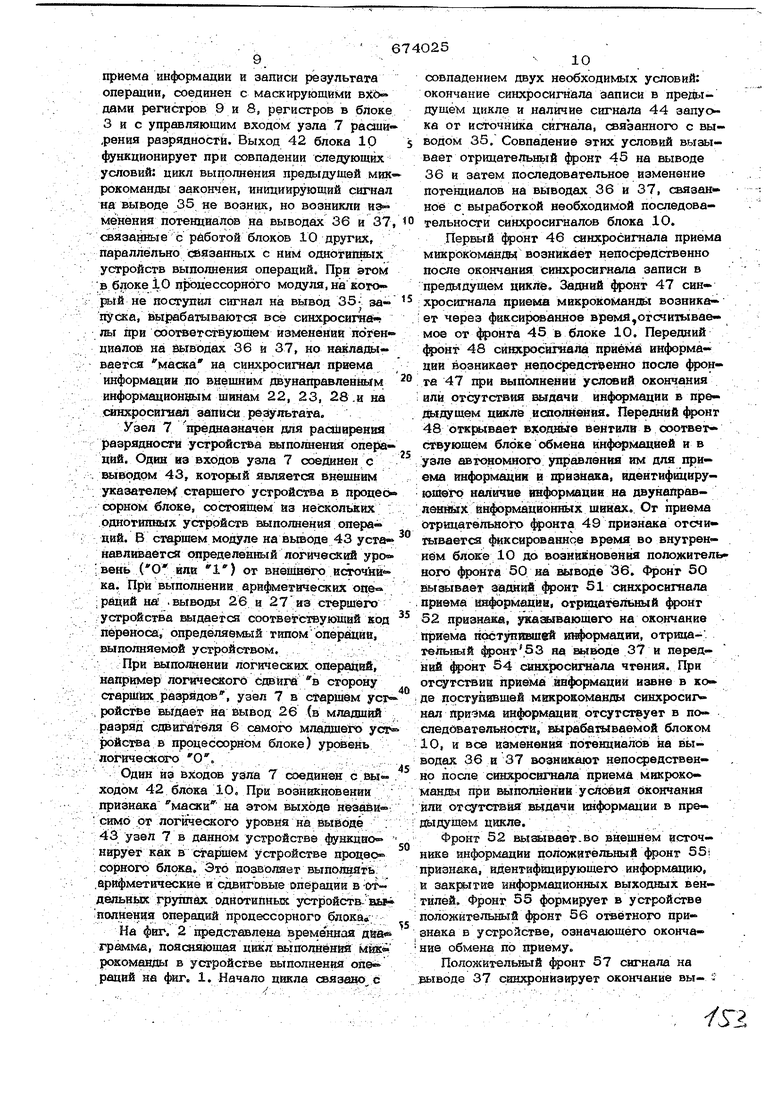

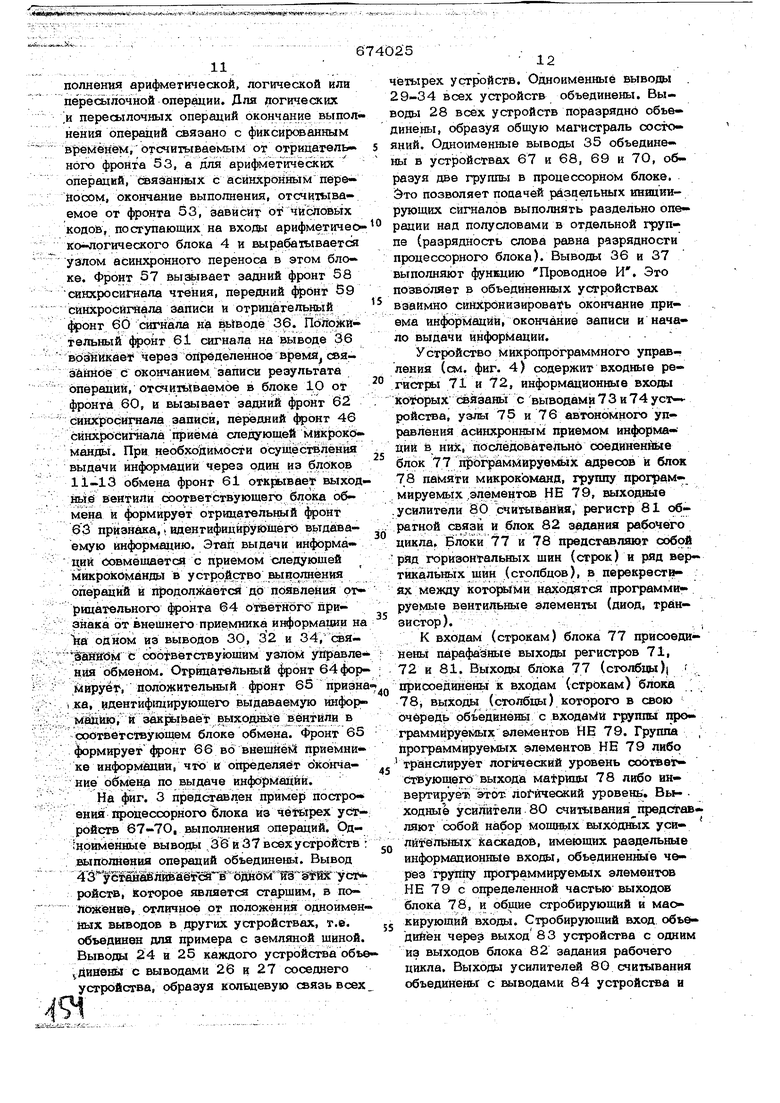

- . 5. .,ite.-.r-.i.,. низиругощих прием или выдачу информации через данный узел обмена. Выходы узлов 14-16 автономного управления обменом подключены к двум управляющим входам соогвегствующего блока 11-13 обмена и огкрьтваюг входные или выходные вентили на время приема или выдачи информации, г.е, оеансза связи по соотвегствую- щим Д1вунаправленным информационным ши- нам 22, 23 и 28. Бпок 10 формирования рабочего цикла подключен к трем внешним выводам 3537 устройства. Вывод 35 аапу.оса обязан .с источником сигнала, интиирующим новую последовательносгь синхросигналов. Выgo j 36 и 37 взаимно синхронизируют . пбтактнре ишолнение микрокоманда в нескольких параллельно соедикенных одно-. типных устройствах выйошенйя операций. 37 синхронизирует также выборку микрокоманды из однотипных устройств микропрограммного управления. Последовагельнос ь синхросигналов, вьхрабатываемая блоком 10, состоит из синхросиг нала приезд микрокоманды в регистр 1 микрокомайд, синхросигнала пр..ёма инфЬрмации йзвЦё через один из блбков 11-13 . обмена по шине 19, синхросигнала чтения операндов по шинам 17 а 18 в блок 4 в №шолнёния операции в нем, сйнхросага ла записи результата операции и контропйpyeMbix сЬстояйвй в приемники информа ции по 20 и 19. При признака приема информадик в коде микрокоманда и посЯедовательностй синхросигаалов о сугсгвует синхросигнал приема информации. Выход блока 10, свйзанный с синхросигналом приема микрокоман ; ды (выход 38),/соединен с входом .санхроНйзации регистра 1 микрокоманд. Вы- ход блока 10, связанный с синхросигнаяом чтения (выход 39), подключен к иё4 точйшшм операндов «регистру 9 резуль тата, регистру 8 состояний, блоку 3 регис ров общего назначения, регистру 1 : МШфокоМййД, к входусинхронизации при- . ема в рвгнотр 5 и к узлу 7 расширения разрядаости. Выходы блока 10, связаннь1е с синхросигналом приема информации (выход 40) по внешним магистралям и с син хросигнйфм эаписи результата операции (выход 41), соединены с входами сннхрои. низаний по приему информации регистра 9, регистра 8, р егистров в блоке 3, а также с узлом 7 расширения разрядности и узлами 14-16 автономного, управления обме- ном. Выход блока 10, связанный с признаком маски (вь1ход 42 / синхросигналов . приема анформадви и записи результата операции, соединен с маскирующиш вхЪ« дами регистров 9 и 8, регистров в блоке 3 и с управляющим входом узла 7 расши ,рения раэрядноспа. Выход 42 блока 10 функционирует при совпадении следующих условий: цикл выполнения предыдущей мик рокоманды закончен, инициирующий сигнал на выводе 35 не возник, но возникли из мёнения потенциалов на выводах 36 и 37 связанные с работой блоков ГО других, параллельно сйязанных с ним однотипных устройств выполнения операций. При этом в блоке 10 процессорного модуля,на когоРЗ{Й не поступил сигнал на вывод 35- запуска, 1аырабать1ваются все синхросига лы 11ри ооответствуюпюм изменений потенциале® на выводах 36 и 37, но накладывается маска на синхросигнал приема информации по внещним двунаправлев алм информационным шинам 22, 23, 28 .и на синхросигнал записи результата. Узел 7 предназначен для расширения разрядности устройства выполнения операций. Один из входов узла 7 соединен с , ияводрм 43, кото{х 1й является внешним указателе к старшего ус гройсдаа в процео сорном блоке, состоянием аз нескольких однотипных устройств выполнения операций. 0 старшем модуле на выводе 43 уста навливается определенный логический уро : вень (О или I) от вневшего иcтoчkй на. При выполнении арифметических оп :раций на .выводы 26 и 27 из crepmiero устройства ш 1дается соответствующий код переноса, определяемый типом операции, выполняемой устройством. При исполнении логичесасих операций, напр№лер логичесжогб сдаИга в сторону старших разрядов, узел 7 в старшем уст , ройстве выдает на вывод 26 (в младаиий разряд сдвигйтеля 6 самого младшего уст ройс1®а в процессорном блоке) урсеейь логического О. Один из Входов уэла 7 (хюдинен с выходом 42 блока 10, При возникновении признака маски на этом выходе Н1эаави« симо от логического уровня на выйод : 43 узел 7 в данном устройстве функционирует как в старшем устройстве процео« :сорного блока. Это позволяет выполнили ,арШ 1метические и сдвиговые операции в -о дельных группах однотипных устройств- щл полненяя операций процессорного блока На фиг, 2 цредст лена временная да, грамма, поясняющая ци&явьшоднёнйё MHs: рокоманды в устройстве выполнений опе« раций на 4шг. 1. Начало цикла связано с

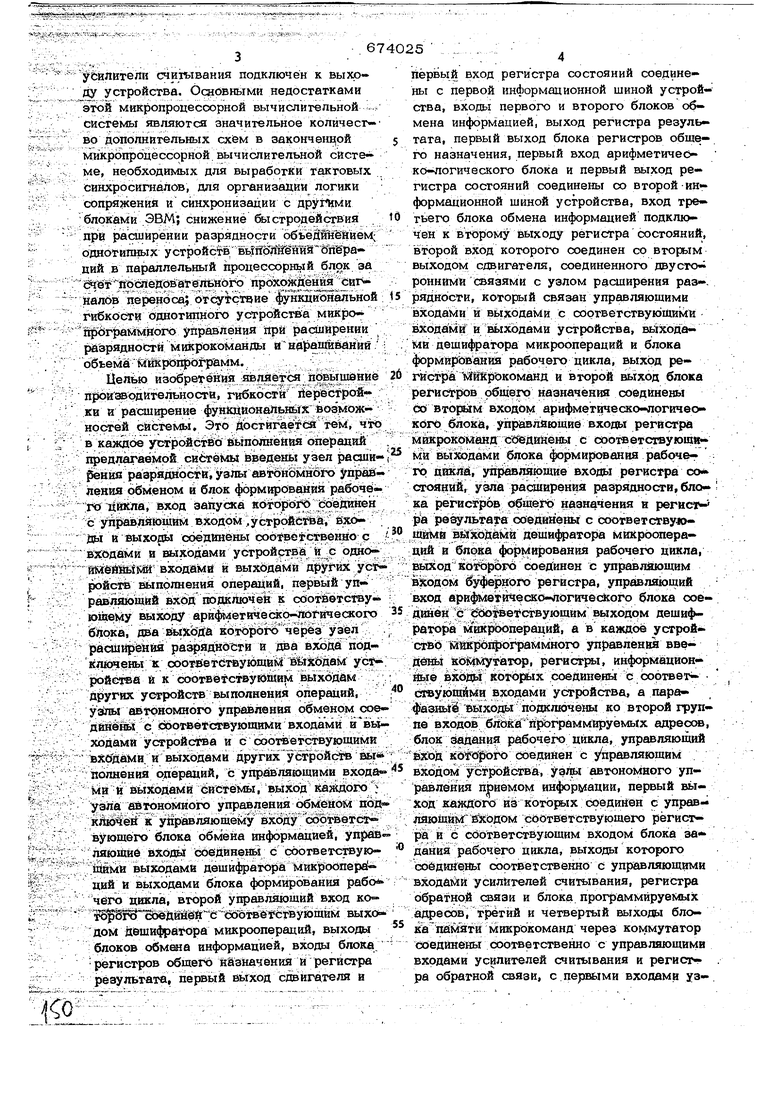

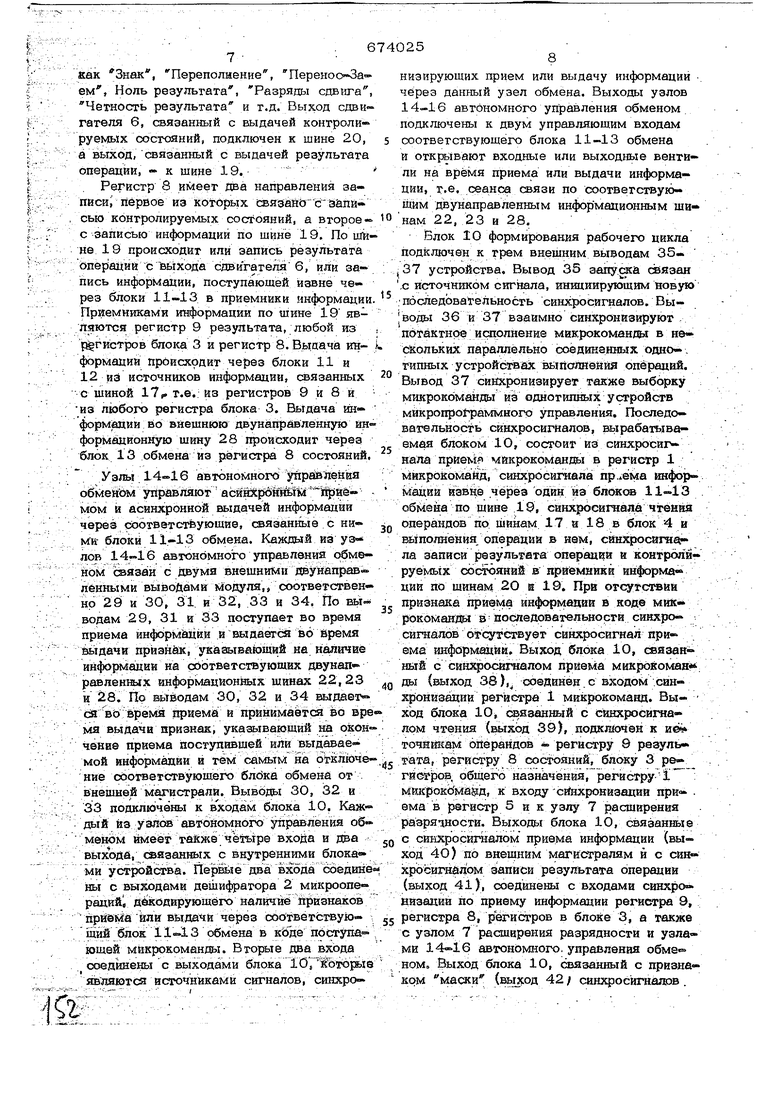

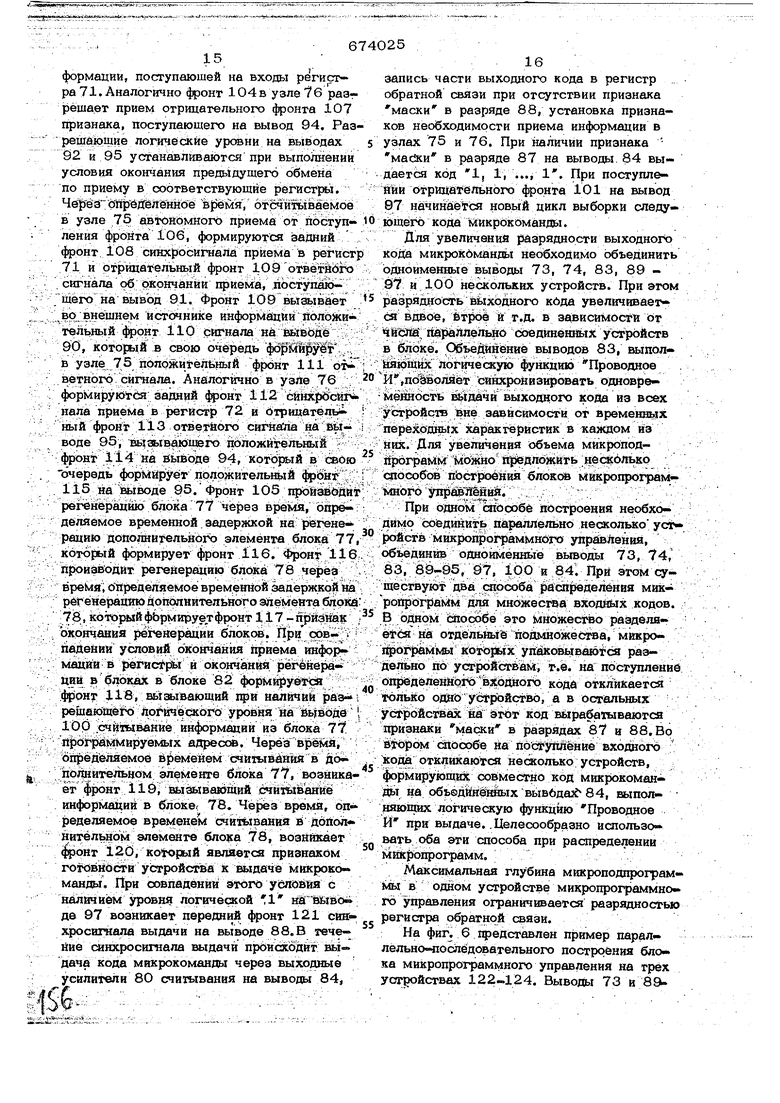

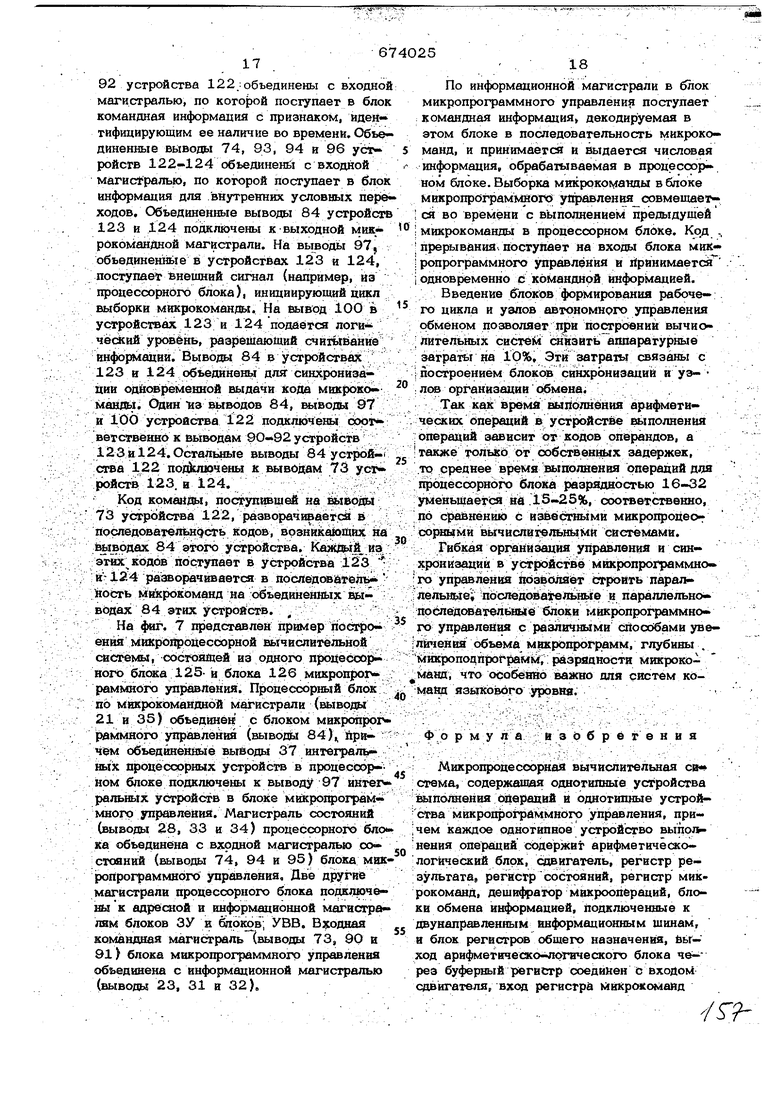

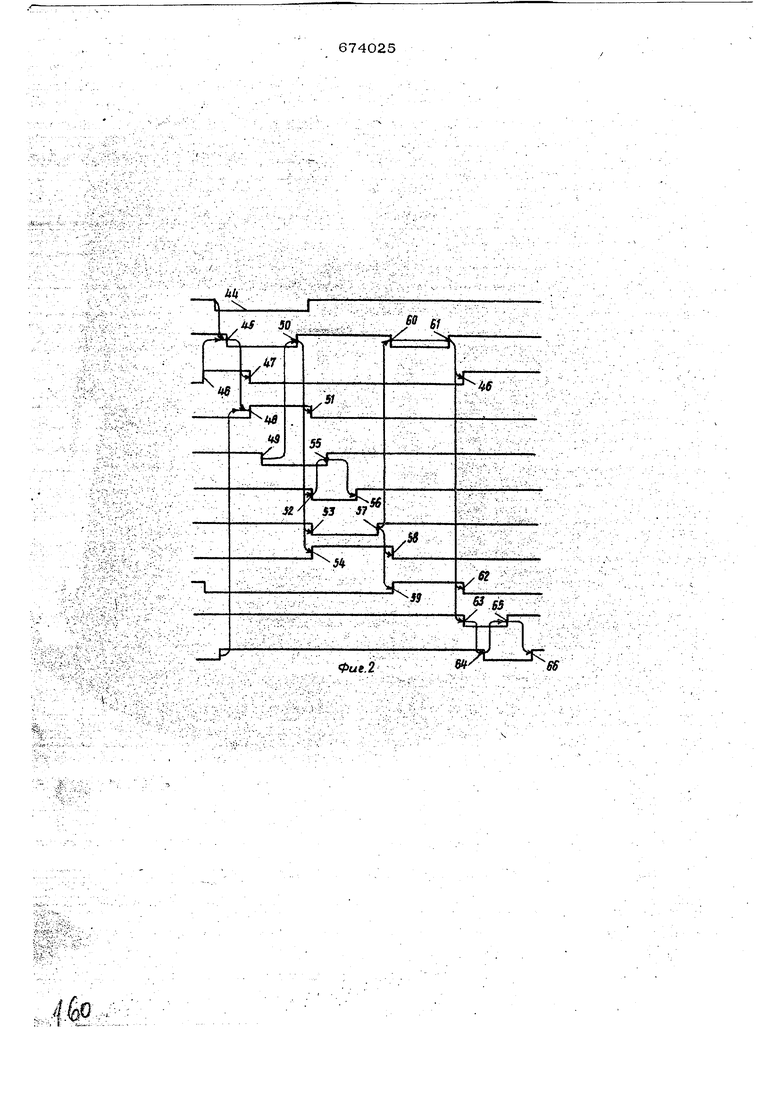

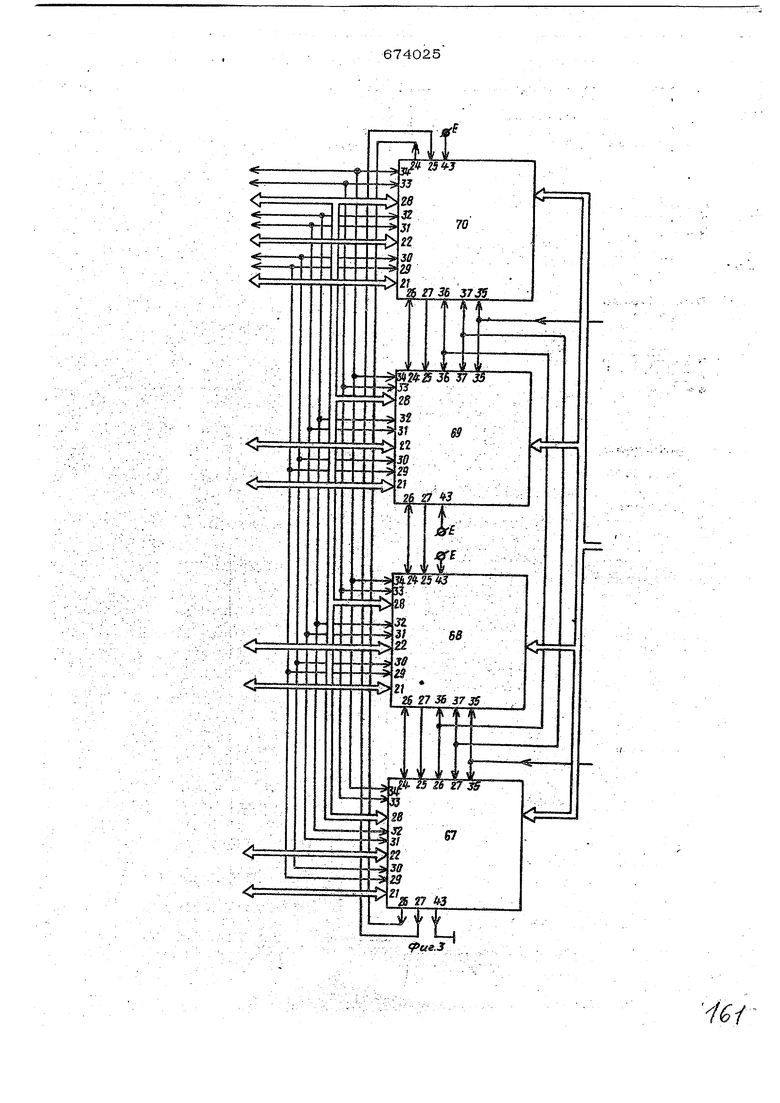

/Г совпадением двух необходимых условий: окончание синхросигнала записи в предыдущем цикле и наличие сигнала 44 запуока от источника сигнала, связанного с выводом 35. Совпадение этих условий выаз1вает отрицатвдьнь1й 4Тоиг на выводе 36 и затем последовательное изменение потенциалов на выводах 36 и 37, связанное с выработкой необходимой последовательносги синхросигналов блока 10. Первый 4ронт 46 синхросигнала приема микрокоманда возникает непосредственно после окончания синхросигнала записи в предыдущем цикле, 3(здний 47 синхросигнала приема микрокомандь возникает через фиксир аннов время,отсчитываемое от «feJOHTa 45 в блоке 10, Передний 48 сикхросигнала приёмй информации возникает непосредстеенно после фронта 47 при выполнении услсжий окончания или отсутствия выдачи инфсфмации в предыдуще1М цикле иоарЫения, Передаий 48 открывает входшлв Вентиле в соответствующем блоке обмена информацией ив узле авго1юмного управления им для приема информации и 1физыака, идентифицируюшегр наличие информации на даунаправденййх информационных шинах. От приема отрицателиаого 49 признака отсчи1ывается фиксированное время во внутреннем блоке 10 до возникновения положитель ного фронта 50 на выводе 36, Фрсдат 50 вышваеу задний ( 51 синхросишала приема информации, отрицательный 52 признака, заказывающего на окончание приема прступйипей нвформадии, отрицательный фрс«т,53 на выводе 37 и перед1Н ий ронт 54 санхросигаала чтения. При ОТСУТСТВИЕ приема информации извне в коде постудившей микрокоманды синхросигнал приема информшдии отсутствует в посяедсжателыюсти, Еаарабаплваемой блоком 10, и все изменения потенциалов на Выводах 36 и 37 возникают непосредственно после синхросигнала приема микрокоманды при выполнений условия бкончания ИЛИ отсутствия выдачи информации в пре- дыдуЩем цикле, . . ... Фронг 52 вы 1вавт.во внешнем источнике йн юрмации положительный 55; признака, идентифицирующего информацию, и закрытие информационных выходных вентилей. Фронт 55 формирует в устройстве положительный 56 ответного признака в устройстве, означающего окончание обмена по приему. Положительный 57 сигнала на выводе 37 синхронизирует окончание вы- s полнения арифметкчесжой, логической ила пересьшочной операции. Для «гюгичесхих и пересылочных операций окончание выполнения операций связано с фиксированным В1ременбм, Ьтсчитьгваемым от отрицагвль« ного фронта 53, а для арифметических операций, Связанных с асйнхройньШ переносом, окончание выполнения, отсчитываемое от фронта 53, зависит от числовых код ову поступающих на входы арифметичео ко-лргического блока 4 и вырабатывается узлом асишфонного переноса в этом блоке. Фронт 57 выщзшает задний фронт 58 синхросигнала чтения, передний (онт 59 сйнхросйзпйала записи и отрицйтельшй фронт 60 сйгн1ала на выводе 36. Штгозкйтельный4ф онт 61 сигнала на выводе $6 BoiShMkae через определенное время сйяэанноес окончанием записи результата операций, отсяитьтаемое в блоке 10 от фронта 60, и вызывает задний фронт 62 сишсросигнала записи, передний 4тонг 46 сйнх:)росйгнала приёма следующей Мйк)ОК(3манды. При н еобхоДиМости осугцестэлёнйя выдачи информации через один из блоков 11-13 обмена фронт 61 открывает выход Нь1б вентили соответствующего блока обмера и формирует отрицательный фронт 63 признака, i идентифицнруюйдего вьтдаваемую информацию. Этай выдачи информации совмещается с приемом следующей мнкрокО1у1анда в устройство выполнения операций и п родолжавтсй до появления отрицательного фронта 64 ответного признака от внешнего приемника информадаи на iia одном из выводов ЗО, 32 и 34, свя §а а1а«й с соб ветствующйм узлом унравленйя обменом. Отрицательный фронт 64форйируёт, положительный фронт 65 призна « . 1 ка, идентифицирующего выдаваемую ннформШик, и закр1ьшаёг выходайб в)энтйли в ррответстеующем блоке обмена. Фронт 65 Армирует«j oHT 66 во внёшйёй приемнике информ йдйи, что и определяет Окончание обмена по выдаче инфЬрмаййи. На фиг. 3 представлен пример постро ения гфоцессорного блока из чётътрех yci ройств 67-70, выполнения операций. Од;нрименные выводы .36 и 37 всех устройств выполнения операций объединены. Вывод 2 ШёШ тг с -Швш Жттуся ройств, iKOTopoe является старшим, в по- Ябжёниб, Отличное от положения одноименных выводов в тфугих устройствах, т.е. обьед,внен для примера с земляной шиной. Выводы 24 и 25 каждого устройства объе удинены с выводами 26 и 27 соседнего устройства, образуя кольцевую связь всех етырех устройств. Одноименные выводы 29-34 всех устройств объединены. Выоды 28 всех устройств поразрядно объеинены, образуя общую магистраль состоний. Одноименные выводы 35 объединены в устройств/ах 67 и 68, 69 и 70, образуя две группы в процессорном блоке. позволяет поцачей рйзцельных инициирующих сигналов выполнять раздельно oneрации над полусловами в отдельной г руппе (разрядность слова равна разрядности процессорного блока). Выводы 36 и 37 выполняют функцию Проводное И. Это позволяет в объединенных усггройствах взаимно синхронизировать окончание приема ин рмацйй, окончание записи и начало выдачи информации. Устройство микропрограммного управления (см. фиг. 4) содержит входные регистрь 71 и 72, информационш е входы кочрорых сазйэань с выводами 7 3 и 74 устройсгва, узлы 75 и 76 автономного управления асинхронным приемом информации в них, последовательно соединенйые блок 77 гфограмМируемЬ : адресов к блок 78 памяти микрокоманд, группу программируемьгх .элементов НЕ 79, выходные усилители 80 считывания, регистр 81 обратн:ой связи tf блок 82 задания рабочего цикла. Блоки 77 и 78 представлявдт собой ряд горизонтальных щин (строк) и ряд вертикальных шин (столбцов), в перекрестиях между которыми находятся программиpyeMbte вентильные элементы (диод, трак- зистор). К входам (строкам) блока 77 прйсоединёнь парафазные выхода регистров 71, 72 и 81. Выходы блока 77 (столбим) присоединены к входам (строкам) блока - - 4 . 78, выходы (столбцы) которого в свою очередь объединень с входа 1й группы программируемых элементов НЕ 79. Группа программируемых элементов НЕ 79 либо транслирует логический уровень соо дает- ствующегб выхода матрицы 78 либо инвертируетй ЭТОТ-ло йчесжий уровень . Вы-, ходные усилители 80 считывания предсгавляют собой набор мощных выходньтх уси- лйгбльных Каскадов, имеющих раздельные информационные входы, объединенные через группу программируемых элементов НЕ 79 с определенной частью выходсв блока 78, и общие стробирующкй и маскирующий входы. Стробирующий вход объедийён через выход 8 3 устройства с одним из выходов блока 82 задания рабочехю цикла. Выходы усилителей 80 считывания объединены с ныводами 84 устройства и

13 позволяют выполнять логическую функцию Проводное И, Вторая часть выходов бло ка 78 через группу элементов 79 обье динена с информационными входами регист ра 81 обрагной связи. Третья часть выходов блока 78 представляет собой четыре служебных разряда 85-88 кода мшсроко манды, два из которых (85 и 86)являются признаками, определяющими необходимость приема информации соответственно в регисгра 71 и 72 перед выборкой кода сле дующей микрокоманды, а следующие два разряда 87 и 88 являются признаками масжи. Выход разряда 87 обьеданен с маскирующим входом усилителей 80 счи- ШВания. .- . ; ;.- -.::-::-Регистр 81 обратной связи, кроме вхо да синхронизации по приему, обьединенно,го с одним из выходе блока 82, имеет вход, маскирующий прием информации . него. Этот вход соединен с выходом сяу- жебногЬ разряда 88. Каждый из узлов 75 и 76 автономно го управленид приемом информации в регистр объединен с четъхрьмя выводшйи со отфегсавенно 89-92 и 93-96 уафойства. Выводы 89 и 93 подключены к источникам внешних свгнаЛ ов,устанавливакш1их на выводах 73 «и 74 извне .признаки необходимости приёма информации в управляемые ими регистры. Выводы 90 и 94 подкгаоченн к источникам внешних сипкалрв, . идентифици{ к шшс наличие информации ва шдводах 73 и 74. Выводы 91 и 95 подключены, к внутренним источникам 0 узлах 75 и 76, формирующих огватвые с«а налы об окончании приема информаави. На выводах 92 и 96 устанавливаются узлами 75 и 76 потевдаальньте урсмзнй, раз-, решающее прием с{1гналс® по выводам 90 и 94. Выводы 9й и 96 при объединении с одноименными выводами других устройств .микропрограммного управления выйблняitor логическую функцию Проводаюе И и предназначены для одновременного приёма сигналов по выводам 90 и S4 и, а)6м1.ёт«ственно идентифицируемой ими инфор уиции Ё несколько параллельно обьединеншх устройств..: Каждый- из узлов 75 и 76 синхросигнал приема информацнн.который поступает на вход синхронизации по приему уп1ивляемого этим узлом регистра в на один ва входов блока 82. того, .вход узла 75 объединен с выходом служебного рафяда 86 кода микрокоманды являющимся признаком необходимости приема информации в регистр 71. Аналогич14

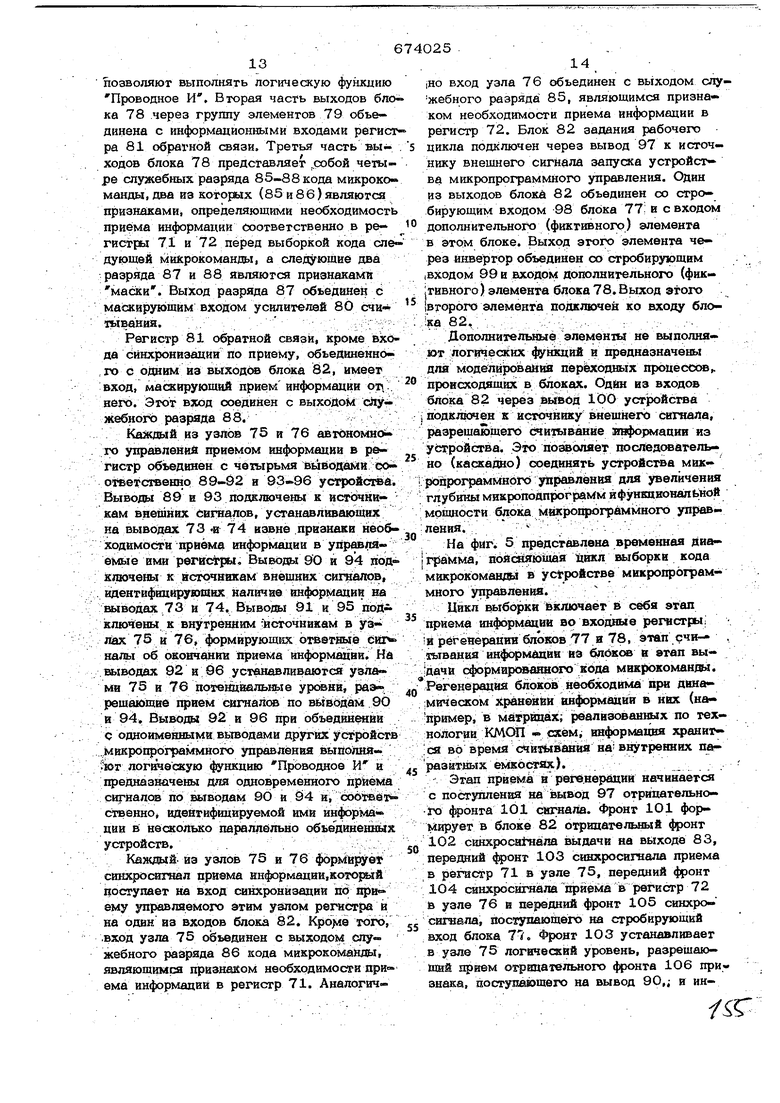

/5Г jHo вход узла 76 объединен с выходом служебного разряда 85, являющимся признаком необходимости приема информации в регистр 72. Блок 82 задания рабочего цикла подключен через вывод 97 к источнику внеишего сигнала запуска устройства микропрограммного управления. Один из выходов блока 82 объединен со сгробирующим входом 98 блока 77; в с входом дополнительного (фиктивного) элемента в этом блоке. Выход этого элемента через инвертор объединен со стробирующим (ВХОДОМ 99 и входом дополнительного (фикJTHBHOro) элемента блока 78. Выход этого второго элемента подключен ко входу 82,.,; -. х-;; ;,..- : /;Дополнительны элементы не выполняют логических функций и предназначены для моде71иров и:в nepiexoms ix процеСОж проасходящЕ1х в блоках. Од|1га из входов блока 8:2 через вывод 10О устройства подключен к йсточ)«ику Внешнего Сигнала, разрешающего сч ишвание хгнформааии из устройства. Это погеоляет послед(юательно (каскадно) соединять устройства мик |Х)программн 5гб управления для увеличения глубины MHKponoflnpoPtsaMM йфункднонаяЬной мрищости блока макропрогрйммного управления.;:. . : . - . На фаг 5 предсгевлена временная Диаг{5амма, п6йс:ййй1цая йижл выборк1а кода микрокомашяа в устройстве микропрограммного управления. Цикл №гборкн включает в себя этап приема информации во входные регистры; 1й рёгенерацнн блоков 77 и 78, этап счн- , йлванйя внффк«йднн ий в этап вы:Дачк сформированного Кбда микрокоманда. Регенерация блоков необходима при динамическом хранении информации в нвх (на пример, в: матрицах; реализованных по технологий КМОП « схем j ннформацня хранит; ся во время с ийЛ1в;ания на внутренних паразйтных емкостях). Этап приема и реге.нерации начинается с поступления на звывод 97 отрйцательнора фронта 101 Сигнала. Фронт 101 формирует в блоке 82 отрицательный фронт 102 сннхросн1т1ала выдачи на выходе 83, передний ЮЗ синхросигнала приема в регистр 71 в узле 75, передний фронт 1О4 синхросигнала приема в регистр 72 6 узле 76 и передний фронт 105 синхросигнала, поступаюгцего на стробирующий вход блока 77. Фронт 103 устанавливает в узле 75 логвческий уровень, разрешающий првем отрщательного 1О6 при знака, поступающего на вывод 90, и ин1 ,6740 15., формации, посгупаюшей на входы регистра71.Аналогично 4ронг 104вузле7б разг решает прием отрицательного фронта 107 признака, поступающего на вывод 94. Разрешающие логические уровни на выводах s 92 и 95 устанавливаются при выполнении условия окончания предь1дущег6 обмена по приему в соответствующие регистры. Через Определенное время, отсчитываемое в узле 75 автономного приема от поступ- ю ления фронта 106, формируются задний фронт 108 синхросигнала приема в регистр 71 и отрицательный фронт 109 ответййго сигнала об окончании приема, поступающего на вывод 91. Фронт 1О9 вызывает во внешнем источнике информации положительный 4чронт 110 сигнала на выводе 90, который в свою очередь фо мй уёт в узле 75 положительный фронт 111 ветного сигнала. Аналогично в узле 76 20 формируются задний 112 синхрбсигнала приема в регистр 72 и отрицатель ; ный 4ронт 113 ответного сигнала на вы- воде 95, вызывающего положительный фронт 114 на йыводе 94, который в свою очередь формирует положительный фронт 115 на выводе 95.Фронт 105 производит регенерацию блока 77 через время, опрвделяемое временной задержкой на регене- рацию дополнительного элемента блока 77,° который формирует фронт 116. 1тронт 116. производит регенерацию блока 78 через , вреМй, определяемое временной задержкой на регенерацию дополнительного элемента блока 78, котчэрмйфЬрмируетфронт 117-признак . окончания регенерации блоков. Присов- . падении условий окончания приема информацйи в регистры и oкoнчiaния рёгёнерации в блоках в блоке 82 формируется 118, выа 1вающий прк наличии раз-, решающего логического уровня на быводе, 100 .считывание информации из блока 77 программируемых адресе. Через BpeNM, определяемое временем счйпдвания в дополнительном элементе блока 77, возникаёт фронт 119, вызывающий считывание информации в блоке 78. Чё{зез время, 6пределяемое временем сяйтьшанигйг и дбпол нительноМ элементе 78, возникает „ ( 120, который является признаком го1чэвНОсти устройства к Еыдаче Микроко- манды. При совпадений этого уьлобйя с нйличиёМ уровня логической тЩ Шлво да 97 возникает передний фронт 121 сияхросигнала выдачи на выводе 88. В гече- Ние (жнхросигнала выдачи происходит ш. дача кода микрокоманды через выходные усилитеЛи 80 считывания на выводы 84, 4SS-i --.r-:r-V - wV.-. - 25 16 запись части выходного кода в регистр .. обратной связи при отсутствии признака маски в разряде 88, установка признаков необходимости приема информации в узлах 75 и 76. При наличии признака майки в разряде 87 на выводы. 84 выдается код 1, 1, ..., 1. При поступлеяии отрицательного фронта 101 на вывод 97 начинается новый цикл выборки следу ющего кода микрокоманды, Для увеличения разрядности выходного кода микрокбманды необходимо объединить одноименные выводы 73, 74, 83, 89 97 и 100 нескольких устройств. При этом разрядность выходного кбда увеличивается вдвое, бтрое и т.д. в зависимости от чйсШ, параллельно соединенных устройств в блоке. Объединение выводов 83, выполйяюших логическую функцию Проводное . и ,пс Ьволяет синхронизировать одновремённость выдачи выходного кода из всех устройств вне зависимости от временньлХ переходнь х характеристик в каждом из них. Для увеличения объема микроподйрограмм мо жнопредложить несжолько способсв пЬстроения блоков микропрограммного упраШШия. При одном способе построения необхо димо соединить параллельно несколькоусТ« ройств микропрограммного управления, объединив одноименньш вывода 73,74, 83, 89-95, 97, 1ОО и 84. При этом сушествуют два способа распределения мик- pottpolpaMM для множества входных кодов. В одном способе это множество раэделн- на отдельные подмножества, мпкро1фограммы котоуых упаковываются раздельно по устройствам, т.е. на поступление определенйо1Ч)входного кодй откликается только одно устройство, а в остальных устройствах на этот код вырабатываются признаки маски в разрядах 87 и ё8.Во атором способе на поступление входного кода откликаются неосолько устройств, формирующих совместно код микрокоманда на объедйнешых выв6дaJ 84, выпол- някидих логическую функцию Проводное И при выдаче. .Целесообразно использо- вать оба эти способа при распределении мй:к{л Црограмм. Максимальная глубина микроподпрограммы в одном устройстве микропрограммного управления ограничивается разрядностью регистра обратной связи, На фиг. 6 гфеДставЛен пример параллельно-посЛёдовательного построения бложа микропрограммного управления на трех уся- йствах 122-124. Выводы 73 и 8992 устройства 122j объединены с входно магистралью, по которой поступает в блок командная информация с признаком, идей- тифвдирующим ее наличие во времени. Объединенные выводы 74, 93, 94 и 96 устройсгв 122-124 обьешнеш с входной магистралью, по которой поступает в блок информация для внутренних условных nepie ходов. Объединенные выводы 84 устройст 123 и 124 подключены к выходной мик-« рОкоманДной магистрали. На выводь 97, обьединенньте и устройствах 123 и 124, поступает внешний сигнал (например:, из процессорного блока), инициирующий цикл выборки микрокоманды. На ЁЫВОД 100 в устройстпэах 123 и 124 подается логический урсёбнь, разрешающий счййгйаниа информации. Выводы 84 в устройствах 123 и 124 объединены для синхронизации одновременной выдачи кода микрокоманды. Один ъз выводов 84, выводы 97 и 10О устройства 122 подключены соот- ветсярвенно к выводам 9О-92 устройств 12 3 и 124. Осталыаге выводы 84 у строй-i ства 122 погб лючеаы к выводам 73 устройств 123. в 124. Код команш 1, поступюшей на выводы 73 устройства 122, разворачивается в последовательн9С7ь кодов, возникаюших на выводах 84 этого устройства. Каждый, из эгих кодов поступает в устройства и-124 разворачивается в последсюатель1йость ми1крокоманд на объединенных выводах 84 этих устройств. На фиг. 7 представлен пример построения микропроцессорной вычислительной системы, состоящей из одного процессорного блока 125- и блока 126 мнкропрограммного управления. Процессорный блок по микрокомаидной магистрали (шводм 21 if 35) объщиява с блоком мвкропррг рамкщого управления (вывод)и 84),,йрй-: Ч0М объединенные вьтоды 37 HHTerpanbii ных процессорных устройств в процесеор- ном блоке подключень к выводу 97 ингег ральных устройств в блоке мйкрощюграммногозгправления. Магистраль состояний (выводы 28, 33 и 34) процессорного бло ка объединена с входной магистралыо состоиний (выводы 74, 94 и 95) блока мик ропрограммного уцравле1аия. Две другие магистрали процессорного блока подалюче- шдк адресной и информационной магистралям блоков ЗУ и &IOKOB; УВВ. В; ОДЕШЯ командная магистраль (выводы 73, 90 и 91) блока микропрограммного управления объединена с информационной магистралью (выводы 23, 31 и 32).

информационной магистрали в блок микропрограммного управления поступает командная информация, декодир уемая в этом блоке в последовательность микрокоманд, и принимается и выдается числсжая информация, обрабатываемая в процессорном блоке. Выборка микрокоманды в блоке микропрограммйого уйравления совмещаетi ся во времени с выполнением предыдущей I микрокоманды в процессорном блоке. Ко,д ., ; пре{я 1вания поступает на входы блока мик- ропрограммного управления и йринимается i одновременно с командной информацией. Введение блоков формирования рабочего цикла и узлов автономного управления обменом позволяет при построении вычио; лительных систем шизйть аппаратурные затраты на 10%, Эти затраты связаны с построением блоков синхронизации и уз- лаа организации обмена. Так как времй шдполнения арифметических операций в устройстве выполнения операций зависит от кодов операндов, а также только от собственных задержек, то среднее время выполнения операций для процессорного блока разрядностью 16-32 уменьшается на 15-25%, соответственно, по сравнению с из&естными микропроцес-: сО{шыми вычислитчальными системами. Гибкая организация управления и синхронизации в уст юйст-ве микропрограммного управления позволяет строить параллельные; последовательные и параллельно последсяательные блоки микропрограммного управления с различными способами увели 1ения объема микропрограмм, глубины . микропоапрограмм, разрядности микрокоМанд, что осо(5ённ6 важно для систем коМайдязьпсбвОго уровня. Ф О р м У Л а И 3 обретения Микропроцессорная вычислительная ев- стема, содержащая однотипные устройства Ёыпошения (Л1ераций и однотипные устройства микропрограммного управления, причем каждое однотипное устройство выполз нения операций содержит арифметиче жологический блок, сдвигатель, регистр результата, регистрсостояний, регистр микрокоманд, микроопераций, блоки обмена информацией, подключенные к Двунаправленным информационным шинам, и блок регистрсв общего назначения, йыход арифметичеасо огического блока че- рез буферный регистр соединен с входом сдвигателя, вход регистра микрокоманд подключен к управляющей шине, а выходк входу деши4|)агрра микроопераций/каждое однотипное устройство микропрограм много упрйвления содержит последовательно соединенные бдок программируемых адресов и блок памяти микрокоманд, группы программируемых элементов НЕ, регистр обратной связи, парафазные выходы которого подключены к первой группе входов блока программируемых адресов, а информационный вход через первую группу пр6граК(1Мируемых элементов НЕ соединен с первым выходом блока памяти микрокоманд, второй выхо1Д кЬторого через последЬёательнй соединённые вторую группу прЪгрвммируемьгх элементов НЕ и усйли1«Лй счить11вания подключен к выходу устройатва, ь f л и ч а к щ & я с я тем. а ю щ & я с я что, с йелью.-повышйгйй проиШедй ёль.нооtK, гибкости перестройки и расширения функциональных возможностей, feKajkfloe устройство 1аыполнё11ия операций системы ввёденьг узел расширения рйзрядности, УЗ- ль1 автономного управ1лени:я обменом и блок формирования рабочего цикла, вход -запуски которого соединен с управляющим входом устройства, входы и выходы соединены соответственно с входами и выходами устройства и с одноименнь1ми входами и выходами других устройств выполиекия операций, пернвый управляющий вход подключен к йоотвеЧтствующему выходу арифметическо-логического блока, два выхода через узел расширения разрядности и два входа подключены к соответствующим ходам устройства и к соответствующим выходам других устройств выполнения операций, узлы автономного уnpasneHtia обменом соединены с со6тЕ етг ствуюшими; входами и вь1ход°ами устройства и Ьбоогвётст вуЮшйми входами и выходамв ДругЁрс. устройргв выполнений бпе ацйй, с управляющими входами и ш одамй системы, выход каждого узла автоном нЬгб управления обменом подключен к управлясЬщётму eboTBercifBjTOniero бло ka обмена информацией, управляющие да соединены с соответствующими выходамн ДёШ11|)ратор а микроопераций в выход и блока фор{«1И:р жания рабочего Цикла, второй управпяк)щий вйсод которого Ьоеданей с сЬотвёгствующйМ выходом дёшифраtojpa М11к|)оо перацнй, выходы блОков обме-ь на йнфЬрм1ещвёй, входы блока регистров общего нйзначеяня ia регистра результата, дер&ый вь1хОд сдвигателя и первый вход регистра состояний соединешзт с первой информационной шиной устройства, входы

ш первого и второго блоков обмена информацией, выход регистра результата, первый выход блока регистров обшего назначения, первый вход арифметическо-логического блока и первый выход perHctpa состояний соединены со второй информадионной шиной устройства, вход третьего блока обмена информацией подключен к второму выходу регистра состояний, второй вход которого соединен со вторым выходом сдвигателя, соединенного двусторо1нними связями с УЗЛОМ расширения разрядности, который связан управляющими входами и выходами с соответствующими входами и выходами устройства, выходами дешифратора микроопераций и блока формирования рабочего цикла, выход регистра микрокоманд и второй выход блока регистров общего на:значения соединены со вторым вхоДом арифметическо-лоПйчесхого блока, управляющие входы , регистра микрокоманд соедйненьг с соответствующими ы 1ходами блока формирования рабочего цикла, управляющие входы регистра СОСТОЯНИЙ, узла расширения разрядности, блока регистров общего назначения и регистра результата соединены с соответсгвующими млходами деши||фатора микроопераций и блока формирования рабочего цикла, вьгход которого соединен с управляющим входом буферного регистра, управляющий вход арифметическо-логического блока соединен с соответствующим выходом дешифратора микро- операций, а в каждое устройство мнкро- программного управления введены коммутатор, регистры, информационные входы которых соединены с соответсгвующими входами устройства, а парафазные Отходы подключены ко второй группе входов блока программируемых адресов, блок задания рабочего цикла, у правляющйй вход кОторого соединен с управляющим входом устройдсва, узлы автономного управления приемом информации, первый выход каждого из которых соединен с управляющим вхо-. ДОМ схзотвёт-етвующёго цегйбгра b с соответствующим входом блока задания рабочего Цикла, выходы которого соединены соответственнос управляющими входами усилителей считывания, регистра обратной связи и блока программируемых адресов, третий и четвертый выходы блока памяти Микрокоманд через коммутатор соединены соответственно с управляющими входами усилителей считывания и регистра обрйтной связи, с первыми входами узлов авто- HOMlJoro управления приемом информации, вторые и третьи входы и выходы каждого

21 из которых соединены соогвегсгвенйо с входами и выходами усгройства и с соогветствующнми входами и выходами других устройств микропрогрцммно1:х) упр ления, вторые вход и выход каждого узла ав- тономного управления приемом информации подключены к соответствующим шинам управления передачей информации, а третий вход - к управляющему входу системы, четвертыйвыход блока памяти микро674025

Ч

22

команд соединен с соответствующим входом блока задания рабочего цикла. Источники информации, принятые во внимание Йрй экспертизеi 1 .Электроника , пер. с англ., иэд. Мир, М« 18, 1974. 2. Патент США № 3878514, кл. 340-172.5, 08.04.75. 3. Электроника, пер. с англ., изд 0: Мир, № 12, 1973, с. 44-54.

АЛ

J

US 30

ц

47

4:1

«

51

fT

MS

55

.n

jW «/

К

4s

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Устройство для обмена информацией | 1978 |

|

SU941978A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

S3 S7

J2

a/. 3

я

0ue.2

j

й

fi

-я

f 55

T i---:

«

Й

w

гьч-3

JJ гв

32 31 22 30

70

w

2L

П36 37 л

V irjijt

Й24:Ж J6 J7 J

S3

28

3f

3ffi

2

Jff

гг

J ;

ШТ5Ч

SB

27 JK 37

и u jL-sLst

« гй zrST

да

д

67

г/

3ff 23

Zt

г g7 43

V

V

4&i

674025

Щ

. -- la-- 1 .

1

97 100

O.

rn- 339SK 13839Ш9и

7

TPMmti

S

S5K9SS n TSgsaiStiS

FJ

11

pu3.fi

tL

TifS3ss36 73 am SB

Z и 1 У I

й

ff

-r

да

3/jf гз л J7

л пл л т

М

i у

AZ

А

J 3

99l09f 73

isn 84. 91 т

Авторы

Даты

1979-07-15—Публикация

1975-09-22—Подача