(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1988 |

|

SU1529228A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программ | 1988 |

|

SU1501102A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

Изобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодействия процессоров отлаживаемого устройства после окончания прогона отлаживаемых программ. Цель изобретения - расширение области применения за счет обеспечения возможности увеличения длины трассы межпроцессорных обменов. Устройство содержит два блока оперативной памяти, элемент НЕ, счетчик импульсов, мультиплексор. Дополнительно устройство содержит счетчик импульсов, мультиплексор, блок оперативной памяти, шифратор. Благодаря этим элементам и связям между ними создается положительный эффект, позволяющий за счет использования режима выборочной трассировки увеличить длину трассы межпроцессорных обменов. 2 ил.

Изобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодействия процессоров отлаживающего устройства после окончания прогона отлаживаемых программ.

Цель изобретения .- расширение области применения за счет обеспечения возможности увеличения длины трассы межпроцессорных обменов.

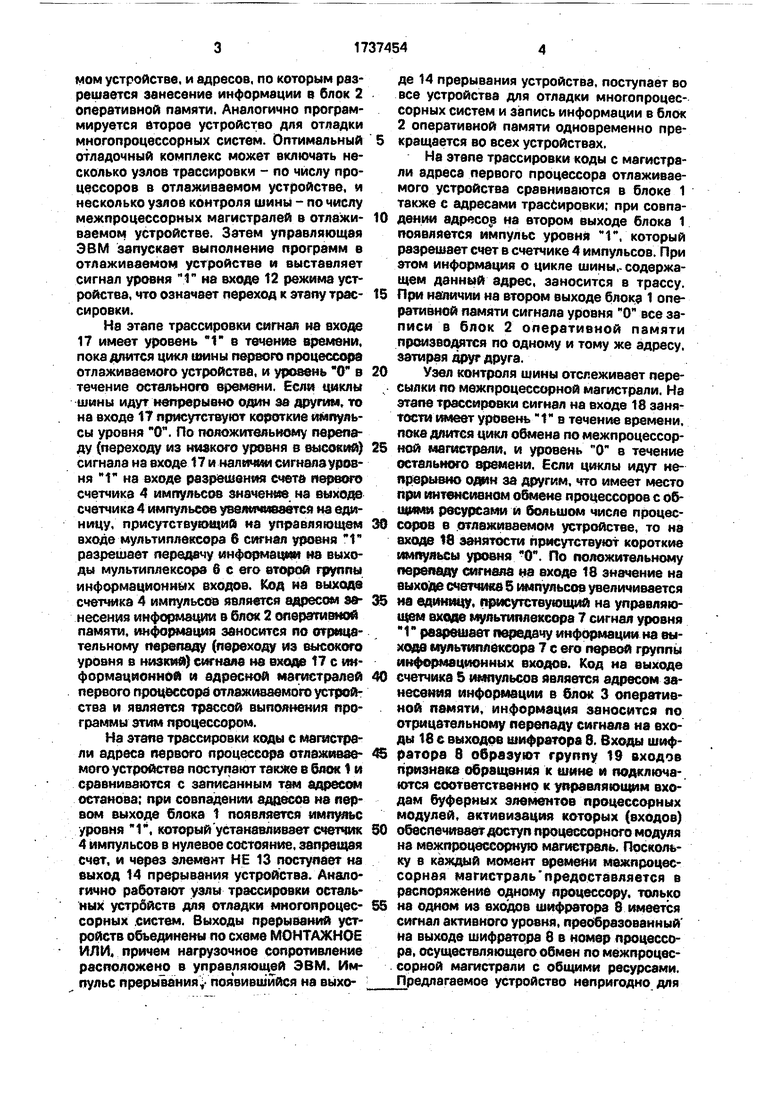

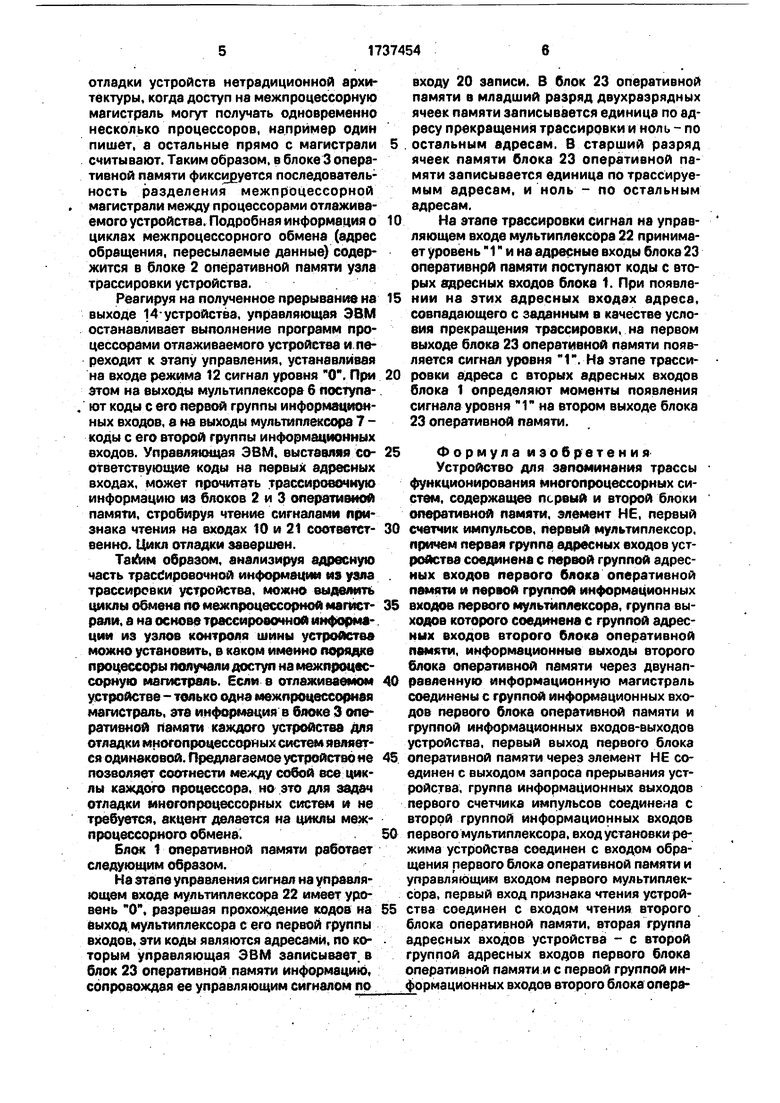

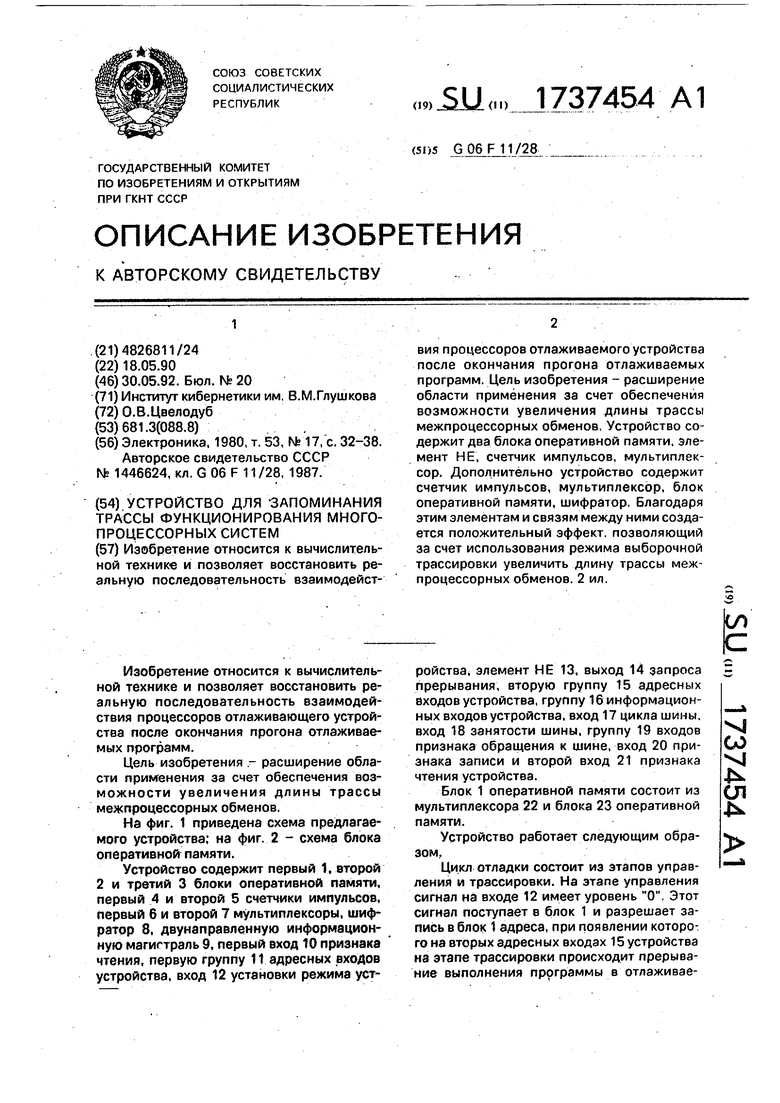

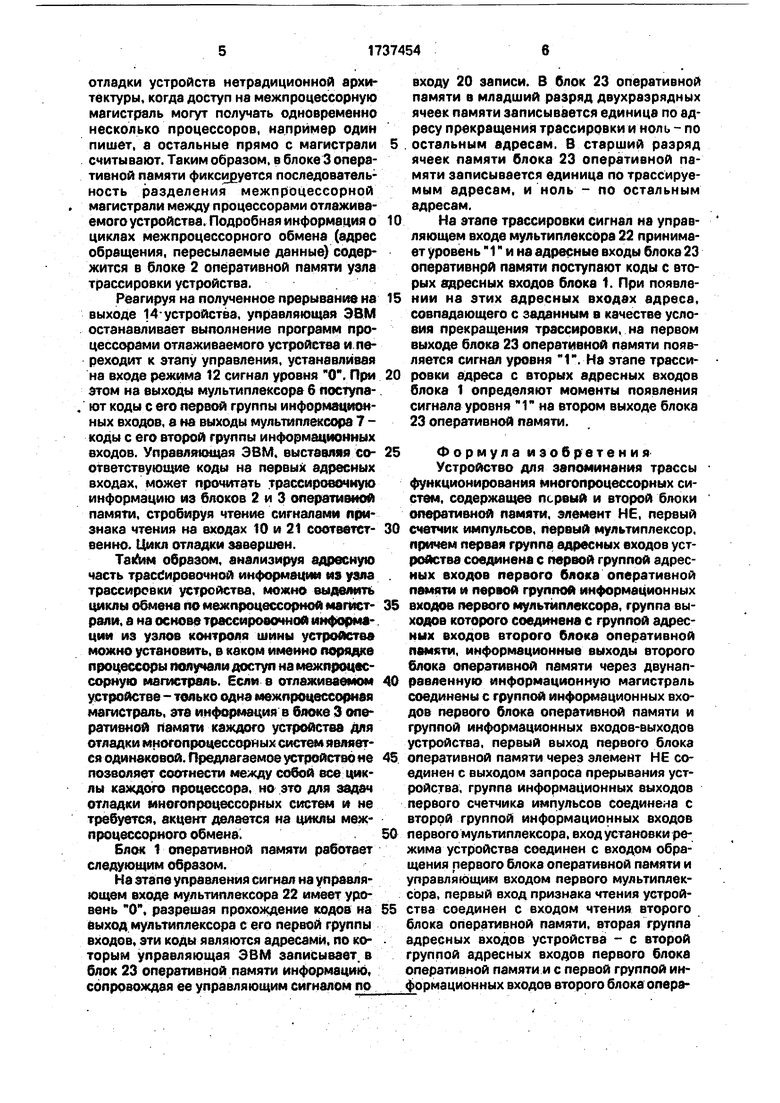

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока оперативной памяти.

Устройство содержит первый 1, второй 2 и третий 3 блоки оперативной памяти, первый 4 и второй 5 счетчики импульсов, первый 6 и второй 7 мультиплексоры, шифратор 8, двунаправленную информационную магистраль 9, первый вход 10 признака чтения, первую группу 11 адресных входов устройства, вход 12 установки режима устройства, элемент НЕ 13, выход 14 запроса прерывания, вторую группу 15 адресных входов устройства, группу 16 информационных входов устройства, вход 17 цикла шины, вход 18 занятости шины, группу 19 входов признака обращения к шине, вход 20 признака записи и второй вход 21 признака чтения устройства.

Блок 1 оперативной памяти состоит из мультиплексора 22 и блока 23 оперативной памяти.

Устройство работает следующим образом.

Цикл отладки состоит из этапов управления и трассировки. На этапе управления сигнал на входе 12 имеет уровень О. Этот сигнал поступает в блок 1 и разрешает запись в блок 1 адреса, при появлении которого на вторых адресных входах 15 устройства на этапе трассировки происходит прерывание выполнения программы в отлаживавvj

со

-Ч СП

мом устройстве, и адресов, по которым разрешается занесение информации в блок 2 оперативной памяти. Аналогично программируется второе устройство для отладки многопроцессорных систем. Оптимальный отладочный комплекс может включать несколько узлов трассировки - по числу процессоров в отлаживаемом устройстве, и несколько узлов контроля шины - по числу межпроцессорных магистралей в отлаживаемом устройстве. Затем управляющая ЭВМ запускает выполнение программ в отлаживаемом устройстве и выставляет сигнал уровня Г на входе 12 режима устройства, что означает переход к этапу трассировки.

На этапе трассировки сигнал на входе 17 имеет уровень 1 в течение времени, пока длится цикл шины первого процессора отлаживаемого устройства, и уровень О в течение остального времени. Если циклы шины идут непрерывно один за другим, то на входе 17 присутствуют короткие импульсы уровня О11. По положительному перепаду (переходу из низкого уровня в высокий) сигнала на входе 17 и наличии сигнала уровня Г на входе разрешения счета первого счетчика 4 импульсов значение на выходе счетчика 4 импульсов увеличивается на единицу, присутствующий на управляющем входе мультиплексора в сигнал уровня 1 разрешает передачу информации на выходы мультиплексора 6 с его второй группы информационных входов. Код на выходе счетчика 4 импульсов является адресом занесения информации а блок 2 оперативной памяти, информация заносится по отрицательному перепаду (переходу из высокого уровня в низкий) сигнала на входе 17 с информационной и адресной магистралей первого процессора отлаживаемого устройства и является трассой выполнения программы этим процессором.

На этапе трассировки коды с магистрали адреса первого процессора отлаживаемого устройства поступают также в блок 1 и сравниваются с записанным там адресом останова; при совпадении адресов на первом выходе блока 1 появляется импульс уровня 1, который устанавливает счетчик 4 импульсов в нулевое состояние, запрещая счет, и через элемент НЕ 13 поступает на выход 14 прерывания устройства. Аналогично работают узлы трассировки остальных устрбйств для отладки многопроцессорных .систем. Выходы прерываний устройств объединены по схеме МОНТАЖНОЕ ИЛИ, причем нагрузочное сопротивление расположено в управляющей ЭВМ. Импульс прерыванияt появившийся на выходе 14 прерывания устройства, поступает во все устройства для отладки многопроцессорных систем и запись информации в блок 2 оперативной памяти одновременно прекращается во всех устройствах.

На этапе трассировки коды с магистрали адреса первого процессора отлаживаемого устройства сравниваются в блоке 1 также с адресами трассировки; при совпа0 дении адресов на втором выходе блока 1 появляется импульс уровня 1. который разрешает счет в счетчике 4 импульсов. При этом информация о цикле шины,- содержащем данный адрес, заносится в трассу.

5 При наличии на втором выходе блока 1 оперативной памяти сигнала уровня О все записи в блок 2 оперативной памяти производятся по одному и тому же адресу, затирая друг друга.

0 Узел контроля шины отслеживает пересылки по межпроцессорной магистрали. На этапе трассировки сигнал на входе 18 занятости имеет уровень Те течение времени, пока длится цикл обмена по межпроцессор5 ной магистрали, и уровень О в течение остального времени. Если циклы идут непрерывно одмн за другим, что имеет место при интенсивном обмене процессоров с общими ресурсами и большом числе процес0 соров в отлаживаемом устройстве, то на входе 18 занятости присутствуют короткие импульсы уровня О. По положительному перепаду сигнала на входе 18 значение на выходе счетчика 5 импульсов увеличивается

5 на единицу, присутствующий на управляющем входе мультиплексора 7 сигнал уровня 1 разрешает передачу информации на выходе мультиплексора 7 с его первой группы информационных входов. Код на выходе

0 счетчика 5 импульсов является адресом занесения информации в блок 3 оперативной памяти, информация заносится по отрицательному перепаду сигнала на входы 18 с выходов шифратора 8. входы шиф5 ратора в образуют группу 19 входов признака обращения к шине и подключаются соответственно к управляющим входам буферных элементов процессорных модулей, активизация которых (входов)

0 обеспечивает доступ процессорного модуля на межпроцессорную магистраль. Поскольку в каждый момент времени межпроцессорная магистраль предоставляется в распоряжение одному процессору, только

5 на одном из входов шифратора 8 имеется сигнал активного уровня, преобразованный на выходе шифратора 8 в номер процессора, осуществляющего обмен по межпроцессорной магистрали с общими ресурсами. Предлагаемое устройство непригодно для

отладки устройств нетрадиционной архитектуры, когда доступ на межпроцессорную магистраль могут получать одновременно несколько процессоров, например один пишет, а остальные прямо с магистрали считывают. Таким образом, в блоке 3 оперативной памяти фиксируется последовательность разделения межпроцессорной магистрали между процессорами отлаживаемого устройства. Подробная информация о циклах межпроцессорного обмена (адрес обращения, пересылаемые данные) содержится в блоке 2 оперативной памяти узла трассировки устройства.

Реагируя на полученное прерывание на выходе 14-устройства, управляющая ЭВМ останавливает выполнение программ процессорами отлаживаемого устройства и переходит к этапу управления, устанавливая на входе режима 12 сигнал уровня О. При этом на выходы мультиплексора 6 поступа- ют коды с его первой группы информационных входов, а на выходы мультиплексора 7 - коды с его второй группы информационных входов. Управляющая ЭВМ, выставляя соответствующие коды на первых адресных входах, может прочитать трассировочную информацию из блоков 2 и 3 оперативной памяти, стробируя чтение сигналами признака чтения на входах 10 и 21 соответственно. Цикл отладки завершен.

TaxViM образом, анализируя адресную часть трассировочной информации из узла трассировки устройства, можно выделить циклы обмена по межпроцессорной магистрали, а на основе трассировочной информации из узлов контроля шины устройства можно установить, в каком именно порядке процессоры получали доступ на межпроцессорную магистраль. Если в отлаживаемом устройстве - только одна межпроцессорная магистраль, эта информация в блоке 3 оперативной памяти каждого устройства для отладки многопроцессорных систем является одинаковой. Предлагаемое устройство не позволяет соотнести между совой все циклы каждого процессора, но это для задач отладки многопроцессорных систем и не требуется, акцент делается на циклы межпроцессорного обмена.

Блок 1 оперативной памяти работает следующим образом.

На этапе управления сигнал на управляющем входе мультиплексора 22 имеет уровень О, разрешая прохождение кодов на выход мультиплексора с его первой группы входов, эти коды являются адресами, по которым управляющая ЭВМ записывает, в блок 23 оперативной памяти информацию, сопровождая ее управляющим сигналом по

входу 20 записи. В блок 23 оперативной памяти в младший разряд двухразрядных ячеек памяти записывается единица по адресу прекращения трассировки и ноль - по

5 остальным адресам. В старший разряд ячеек памяти блока 23 оперативной памяти записывается единица по трассируемым адресам, и ноль - по остальным адресам.

10 На этапе трассировки сигнал на управляющем входе мультиплексора 22 принимает уровень 1 и на адресные входы блока 23 оперативнрй памяти поступают коды с вторых адресных входов блока 1. При появле15 нии на этих адресных входах адреса, совпадающего с заданным в качестве условия прекращения трассировки, на первом выходе блока 23 оперативной памяти появляется сигнал уровня 1. На этапе трасси0 ровки адреса с вторых адресных входов блока 1 определяют моменты появления сигнала уровня Г на втором выходе блока 23 оперативной памяти.

5 Формула изобретения

Устройство для запоминания трассы функционирования многопроцессорных систем, содержащее первый и второй блоки оперативной памяти, элемент НЕ, первый

0 счетчик импульсов, первый мультиплексор, причем первая группа адресных входов устройства соединена с первой группой адресных входов первого блока оперативной памяти и первой группой информационных

5 входов первого мультиплексора, группа выходов которого соединена с группой адресных входов второго блока оперативной памяти, информационные выходы второго блока оперативной памяти через двунап0 равденную информационную магистраль соединены с группой информационных входов первого блока оперативной памяти и группой информационных входов-выходов устройства, первый выход первого блока

5 оперативной памяти через элемент НЕ соединен с выходом запроса прерывания устройства, группа информационных выходов первого счетчика импульсов соединена с второй группой информационных входов

0 первого мультиплексора, вход установки режима устройства соединен с входом обращения первого блока оперативной памяти и управляющим входом первого мультиплексора, первый вход признака чтения устрой5 ства соединен с входом чтения второго блока оперативной памяти, вторая группа адресных входов устройства - с второй группой адресных входов первого блока оперативной памяти и с первой группой ин- формационных входов второго блока оперативной памяти, группа информационных входов устройства - с второй группой информационных входов второго блока оперативной памяти, вход признака записи устройства - с входом записи первого блока оперативной памяти, вход цикла шины устройства - с входом чтения первого блока оперативной памяти, отличающееся тем, что, с целью расширения области применения путем обеспечения увеличения длины трассы межпроцессорных обменов, в него введены второй счетчик импульсов, второй мультиплексор, третий блок оперативной памяти, шифратор, причем вход занятости шины устройства соединен с тактовым входом второго счетчика импульсов и входом записи третьего блока оперативной памяти, группа информационных выходов которого соединена с группой информационных входов-выходов устройства, вход начальной установки второго счетчика импульсов связан с входом начальной установки первого счетчика импульсов и выходом элемента НЕ, второй выход первого

.УУ

7Г

К отложийаетму ycmfoucmtt/ Фиг(

блока оперативной памяти связан с входом разрешения счета первого счетчика импульсов, вход цикла шины устройства - с тактовым входом первого счетчика импульсов и входом записи второго блока оперативной памяти, группа выходов второго счетчика импульсов - с первой группой информационных входов второго мультиплексора, группа выходов которого соединена с группой адресных входов третьего блока оперативной памяти, вторая группа информационных входов второго мультиплексора связана с первой.группой адресных входов устройства, управляющий вход второго мультиплексора соединен с входом установки режима устройства, вход чтения третьего блока оперативной памяти соединен с вторым входом признака чтения устройства, группа входов признака обращения к шине устройства подключена к группе входов шифратора, группа выходов которого подключена к группе Информационных входов третьего блока оперативной памяти.

7Г-,

| Электроника, 1980, т | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-30—Публикация

1990-05-18—Подача