Изобретение относится к технике электрической связи, а именно к устройствам тактовой синхронизации.

Известно устройство тактовой синхронизации, содержащее первый и второй регистры, триггер и элемент И-НЕ, информационный вход, входы тактовых импульсов приема и передачи и информационный вход.

Недостаток известного устройства тактовой синхронизации состоит в малой помехоустойчивости.

Технический результат, который может быть получен при осуществлении настоящего изобретения, выражается в повышении помехоустойчивости.

С целью получения этого технического результата в устройство тактовой синхронизации, содержащее первый и второй регистры, триггер, элемент И-НЕ, информационный вход, входы тактовых импульсов приема и передачи и информационный вход, введены последовательно соединенные третий и четвертый регистры и мультиплексор, последовательно соединенные пятый и шестой регистры, последовательно соединенные счетчик, интегратор, первый сумматор по модулю два, второй и третий счетчики, а также второй сумматор по модулю два и гасящий элемент, при этом выходы четырех разрядов первого регистра соединены с соответствующими информационными входами третьего регистра, выходы четырех разрядов второго регистра соединены с соответствующими информационными входами пятого регистра, выходы четырех разрядов шестого регистра соединены с соответствующими информационными входами мультиплексора, адресные входы которого соединены соответственно с выходами первого и второго разрядов и с выходом третьего разряда третьего счетчика, который соединен со входами синхронизации четвертого и шестого регистров, выход второго разряда первого счетчика соединен со вторым входом первого сумматора, а выход третьего разряда первого счетчика соединен со входами синхронизации третьего и пятого регистров, вход установки нуля третьего счетчика соединен со входом синхронизации второго счетчика, выход элемента И-НЕ соединен непосредственно и через гасящий элемент соответственно со входом синхронизации и с информационным входом триггера, выход которого через второй сумматор по модулю два соединен со входом разрешения третьего счетчика, а выход четвертого разряда первого регистра соединен с информационным входом второго регистра, причем информационный вход первого регистра является информационным входом устройства, входы синхронизации первого и второго регистров и первого счетчика и первый вход элемента И-НЕ соединены между собой и являются входом тактовых импульсов приема устройства, второй вход элемента И-НЕ, второй вход второго сумматора по модулю два и вход разрешения второго счетчика соединены между собой и являются входом тактовых импульсов передачи, вход синхронизации третьего счетчика, входы установки нуля и единицы триггера, входы установки нуля первого и второго регистров, входы выбора прямого и обратного кода и входы установки нуля третьего, четвертого, пятого и шестого регистров, вход установки нуля первого счетчика и вход запрета мультиплексора соединены между собой и являются общей шиной устройства, а входы последовательной записи и входы параллельного и последовательного режимов работы третьего, четвертого, пятого и шестого регистров и вход разрешения первого счетчика соединены между собой и являются входом логической единицы устройства, информационным входом которого является выход мультиплексора.

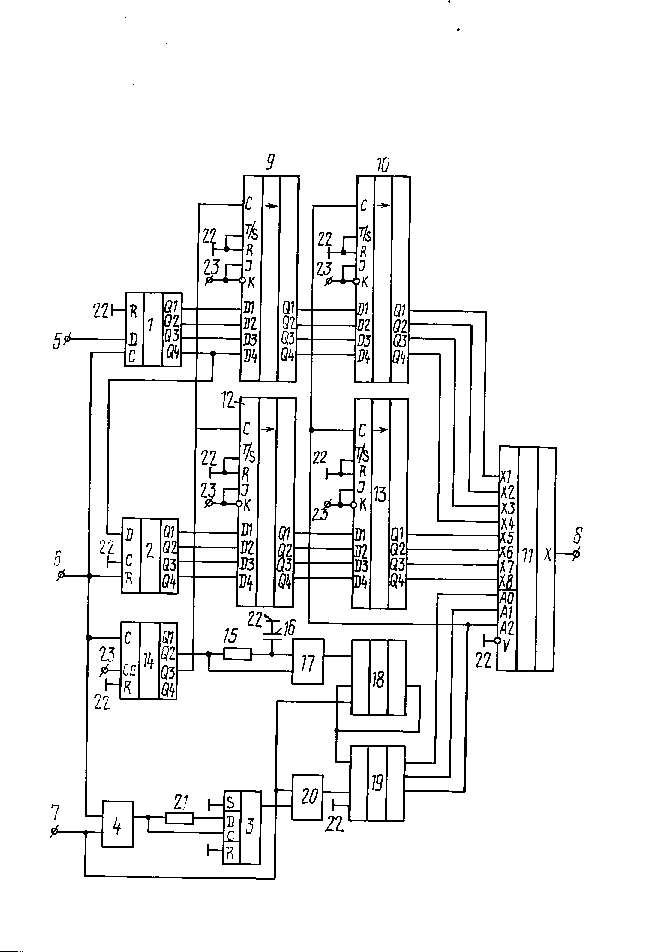

На чертеже изображен один из возможных вариантов устройства тактовой синхронизации согласно изобретению.

Устройство содержит первый и второй регистры 1 и 2, триггер 3, элемент И-НЕ 4, информационный вход 5, вход 6 тактовых импульсов приема, вход 7 тактовых импульсов передачи и информационный выход 8.

Устройство содержит также последовательно соединенные третий и четвертый регистры 9 и 10 и мультиплексор 11, последовательно соединенные пятый и шестой регистры 12 и 13, последовательно соединенные первый счетчик 14, интегратор, состоящий из резистора 15 и конденсатора 16, первый сумматор 17 по модулю два, второй и третий счетчики 18 и 19, а также второй сумматор 20 по модулю два и гасящий элемент 21. Выходы четырех разрядов первого регистра 1 соединены с соответствующими информационными входами третьего регистра 9, а выходы четырех разрядов второго регистра 2 соединены с соответствующими информационными входами пятого регистра 12. Выходы четырех разрядов шестого регистра 13 соединены с соответствующими информационными входами мультиплексора 11, адресные входы которого соединены соответственно с выходами первого и второго разрядов и с выходом третьего разряда третьего счетчика 19. Выход третьего разряда третьего счетчика 19 соединен также со входами синхронизации четвертого и шестого регистров 4 и 6, а выход второго разряда первого счетчика 14 - со вторым входом первого сумматора 17 по модулю два. Выход третьего разряда первого счетчика 14 соединен со входами синхронизации третьего и пятого регистров 9 и 12, а вход установки нуля третьего счетчика 19 - со входом синхронизации второго счетчика 18. Выход элемента И-НЕ 4 cоединен непосредственно и через гасящий элемент 21, выполненный в виде резистора, соответственно со входом синхронизации и с информационным входом триггера 3, выход которого через второй сумматор 20 по модулю два соединен со входом разрешения третьего счетчика 19. Выход четвертого разряда первого регистра 1 соединен с информационным входом второго регистра 2. При этом информационный вход первого регистра 1 является информационным входом 5 устройства.

Входы синхронизации первого и второго регистров 1 и 2 и первого счетчика 14 и первый вход элемента И-НЕ соединены между собой и являются входом 6 тактовых импульсов приема устройства, а второй вход элемента И-НЕ 4, второй вход второго сумматора 20 по модулю два соединены между собой и являются входом 7 тактовых импульсов передачи. Вход синхронизации третьего счетчика 20, входы установки нуля и единицы триггера 3, входы установки нуля первого и второго регистров 1 и 2, входы выбора прямого и обратного кода и входы установки нуля третьего, четвертого, пятого и шестого регистров 9, 10, 12 и 13, вход установки нуля первого счетчика 14 и вход запрета мультиплексора 11 соединены между собой и являются общей шиной 22 устройства, а входы последовательной записи и входы параллельного и последовательного режимов работы третьего, четвертого, пятого и шестого регистров 9, 10, 12 и 13 и вход разрешения первого счетчика 14 соединены между собой и являются входом 23 логической единицы устройства. При этом информационным выходом 8 устройства является выход мультиплексора 11.

Работа устройства тактовой синхронизации происходит следующим образом.

Принимаемый цифровой сигнал, пораженный джиттером, поступает с информационного входа 5 устройства на информационный вход первого регистра 1 и преобразуется с помощью первого и второго регистров 1 и 2 в параллельную форму. Преобразование принимаемого цифрового сигнала ведется по синфазным им тактовым импульсам приема, поступающим со входа 6 тактовых импульсов приема на входы синхронизации первого и второго регистров 1 и 2. Тактовые импульсы приема поступают также на вход синхронизации первого счетчика 14, в котором через каждые восемь тактовых импульсов приема формируется положительный перепад, поступающий на входы синхронизации третьего и пятого регистров 9 и 12. В интервалах времени между этими положительными перепадами на входах синхронизации третьего и пятого регистров 9 и 12 информация, поступающая на информационные входы четвертого и шестого регистров 10 и 13, считывается на выходы при поступлении положительных перепадов на их входы синхронизации. С выходов четвертого и шестого регистров 10 и 13 цифровая информация поступает в параллельной форме на информационные входы мультиплексора 11. Считывание информации c информационных входов четвертого и шестого регистров 10 и 13 и ее коммутация мультиплексором 11 происходит синхронно входной последовательности тактовых импульсов передачи, поступающей на вход 7 тактовых импульсов передачи. При этом последовательность тактовых импульсов приема и последовательность тактовых импульсов передачи поступают соответственно на первый и второй входы элемента И-НЕ 4. Если последовательности тактовых импульсов передачи и приема находятся в фазе, то элемент И-НЕ 4 формирует сигнал, близкий к меандру. Если последовательности тактовых импульсов передачи и приема находятся в противофазе, то элемент И-НЕ формирует уровень логической единицы с узкими отрицательными импульсами. Сигнал с выхода элемента И-НЕ 4 поступает непосредственно на вход синхронизации триггера 3 и проходит через гасящий элемент 21 на информационный вход триггера 3. При этом в триггер записывается логическая единица, если последовательности тактовых импульсов передачи и приема синфазны, и логический ноль, если они противофазны. С прямого выхода триггера 3 записанное логическое число поступает на первый вход второго сумматора 20 по модулю два, на второй вход которого подается последовательность тактовых импульсов передачи. Последовательность тактовых импульсов выбранной фазы с выхода второго сумматора 20 по модулю два поступает на вход разрешения третьего счетчика 19. С выходов первого, второго и третьего разрядов третьего счетчика 19 соответственно на младший, средний и старший адресные входы мультиплексора 11 поступают последовательности логических нулей и логических единиц, обеспечивающих преобразование информации параллельного вида в информацию последовательного вида, поступающую на выход 8 устройства.

В начале работы считывание информации четвертого и шестого триггеров 10 и 13 из третьего и пятого регистров 9 и 12 происходит близко к середине периода записи информации в четвертый и шестой регистры 10 и 13, что обеспечивает примерно равный запас на расхождение фазы между последовательностями тактовых импульсов приема и передачи в сторону опережения или запаздывания. При этом с выхода второго разряда первого счетчика 14 поступает сигнал, представляющий собой результат деления на четыре частоты последовательности тактовых импульсов приема. Сигнал с выхода второго разряда первого счетчика 14 подается непосредственно на один вход первого сумматора 17 по модулю два, а посредством резистора 15 и конденсатора 16 интегратора на другой вход первого сумматора 17 по модулю два. В результате этого первый сумматор 17 по модулю два формирует узкие положительные импульсы, период следования которых в два раза больше, чем у последовательности тактовых импульсов приема. Узкие положительные импульсы с выхода первого сумматора 17 по модулю два подаются на вход установки нуля второго счетчика 18, на вход разрешения которого поступает последовательность тактовых импульсов передачи. Уровень логической единицы с выхода третьего разряда второго счетчика 17 поступает на его вход синхронизации и на вход установки нуля третьего счетчика 19. Благодаря этому положительный перепад считывания, поступающий на входы синхронизации четвертого и шестого регистров 10 и 13, приходится посредине между положительными перепадами записи, поступающими на входы синхронизации третьего и пятого регистров 9 и 12. (56) Авторское свидетельство СССР N 1109930, кл. Н 04 L 7/04, 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИИМПУЛЬСНОГО СИГНАЛА | 1992 |

|

RU2048706C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ | 1992 |

|

RU2047870C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА | 1991 |

|

RU2010428C1 |

| УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2013015C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2010427C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1990 |

|

RU2007882C1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ СИГНАЛА ТЕСТА | 1990 |

|

RU2007864C1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1992 |

|

RU2029357C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

Использование: в технике электрической связи, а именно в устройствах тактовой синхронизации. Сущность изобретения: устройство тактовой синхронизации содержит первый и второй регистры 1, 2, триггер 3, элемент И-НЕ 4, регистры 9, 10, мультиплексор 10, регистры 12, 13, первый счетчик 14, интегратор, состоящий из резисторов 15 и конденсатора 16, первый сумматор 17 по модулю два, второй и третий счетчики 18, 19, второй сумматор 20, гасящий элемент 21. Устройство обеспечивает повышение помехоустойчивости. 1 ил.

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержащее первый и второй регистры, триггер и элемент И - НЕ, информационный вход, входы тактовых импульсов приема и передачи и информационный выход, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные третий и четвертый регистры и мультиплексор, последовательно соединенные пятый и шестой регистры, последовательно соединенные первый счетчик, интегратор, первый сумматор по модулю два, второй и третий счетчики, а также второй сумматор по модулю два и гасящий элемент, при этом выходы четырех разрядов первого регистра соединены с соответствующими информационными входами третьего регистра, выходы четырех разрядов второго регистра соединены с соответствующими информационными входами пятого регистра, выходы четырех разрядов шестого регистра соединены с соответствующими информационными входами мультиплексора, адресные входы которого соединены соответственно с выходами первого и второго разрядов и с выходом третьего разряда третьего счетчика, который соединен с входами синхронизации четвертого и шестого регистров, выход второго разряда первого счетчика соединен с вторым входом первого сумматора, а выход третьего разряда первого счетчика соединен с входами синхронизации третьего и пятого регистров, вход установки нуля третьего счетчика соединен с входом синхронизации второго счетчика, выход элемента И - НЕ соединен непосредственно и через гасящий элемент соответственно с входом синхронизации и с информационным входом триггера, выход которого через второй сумматор по модулю два соединен с входом разрешения третьего счетчика, а выход четвертого разряда первого регистра соединен с информационным входом второго регистра, причем информационный вход первого регистра является информационным входом устройства, входы синхронизации первого и второго регистров и первого счетчика и первый вход элемента И - НЕ соединены между собой и являются входом тактовых импульсов приема устройства, второй вход элемента И - НЕ, второй вход второго сумматора по модулю два и вход разрешения второго счетчика соединены между собой и являются входом тактовых импульсов передачи, вход синхронизации третьего счетчика, входы установки нуля и единицы триггера, входы установки нуля первого и второго регистров, входы выбора прямого и обратного кода и входы установки нуля третьего, четвертого, пятого и шестого регистров, вход установки нуля первого счетчика и вход запрета мультиплексора соединены между собой и являются общей шиной устройства, а входы последовательной записи и входы параллельного и последовательного режимов работы третьего, четвертого, пятого и шестого регистров и вход разрешения первого счетчика соединены между собой и являются входом логической единицы устройства, информационным выходом которого является выход мультиплексора.

Авторы

Даты

1994-03-15—Публикация

1990-04-23—Подача