Изобретение относится к вычислительной технике и может использоваться при построении блоков памяти.

Известны запоминающие устройства (ЗУ) на сердечниках, состоящий из регистра адреса, дешифраторов адреса, устройств выборки, накопителя и разрядной части, причем выходы регистра адреса соединены с входами дешифраторов адреса [1]

Недостатками таких ЗУ являются низкое быстродействие, большая стоимость и большие габариты.

Наиболее близким по технической сущности к предлагаемому является ЗУ на полупроводниковых микросхемах памяти. Такое ЗУ состоит из регистра адреса, выходы которого соединены с входами микросхем памяти накопителя [2] .

Недостатком такого ЗУ является снижение быстродействия и надежности из-за увеличения количества микросхем (нагрузки) памяти, подключаемых к выходам регистра адреса.

Целью изобретения является повышение быстродействия и надежности полупроводниковых ЗУ.

Цель достигается тем, что в ЗУ, состоящем из n микросхем памяти и регистра адреса, выходы которого подключены к m из n микросхем памяти, регистр адреса выполнен на элементах, имеющих инверсные выходы, к которым подключены остальные n-m микросхемы памяти. При этом происходит разделение нагрузки на выходы регистра адреса, что позволяет улучшить фронты кодов адреса. Указанное новое свойство обеспечивает увеличение быстродействия и надежности, т. е. новый положительный эффект. В результате предложенное техническое решение соответствует критерию "существенные отличия".

Заявляемое ЗУ отличается от прототипа тем, что его регистр адреса выполнен на элементах, имеющих инверсные выходы, соединенные с частью микросхем памяти накопителя.

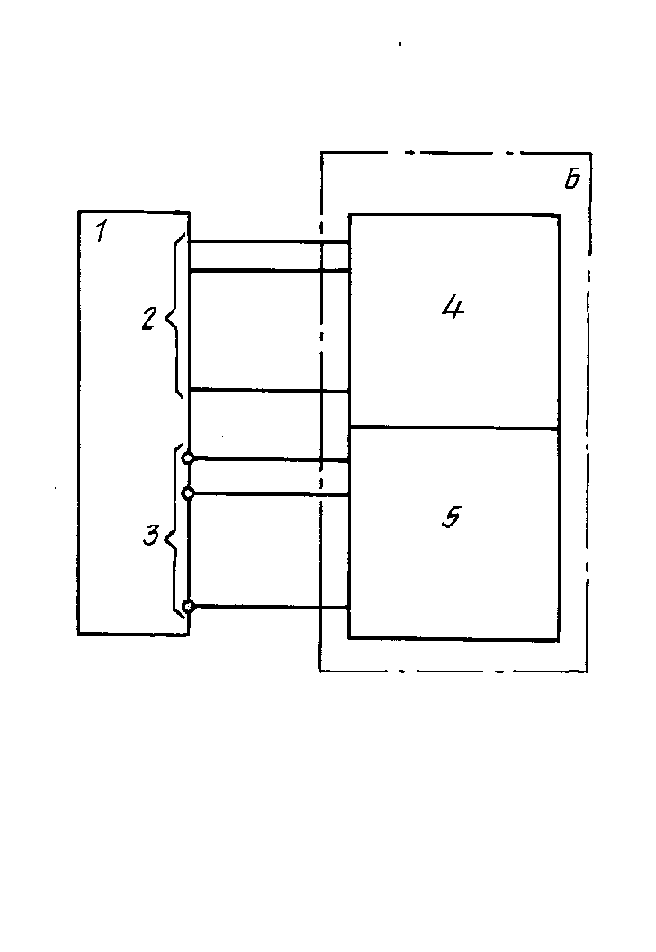

На чертеже приведена схема предлагаемого ЗУ.

ЗУ содержит регистр 1 адреса, имеющий прямые 2 и инверсные 3 выходы, соединенные соответственно с m и n-m (n и m - целые числа, причем n больше m) микросхемами 4, 5 памяти накопителя 6.

ЗУ работает следующим образом.

В соответствии с кодом адреса, поступающим на регистр 1, происходит возбуждение ячеек памяти m микросхем, соединенных с прямыми выходами 2, и n-m микросхем, соединенных с инверсными 3 выходами регистра 1, соответственно по прямым и инверсным адресам.

Использование предлагаемого устройства позволяет уменьшить нагрузку на выход регистра адреса в два раза, что увеличивает быстродействие и надежность ЗУ.

(56) 1. Крайзмер Л. П. Быстродействующие ферромагнитные ЗУ. М. : Энергия, 1964.

2. Огнев И. В. , Шамаев Ю. М. Проектирование ЗУ. М. : Высшая школа, 1979, с. 45.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| МОЛЕКУЛЯРНО-ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2068586C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| ЦИФРОВОЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010238C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1517737A1 |

Изобретение относится к вычислительной технике и может использоваться при построении блоков памяти. Устройство содержит регистр 1 адреса, накопитель 6. 1 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО , содеpжащее pегистp адpеса и N полупpоводниковых накопителей, соединенных с соответствующими дешифpатоpами, отличающееся тем, что, пpямые выходы pегистpа адpеса соединены с соответствующими входами M дешифpатоpов, а инвеpсные выходы pегистpа адpеса - с N - M входами дешифpатоpов.

Авторы

Даты

1994-03-30—Публикация

1991-05-05—Подача