Изобретение относится к вычислительной технике, в частности к микропрограммным устройствам управления.

Известно микропрограммное устройство управления [1] , содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, узел формирования адреса и коммутатор.

Недостаток такого устройства - отсутствие возможности микропрограммной организации временных задержек и временного отсчета отсутствия логического условия (сигнала) при реализации режима ожидания.

Наиболее близким к предлагаемому по технической сущности является микропрограммное устройство управления [2] , содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, формирователь адреса, счетчик, регистр хранения адреса перехода, причем выход регистра адреса микрокоманд соединен с адресным входом блока памяти микрокоманд, выход кода микрокоманд которого подключен к информационному входу регистра микрокоманд, первому информационному входу формирователя адреса, к установочному входу счетчика, входу записи кода счетчика, управляющему входу счетчика, выход которого соединен с первым управляющим входом формирователя адреса, второй управляющий вход которого подключен к входу признака устройства, выход формирователя адреса соединен с информационным входом регистра адреса микрокоманд, выход регистра микрокоманд является информационным выходом устройства, установочный вход и вход записи адреса регистра хранения адреса перехода подключены к соответствующим выходам блока памяти микрокоманд, выход регистра хранения адреса перехода соединен с вторым информационным входом формирователя адреса.

Недостатком известного микропрограммного устройства управления является аппаратная избыточность, вызванная необходимостью хранения в отдельном поле микрокоманды адреса перехода, который необходим только по окончании выполнения цикла, для выхода из последнего.

Цель изобретения - сокращение аппаратных затрат за счет повышения плотности хранения информации.

Цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, формирователь адреса, счетчик, регистр хранения адреса перехода, причем группа выходов регистра хранения адреса перехода соединена с третьей группой информационных входов формирователя адреса, группа выходов которого соединена с группой информационных входов регистра адреса, группа выходов которого соединена с группой адресных входов блока памяти, группа выходов кода микрокоманд которого соединена с группой информационных входов регистра микрокоманд, первая группа выходов которого является группой информационных выходов устройства, дополнительно введены второй счетчик, три триггера, демультиплексор, три элемента И, элемент задержки, генератор синхроимпульсов, вход которого соединен с единичным выходом первого триггера, единичный вход которого является входом запуска устройства, а нулевой вход соединен с первым управляющим выходом регистра микрокоманд, вторая группа информационных выходов которого соединена с второй группой информационных входов формирователя адреса, первой группой информационных входов которого является группа входов кода операций, а четвертым информационным входом является вход логических условий, управляющий вход формирователя адреса соединен с выходом первого элемента И, третья группа информационных выходов регистра микрокоманд соединена с группами информационных входов демультиплексора и первого счетчика, инверсный выход которого соединен с первыми входами первого и третьего элементов И, выход третьего элемента И соединен с R-входами регистра хранения адреса перехода и третьего триггера, единичный выход которого соединен с вторым входом первого элемента И, второй управляющий выход регистра микрокоманд соединен с управляющим входом первого счетчика и S-входом второго триггера, единичный выход которого соединен с Т-входом второго счетчика и первым входом второго элемента И, выход которого соединен с входом синхронизации регистра хранения адреса перехода, третий управляющий выход регистра микрокоманд соединен с вычитающим входом первого счетчика и входом элемента задержки, выход которого соединен с R-входами второго триггера и второго счетчика, выход которого соединен с управляющим входом демультиплексора, выходы которого соединены с соответствующими входами регистра хранения адреса перехода, первый выход генератора синхроимпульсов соединен с входом синхронизации регистра адреса и суммирующим входом второго счетчика, второй выход генератора синхроимпульсов соединен с входом синхронизации регистра микрокоманд и вторым входом третьего элемента И, третий выход генератора синхроимпульсов соединен с входом синхронизации первого счетчика и вторым входом второго элемента И.

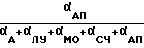

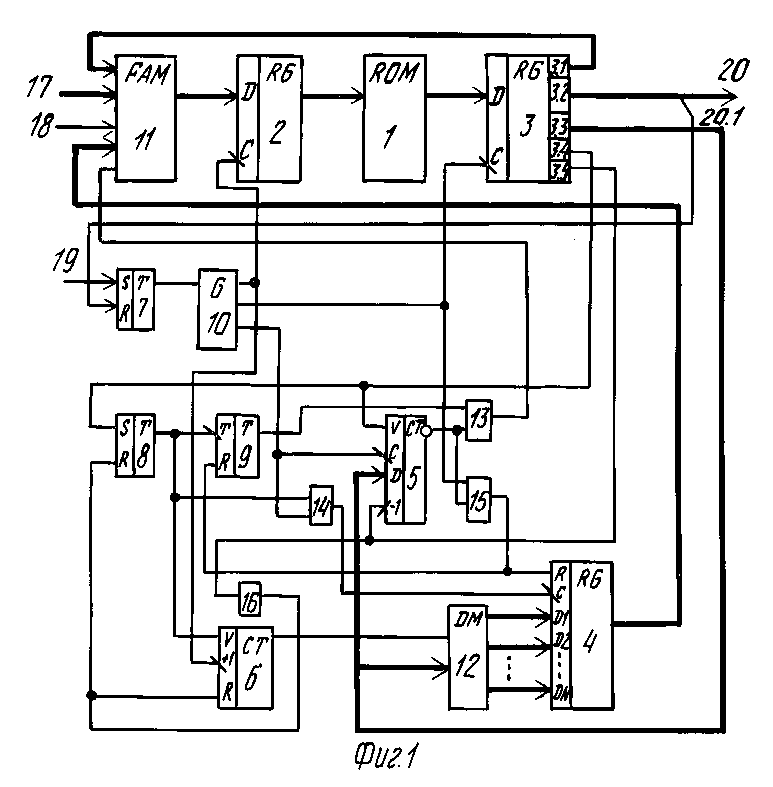

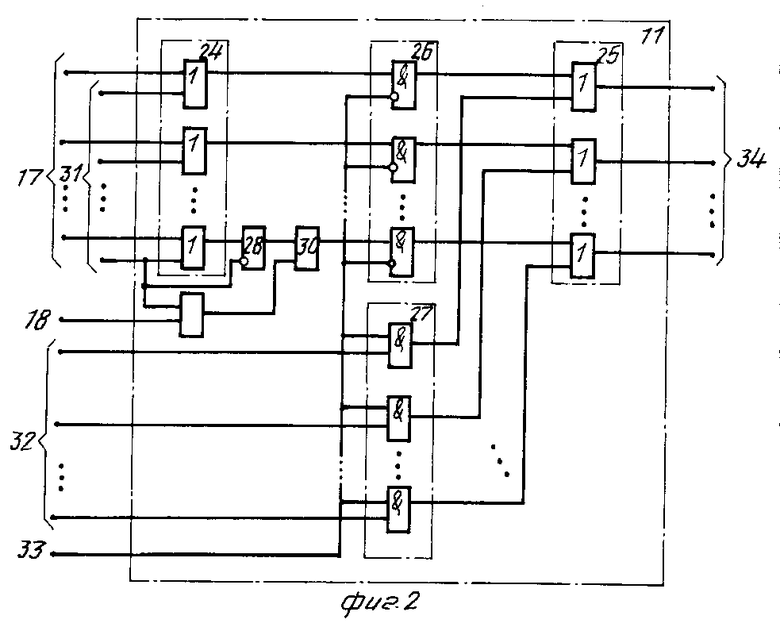

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 - функциональная схема формирователя адреса микрокоманд; на фиг. 3 - функциональная схема регистра хранения адреса перехода.

Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микрокоманд с полями: 3.1 - формирователя адреса, 3.2 - микроопераций, 3.3 - счетчика, 3.4 и 3.5 - одноразрядных меток, регистр 4 хранения адреса перехода, первый и второй счетчики 5, 6, первый - третий триггеры 7-9 генератор 10 синхроимпульсов с выходами, 10.1-10.3 сигналов синхронизации τ1-τ3соответственно, формирователь 11 адреса, демультиплексор 12, первый-третий элементы И 13-15, элемент 16 задержки, входы 17 кода операции, вход 18 логического условия, вход 19 запуска, выходы 20 микроопераций, выход 20.1 микрооперации "Конец операции".

Формирователь 11 адреса (фиг. 2) содержит две группы элементов ИЛИ 24, 25, две группы элементов И 26, 27, два элемента И 28, 29, элемент ИЛИ 30, первые-третьи группы информационных входов 17, 31, 32 формирователя, управляющий вход 33, группу элементов 34.

Регистр 4 хранения адреса перехода (фиг. 3) содержит группы регистров 21 (21.1-21. N), элементов И 22 (И 22.1-И 22. N), ИЛИ 3 (23.1-23. N), группы выходов 35 и входов 36.

Группа выходов регистра 4 хранения адреса перехода соединена с третьей группой информационных входов формирователя 11, группа выходов которого соединена с группой информационных входов регистра 2 адреса, группа выходов которого соединена с группой адресных входов блока 1 памяти, группа выходов кода микрокоманд которого соединена с группой информационных входов регистра 3 микрокоманд, первая группа информационных выходов (выходы поля 3.1 адреса) которого являются группой информационных выходов 20 устройства.

Вход генератора 10 синхроимпульсов соединен с единичным выходом первого триггера 7, единичный вход которого является входом 19 запуска устройства, а нулевой вход соединен с первым управляющим выходом (выход 20.1 поля 3.2) регистра 3 микрокоманд, вторая группа информационных выходов (выходы поля 3.2 микрооперации) которого соединена с второй группой информационных входов формирователя 11 адреса, первой группой информационных входов которого являются группа входов 17 устройства (входы кода операций), а четвертым информационным входом является вход 18 логических условий, управляющий вход формирователя 11 адреса соединен с выходом первого элемента И 13, третья группа информационных выходов (выходы поля 3.3 счетчика) регистра 3 микрокоманд соединена с группами информационных входов демультиплексора 12 и первого счетчика 5, инверсный выход которого соединен с первыми входами элементов И 13, 15, выход третьего элемента И 15 соединен с R-входами регистра 4 хранения адреса перехода и третьего триггера 9, единичный выход которого соединен с вторым входом первого элемента И 13, второй управляющий выход (выход поля 3.4 метки) регистра 3 микрокоманд соединен с управляющим входом первого счетчика 5 и S-входом второго триггера 8, единичный выход которого соединен с Т-входом второго счетчика 6 и первым входом второго элемента И 14, выход которого соединен с входом синхронизации регистра 4 хранения адреса перехода, третий управляющий выход (выход поля 3,5 метки) регистра 3 микрокоманд соединен с вычитающим входом первого счетчика 5 и входом элемента 16 задержки, выход которого соединен с R-входами второго триггера 8 и второго счетчика 6, выход которого соединен с управляющим входом демультиплексора 12, выходы которого соединены с соответствующими входами регистра 4 хранения адреса перехода, первый выход 10.1 генератора 10 синхроимпульсов соединен с входом синхронизации регистра 2 адреса и суммирующим входом второго счетчика 6, второй выход 10.2 генератора 10 синхроимпульсов соединен с входом синхронизации регистра 3 микрокоманд и вторым входом третьего элемента И 15, третий выход 10.3 генератора 10 синхроимпульсов соединен с входом синхронизации первого счетчика 5 и вторым входом второго элемента И 14.

Устройство работает следующим образом.

В исходном состоянии элементы памяти находятся в нулевом состоянии, а в блок 1 памяти записаны микропрограммы. Шины установки элементов в исходное состояние не показаны. Код операции через группу входов 17 устройства поступает на первую группу информационных входов формирователя 11 адреса, на выходах которого формируется адрес первой микрокоманды. Единичным сигналом на входе 19 запуска устройства переводится в единичное состояние триггер 7, единичный сигнал с выхода которого поступает на управляющий вход генератора 10 синхроимпульсов, разрешая формирование последовательностей синхроимпульсов τ1-τ3 на выходах 10.1-10.3 генератора 10 синхроимпульсов. По заднему фронту синхроимпульса τ1, поступающего с выхода 10.1 генератора 10 синхроимпульсов на синхровход регистра 2 адреса, адрес микрокоманды с выходов формирователя 11 адреса заносится в регистр 2 адреса.

В соответствии с начальным адресом, поступающим на адресный вход блока 1 памяти с выхода регистра 2 адреса, из блока 1 памяти считывается первая микрокоманда микропрограммы. По заднему фронту синхроимпульса τ2, поступающего с выхода 10.2 генератора 10 синхроимпульсов на управляющий вход регистра 3 микрокоманд, первая микрокоманда заносится в регистр 3 микрокоманд. Одна часть этой микрокоманды, содержащая поле информации, предназначенной для внешних устройств (поле 3.2), выводится на выходы 20 устройства. Другая часть микрокоманды содержит следующие поля.

Поле 3.1 адреса. В этом поле содержится в прямой или косвенной форме информация об адресе следующей микрокоманды, а также указывается код операции, которую надо проделать с указанной информацией, чтобы получить адрес очередной микрокоманды.

Поле 3.3 счетчика. Это поле содержит код числа циклов, который записывается в счетчик 5 циклов по сигналу-метке разрешения записи, формирующемуся в поле 3.4. Кроме того, в поле 3.3 счетчика по частям записывается код адреса перехода.

Поле 5.5 метки. В поле содержится метка окончания выполнения текущего участка.

Если первая микрокоманда не является микрокомандой начала цикла, то на выходах поля 3.3 счетчика регистра 3 микрокоманд формируется нулевой код. Одновременно на выходах поля 3.2 микроопераций регистра 3 микрокоманд формируются коды микроопераций, которые поступают на выходы 20 устройства. Адрес следующей микрокоманды и код условия с выходов поля 3.1 адреса регистра 3 поступают на вторую группу с информационных входов формирователя 11 адреса.

Работу формирователя 11 адреса поясняет функциональная схема, представленная на фиг. 2. Конкретная реализация этого формирователя не влияет на сущность работы предлагаемого устройства, поэтому на фиг. 2 дана одна из простейших возможных реализаций формирователя 11 адреса. При этом формирователь 11 адреса может осуществлять прием кода адреса микрокоманды с входа 17 устройства и две операции выработки адреса следующей микрокоманды: операцию безусловного перехода и операцию условного перехода по признаку, поступающему из внешнего устройства через информационный вход 18 логического условия. В данном случае младший разряд кода, поступающего на группу информационных входов 31 формирователя 11 адреса с поля 3.1 адреса регистра 3 микрокоманд (фиг. 1), является кодом условия, при единичном значении которого запирается элемент И 28 и сигнал признака, поступающего из внешнего устройства на информационный вход 18 устройства, через элементы И 29, ИЛИ 30 поступает на первый вход элемента И 26. N, а при нулевом значении которого на первый вход элемента И 26. N через элементы ИЛИ 24. N, И 28 подается младший разряд кода адреса следующей микрокоманды. Остальные разряды кода адреса следующей микрокоманды поступают с группы входов 31 формирователя 11 адреса или с группы входов 17 устройства через группы элементов ИЛИ 24 на первые входы группы элементов И 26, а на первые входы группы элементов И 27 с группы информационных входов 32 формирователя 11 подаются разряды кода адреса перехода, поступающие на группу входов 32 формирователя 11 адреса с выхода регистра 4 хранения адреса перехода (фиг. 1). На вторые входы группы элементов И 27 и на вторые инверсные входы группы элементов И 26 с входа 33 управления формирователя 11 адреса подается управляющий сигнал, поступающий с выхода элемента И 13 (фиг. 1). В зависимости от этого сигнала на группу выходов 34 формирователя 11 адреса поступает через группу элементов ИЛИ 25 либо код адреса микрокоманд с выходов группы элементов И 27, либо И 26.

В начале работы формирователя 11 адреса через группу входов 17 устройства код адреса первой микрокоманды поступает на вторые входы группы элементов ИЛИ 24 и далее через группы элементов И 26 и ИЛИ 25 на группу выходов 34 формирователя 11 адреса. Модификация младшего разряда при этом не производится, так как на группе входов 31 сформирован нулевой код и на входе 33 управления формирователем 11 присутствует нулевой сигнал.

Код адреса второй микрокоманды, если первая микрокоманда не является микрокомандой начала цикла, поступает с выходов поля 3.1 регистра 3, формируется в формирователе 11 адреса и по заднему фронту очередного синхроимпульса τ 1 с выхода 10.1 генератора 10 синхроимпульсов заносится в регистр 2 адреса и дальнейшая работа устройства происходит аналогично описанному ранее.

Если текущая микрокоманда является микрокомандой начала цикла, то при ее записи в регистр 3 микрокоманд в поле 3.3 счетчика регистра 3 микрокоманд формируется ненулевой код, что определяется появлением единичного сигнала на выходе поля 3.4 метки регистра 3 микрокоманд, который поступает на управляющий вход счетчика 5 циклов и S-вход триггера 8, устанавливая его в единичное состояние. По заднему фронту синхроимпульса τ 3 с выхода 10.3 генератора 10 синхроимпульсов в счетчик 5 циклов заносится код счетчика с выходов поля 3.3 счетчика регистра 3 микрокоманд. Код счетчика не проходит через демультиплексор 12 на входы регистра 4 хранения адреса перехода, так как на управляющие входы демультиплексора 12 с выходов счетчика 6 поступает нулевой код, а подключаемые при этом выходы демультиплексора 12 в данном устройстве не используются. Единичный сигнал с единичного выхода триггера 8 поступает на управляющий вход счетчика 6, разрешая его работу, и на Т-вход триггера 9.

При записи очередной микрокоманды в регистр 3 микрокоманд в поле 3.3 счетчика записывается часть кода адреса перехода. Полный код адреса перехода формируется следующим образом.

Каждый раз по заднему фронту синхроимпульса τ 3 с выхода 10.1 генератора 10 синхроимпульсов содержимое счетчика 6 увеличивается на единицу (при единичном состоянии триггера 8), тем самым обеспечивается коммутация выходов демультиплексора 12, на вход которого поступают части кода адреса перехода с выходов поля 3.3 счетчика регистра 3 микрокоманд. Запись (формирование) кода адреса перехода осуществляется в регистре 4 хранения адреса перехода по заднему фронту синхроимпульса τ 3, поступающего с выхода 10.3 генератора 10 синхроимпульсов через элемент И 14 на управляющий вход регистра 4 хранения адреса перехода.

Работу регистра 4 хранения адреса перехода поясняет функциональная схема, представленная на фиг. 3. В исходном состоянии в регистрах 21.1-21. N записаны нулевые коды. Поступающий синхроимпульс на вход синхронизации регистра 4 хранения адреса перехода проходит через открытые элементы И 22.1-22. N на входы синхронизации регистров 21.1-21. N, обеспечивая этим занесение в регистр 21. i (i =  ) информации, поступающей с входа 36. i. При этом на выходе элемента ИЛИ 23. i формируется единичный сигнал, который поступает на инверсный вход соответствующего элемента И 22. i, запрещая прохождение очередных синхроимпульсов на вход синхронизации соответствующего регистра 21. i. Выходы регистров 21.1-21. N образуют группу информационных выходов 35 регистра 4 хранения адреса перехода. Обнуление регистров 21.1-21. N производится одновременно по сигналу, поступающему на R-вход регистра 4 хранения адреса перехода. Приведенный механизм блокировки синхровхода регистра 21. i (i =

) информации, поступающей с входа 36. i. При этом на выходе элемента ИЛИ 23. i формируется единичный сигнал, который поступает на инверсный вход соответствующего элемента И 22. i, запрещая прохождение очередных синхроимпульсов на вход синхронизации соответствующего регистра 21. i. Выходы регистров 21.1-21. N образуют группу информационных выходов 35 регистра 4 хранения адреса перехода. Обнуление регистров 21.1-21. N производится одновременно по сигналу, поступающему на R-вход регистра 4 хранения адреса перехода. Приведенный механизм блокировки синхровхода регистра 21. i (i =  ) обеспечивает при переходе очередного синхроимпульса возможность занесения информации, поступающей с входа 36. i+1 регистра 4 хранения адреса перехода, без ее уничтожения в регистре 21. i ввиду отсутствия на информационном входе 36. i информации.

) обеспечивает при переходе очередного синхроимпульса возможность занесения информации, поступающей с входа 36. i+1 регистра 4 хранения адреса перехода, без ее уничтожения в регистре 21. i ввиду отсутствия на информационном входе 36. i информации.

При появлении единичного потенциала на выходе поля 3.5 метки регистра 3 микрокоманд, обозначающего выполнение последней микрокоманды циклического участка, содержимое счетчика 5 циклов уменьшается на единицу. Одновременно единичный потенциал с выхода поля 3.5 метки регистра 3 микрокоманд, пройдя через элемент 16 задержки, переводит триггер 8 и счетчик 6 в нулевое состояние. Задержка в элементе 16 задержки осуществляется на время, необходимое для записи последней части кода адреса перехода в регистр 4 хранения адреса перехода. Нулевой потенциал с единичного выхода триггера 8 запирает элемент И 14, тем самым запрещая дальнейшее поступление синхроимпульсов τ 3 с выхода 10.3 генератора 10 синхроимпульсов на синхровход регистра 4 хранения адреса перехода. Кроме того, этим же нулевым сигналом запрещается работа счетчика 6. Одновременно, по заднему фронту сигнала на единичном выходе триггера 8 переводится в единичное состояние триггер 9. В результате единичный потенциал на единичном выходе последнего открывает по первому входу элемент И 13. К этому времени на регистре 4 хранения адреса перехода полностью сформирован код адреса перехода. По окончании очередного выполнения циклического участка содержимое счетчика 5 уменьшается на единицу по сигналу с поля 3.5 метки регистра 3 микрокоманд. Моменту завершения выполнения циклического участка требуемое число раз соответствует появление единичного сигнала на инверсном выходе счетчика 5, который формируется после появления в поле 3.5 метки регистра 3 микрокоманд по синхроимпульсу τ 2 очередной метки. В результате на выходе элемента И 13 формируется единичный сигнал, который поступает на управляющий вход 3.3 на фиг. 2) формирователя 11 адреса. Адрес перехода с выхода регистра 4 хранения адреса перехода поступает на информационный вход формирователя 11 адреса (вход 32 на фиг. 2) и через формирователь 11 адреса поступает на информационный вход регистра 2 адреса. По заднему фронту очередного синхроимпульса τ 1 с выхода 10.1 генератора 10 синхроимпульсов адрес перехода заносится в регистр 2 адреса. По синхроимпульсу τ 2 с выхода 10.2 генератора 10 синхроимпульсов в соответствии с адресом перехода очередная микрокоманда заносится в регистр 3 микрокоманд. Одновременно синхроимпульс τ 2проходит через элемент И 15, открытый по второму входу единичным сигналом с выхода счетчика 5, на R-входы регистра 4 хранения адреса перехода и триггера 9, переводя их в нулевое состояние. В результате единичный сигнал с выхода элемента И 13 снимается и формирователь 11 адреса формирует адрес очередной микрокоманды в соответствии с кодом в поле 3.1 адреса регистра 3 микрокоманд. С приходом очередного синхроимпульса τ 1 с выхода 10.1 генератора 10 синхроимпульсов сформированный адрес очередной микрокоманды заносится в регистр 2 адреса и в дальнейшем работа устройства происходит аналогично описанному ранее.

При появлении единичного сигнала на выходе 20.1 микрооперации "Конец операции" триггер 7 переводится в нулевое состояние, при этом происходит останов генератора 10 синхроимпульсов. На этом работа устройства завершается.

С приходом единичного сигнала на вход 19 запуска работа устройства возобновляется.

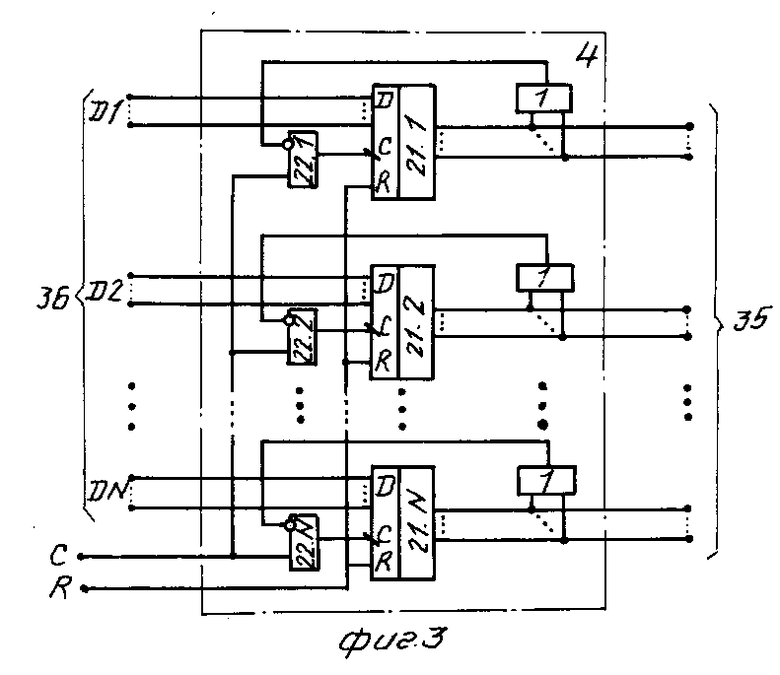

Таким образом, предлагаемое устройство позволяет получить существенный выигрыш в экономии памяти устройства, особенно при выполнении циклических программ, за счет повышения плотности хранения информации путем использования поля счетчика микрокоманды для хранения адреса перехода при завершении циклического участка микропрограммы. А именно, экономия памяти δα предлагаемого устройства по сравнению с прототипом будет составлять:

δα =  1-

1-  100% , где α' мк, α мк - объемы памяти, занимаемой микрокомандой соответственно в предлагаемом устройстве и устройстве прототипе;

100% , где α' мк, α мк - объемы памяти, занимаемой микрокомандой соответственно в предлагаемом устройстве и устройстве прототипе;

α мк = α А + α лу + α мо + α сч + α ап,

α' мк = α А + α лу + α мо + α сч, где α А - объем поля адреса микрокоманды;

α лу - объем поля логических условий;

α сч - объем поля счетчика микрокоманды;

α ап - объем поля адреса перехода;

α мо - объем поля микрооперации.

Тогда

δα =  1-

1-  100% =

100% =  ·100%

·100%

Для значений α А = 8 байт, α лу = 4 байт, α мо = 16 байт, α сч = 4 байт, α ап = 8 байт выигрыш в экономии памяти δα будет составлять:

δα =  ·100% =

·100% =  ·100% = 20%

·100% = 20%

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для последовательного выделения единиц из двоичного кода | 1990 |

|

SU1795458A1 |

| Устройство для отображения информации | 1981 |

|

SU963080A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для отображения информации | 1985 |

|

SU1316028A2 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

Изобретение относится к вычислительной технике, в частности к микропрограммным устройствам управления. Целью изобретения является сокращение аппаратных затрат. Цель достигается тем, что устройство содержит блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, формирователь адреса, два счетчика, генератор синхроимпульсов, регистр хранения адреса перехода, три триггера, демультиплексор, три элемента И и элемент задержки. 3 ил.

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, формирователь адреса, первый счетчик, генератор синхроимпульсов, регистр хранения адреса перехода, причем группа выходов регистра хранения адреса перехода соединена с первой группой информационных входов формирователя адреса, группа выходов которого соединена с группой информационных входов регистра адреса, группа выходов которого соединена с группой адресных входов блока памяти, группа выходов кода микрокоманд которого соединена с группой информационных входов регистра микрокоманд, группа выходов поля микроопераций которого является группой выходов устройства, отличающееся тем, что, с целью сокращения аппаратных затрат устройства, оно содержит второй счетчик, три триггера, демультиплексор, три элемента И, элемент задержки, вход генератора синхроимпульсов соединен с прямым выходом первого триггера, вход установки в "1" которого является входом запуска устройства, а вход установки в "0" соединен с выходом регистра признака конца операции микрокоманд, группа выходов поля адреса которого соединена с второй группой информационных входов формирователя адреса, третьей группой информационных входов которого является группа входов кода операции устройства, а четвертый группой информационных входов является вход логических условий устройства, управляющий вход формирователя адреса соединен с выходом первого элемента И, группа выходов поля числа циклов регистра микрокоманд соединена с группами информационных входов демультиплексора и первого счетчика, инверсный выход переноса которого соединен с первыми входами первого и третьего элементов И, выход третьего элемента И соединен с R-входами регистра хранения адреса перехода и третьего триггера, прямой выход которого соединен с вторым входом первого элемента И, выход признака начала цикла регистра микрокоманд соединен с управляющим входом первого счетчика и S-входом второго триггера, прямой выход которого соединен с T -входом второго триггера, управляющим входом второго счетчика и первым входом второго элемента И, выход которого соединен с входом синхронизации регистра хранения адреса перехода, выход признака окончания выполнения текущего участка регистра микрокоманд соединен с вычитающим входом первого счетчика и входом элемента задержки, выход которого соединен с R-входом второго триггера и второго счетчика, выход которого соединен с управляющим входом демультиплексора, выходы которого соединены с соответствующими входами регистра хранения адреса перехода, первый выход генератора синхроимпульсов соединен с входом синхронизации регистра адреса и суммирующим входом второго счетчика, второй выход генератора синхроимпульсов соединен с входом синхронизации регистра микрокоманд и вторым входом третьего элемента И, третий выход генератора синхроимпульсов соединен с входом синхронизации первого счетчика и вторым входом второго элемента И.

Авторы

Даты

1994-05-30—Публикация

1991-06-28—Подача