сд оо о

00 00

го

Изобретение относится к вычислительной технике и может найти применение при построении высокопроизводительных вычислительных систем, муль- типроцессоров с динамической архитектурой ,микроконтроллеров с множествен- ным потоком команд управления при организации волновых, систолических, матричных и конвейерных процессов.

Целью изобретения является расширение области применения устройства за счет обеспечения возможности обмена информацией в матричной распределенной вычислительной системе по двум направлениям.

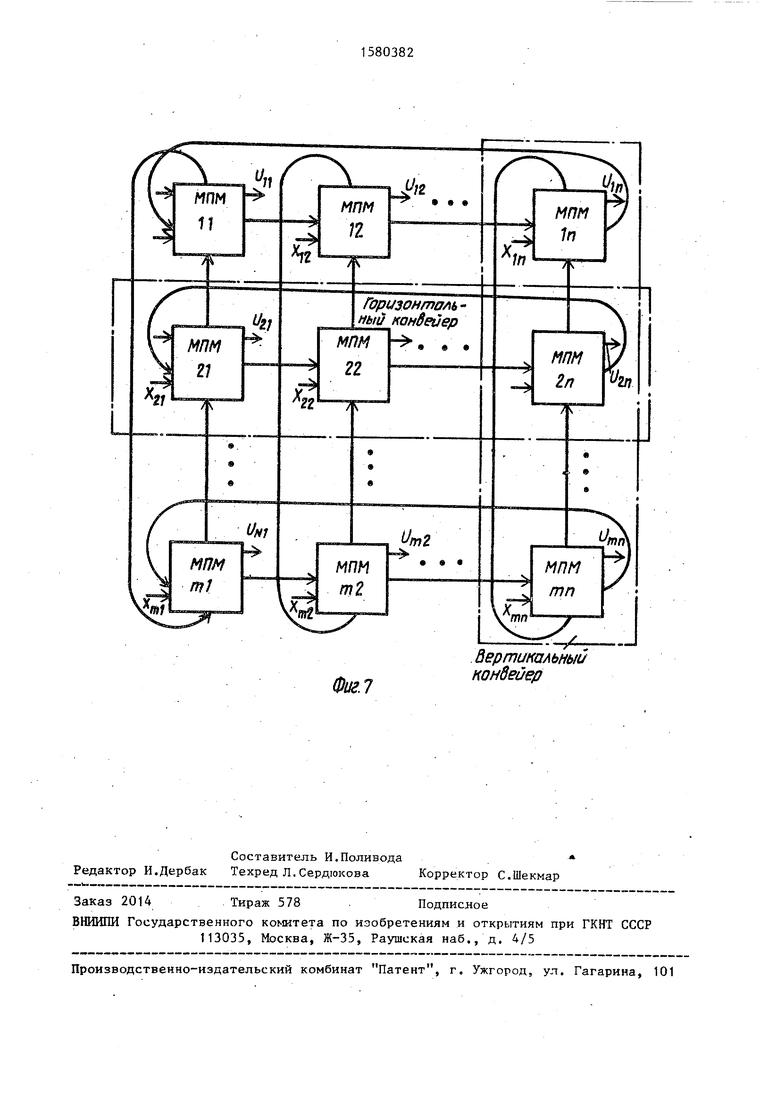

Микропрограмма, выполняемая устройством, состоит из двух подмножест операционных микрокоманд (нанокоманд М и М« причем Mt Л Мг 0 . Первый тип нанокоманд (М ) предназначен для управления операционным блоком. Во время выполнения микропрограммы устройство может выдавать на аналогичное устройство нанокоманды второго типа (M.j), образующие подмножество нанокоманд передачи управления.

Формат нанокоманды передачи управления представляется в виде

м«

где т „р - номер (код) модульного устройства - приемника информации;m R - номер (код) микропрограммы, которую должно выполнить устройство - приемник (начальный адрес микропрограммы) ; Ф - знак сцепления. свою очередь

m

Яр

m г ,

где m и m - соответственно коды адресов местоположения устройства в матрице однотипных устройств распределенной системы.

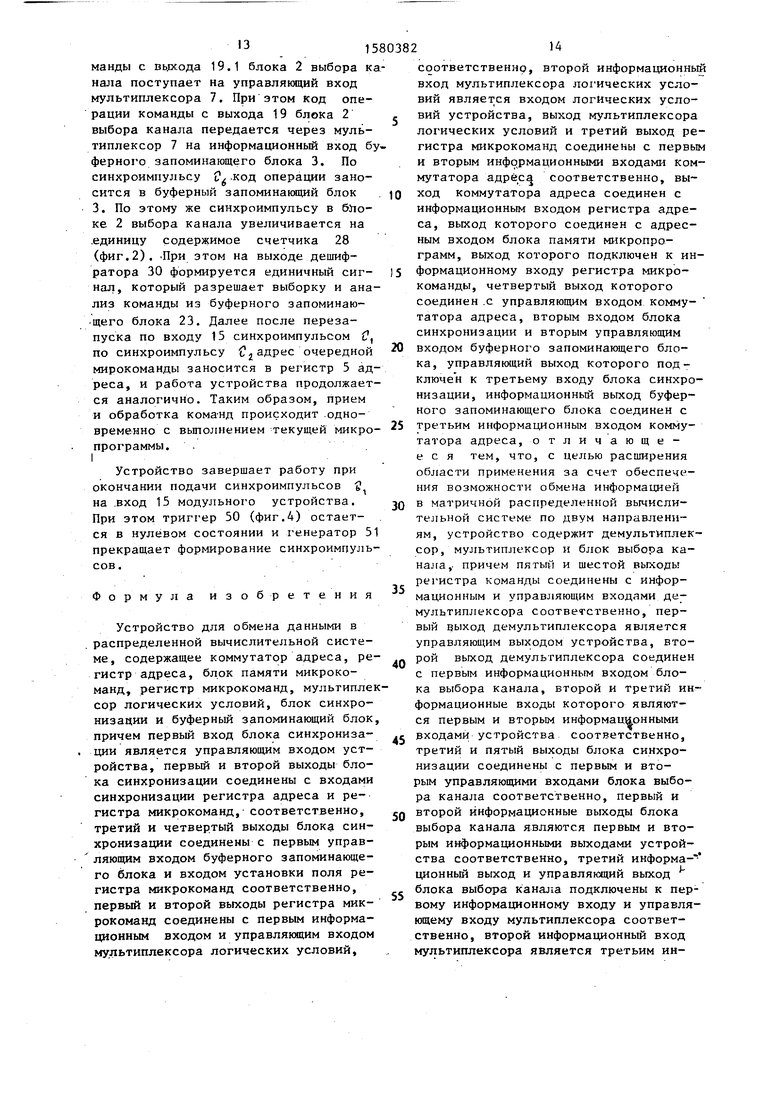

Каждому устройству, входящему в распределенную систему присваивается свой номер (идентификатор). Устройства, образующие систему, объединяются в двойную кольцевую систему по строке устройств системы и по столбцу устройств системы. Данная организация взаимодействия отдельных

Q

5

0 5

0

0

5

0

5

устройств системы позволяет организовать полный обмен между устройствами.

Нанокоманда передачи управления с ij-ro устройства (i 1,го, j 1,п, где тип- соответственно число устройств в матрице по горизонтали и вертикали) поступает на (i+1)j-e устройство, которое определяет, ему ли предназначена информация. Определение принадлежности информации происходит путем сравнения кода устройства - приемника информации в нано- команде передачи управления с кодом - идентификатором устройства. При несовпадении этих кодов поступившая информация отправляется по горизонтали к (i+2)j-My устройству и так далее до совпадения кодов по горизонтали. При совпадении горизонтальных кодов информация отправляется по вертикальному кольцу до совпадения кодов.

При совпадении кодов и по горизонтали и по вертикали информация о номере микропрограммы заносится в буферный запоминающий блок. В данный блок может заноситься управляющая информация как от устройств системы, так и от супервизорного блока (например, центрального процессора). Обработка информации из буферного запоминающего блока осуществляется по , правилу: первым пришел - первым обслужен (организация типа F1FO).

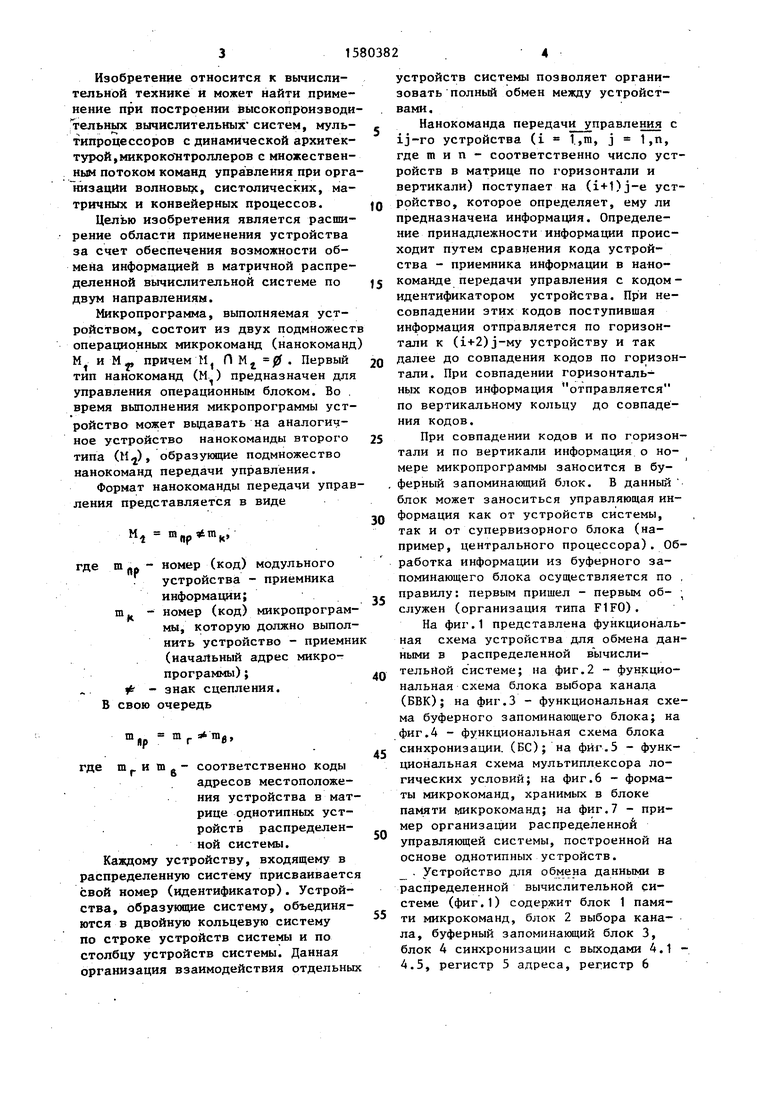

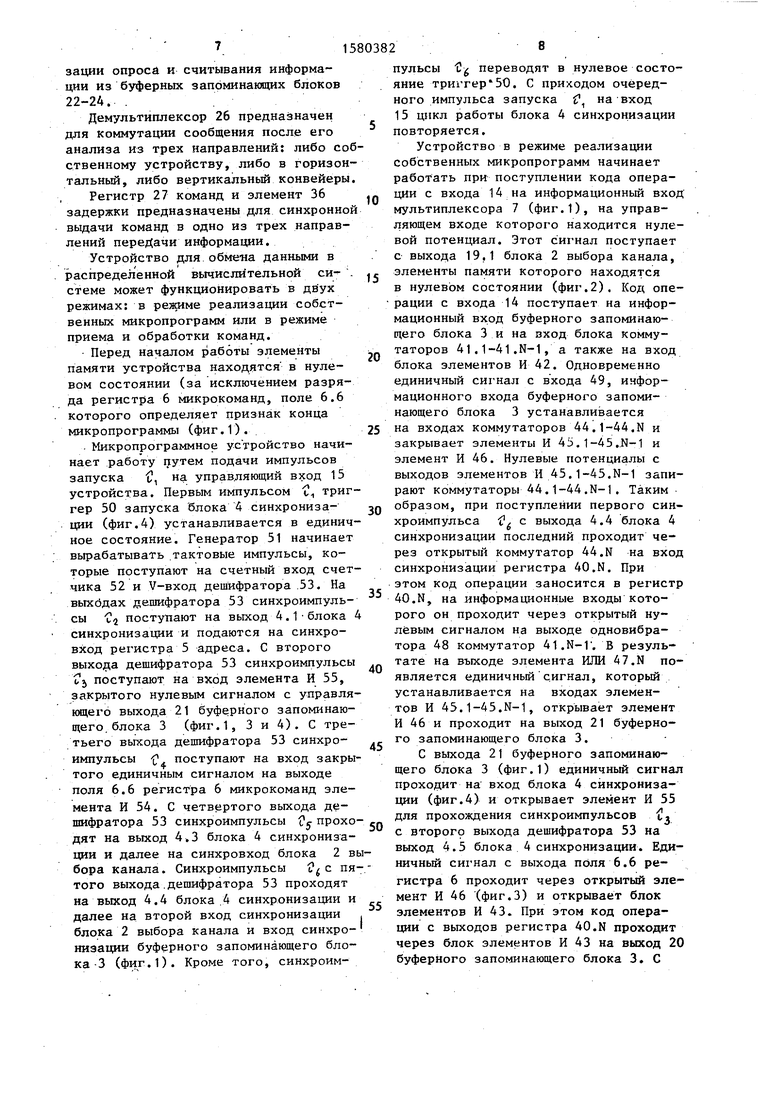

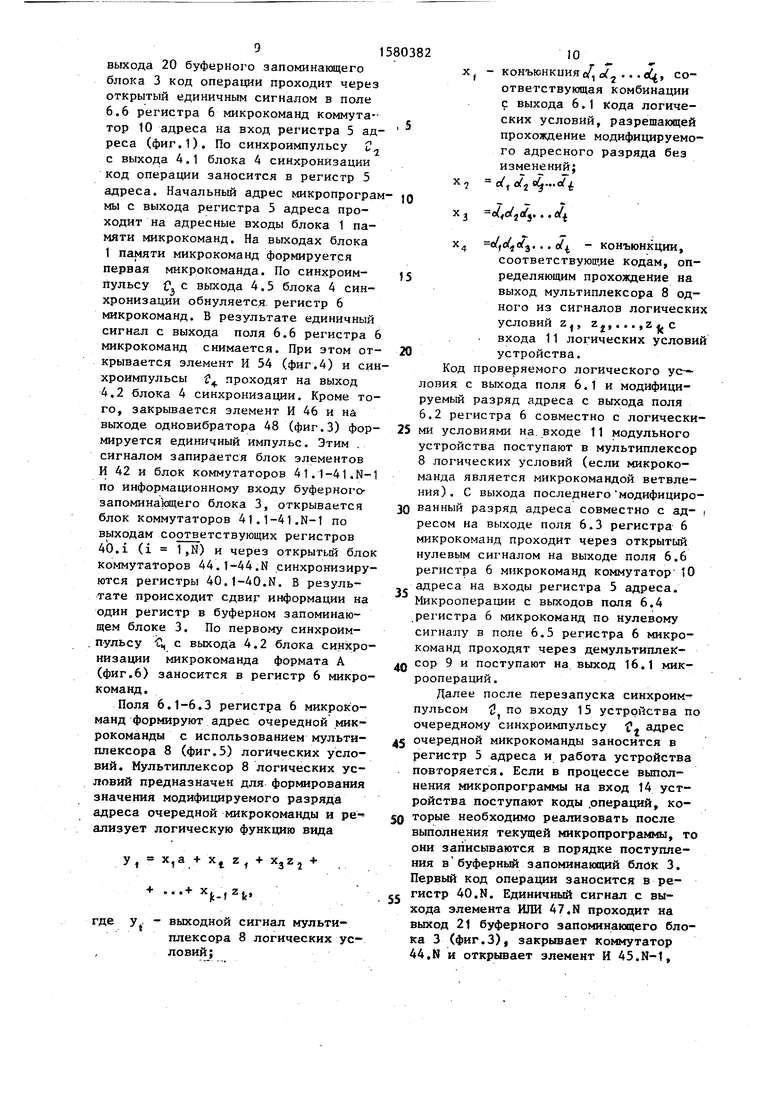

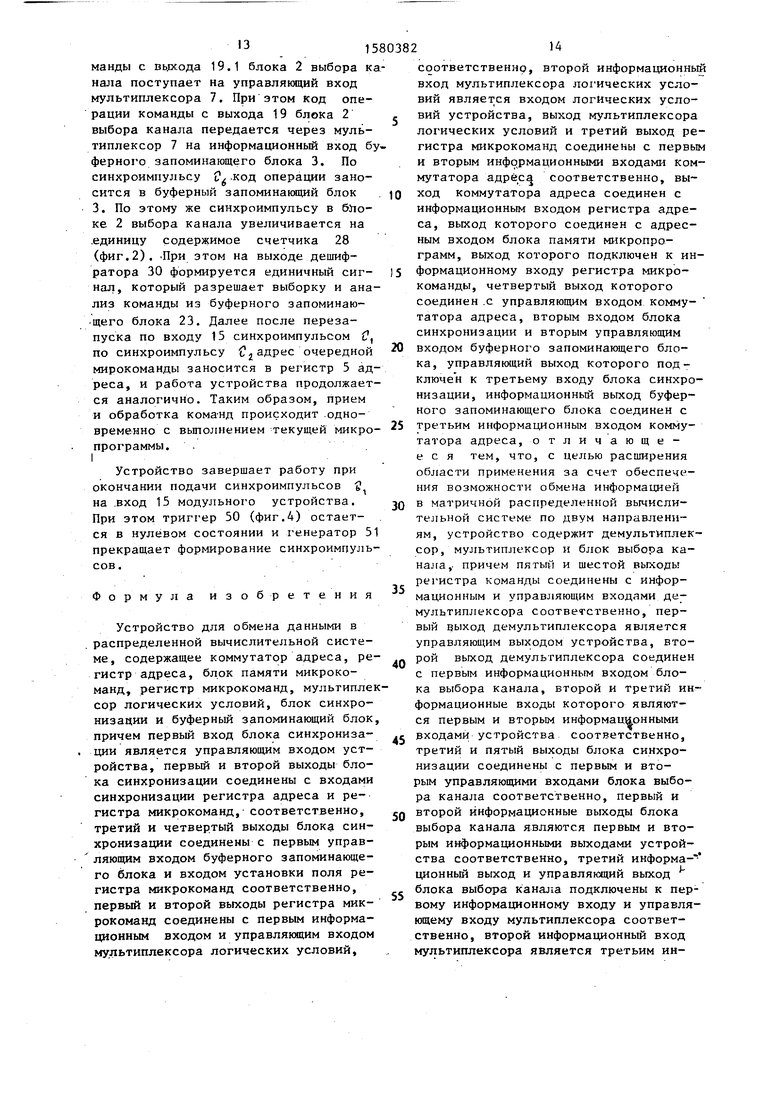

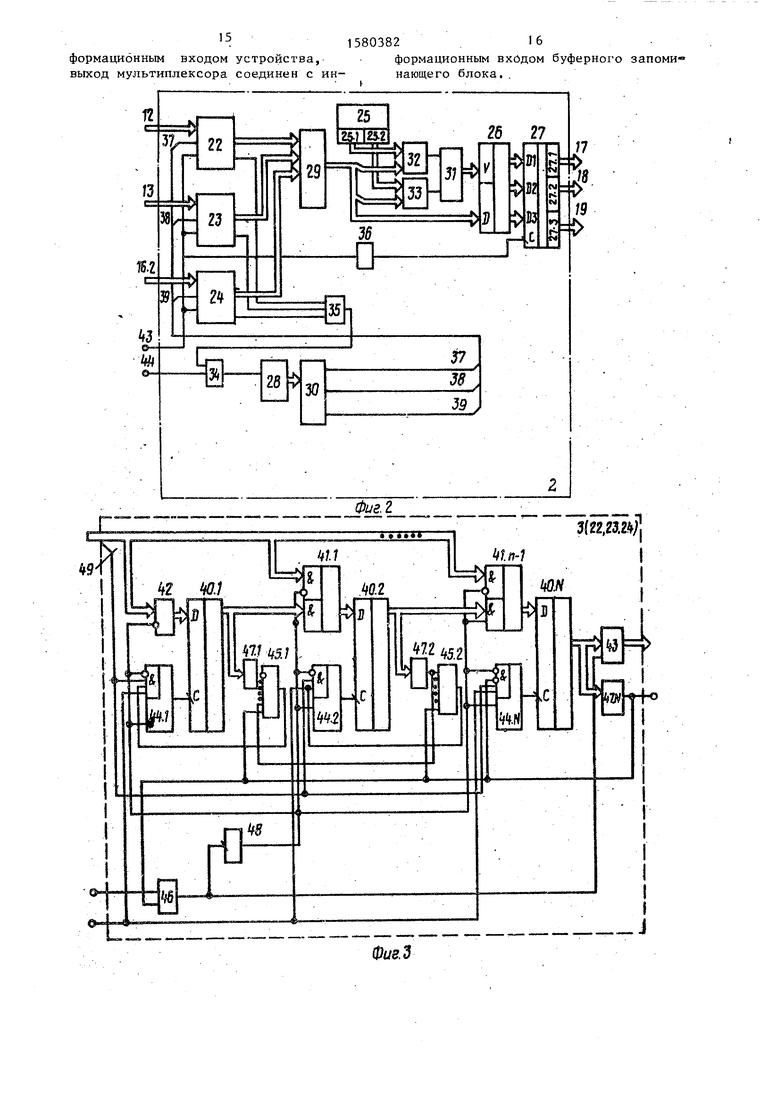

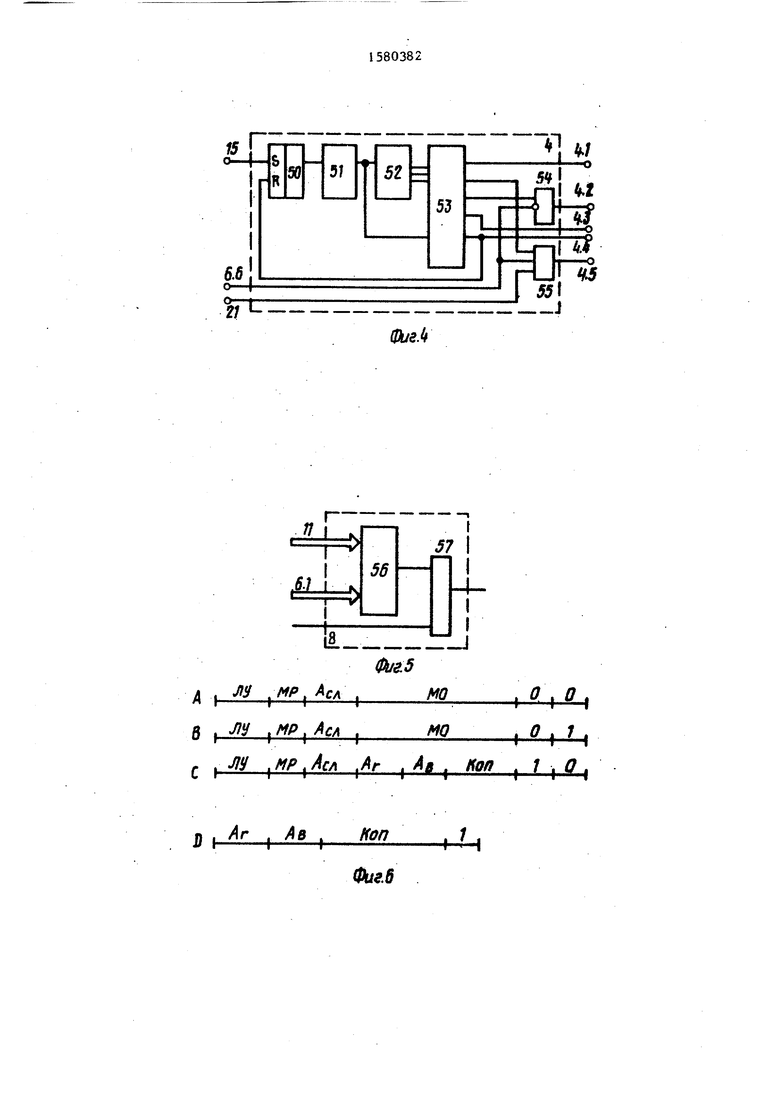

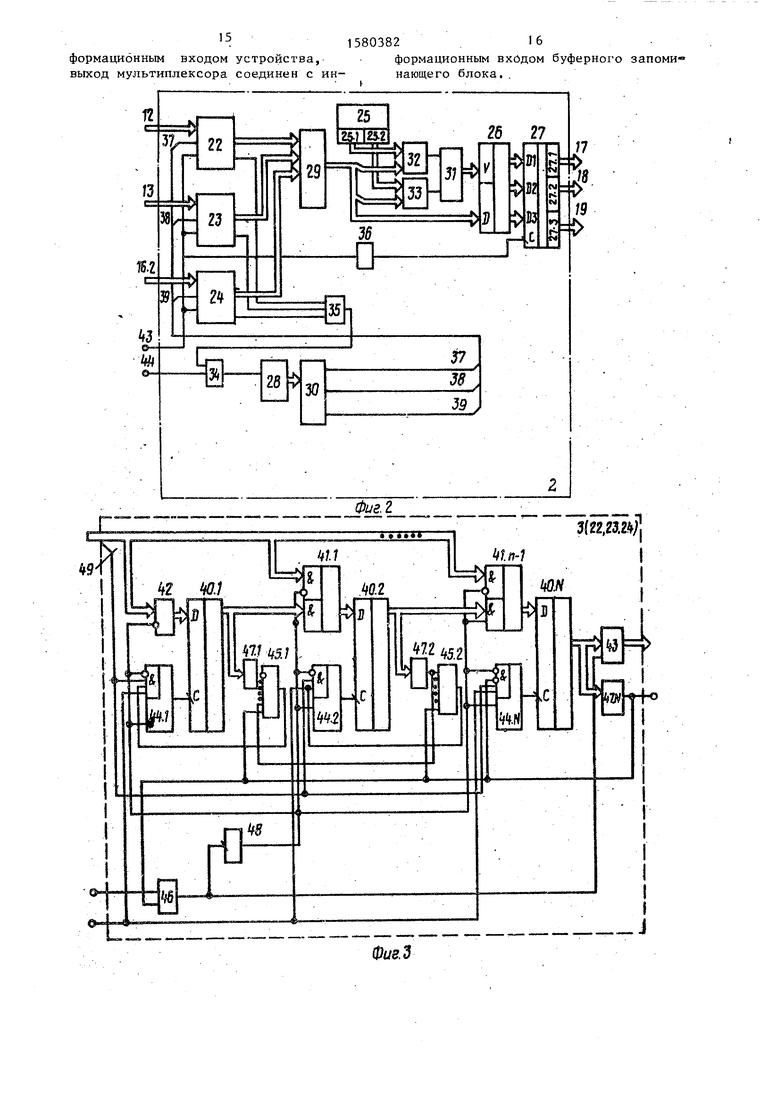

На фиг.1 представлена функциональная схема устройства для обмена данными в распределенной вычислительной системе; на фиг.2 - функциональная схема блока выбора канала (БВК); на фиг.З - функциональная схема буферного запоминающего блока; на фиг.4 - функциональная схема блока синхронизации. (БС); на фиг.З - функциональная схема мультиплексора логических условий; на фиг.6 - форматы микрокоманд, хранимых в блоке памяти микрокоманд; на фиг.7 - пример организации распределенной управляющей системы, построенной на основе однотипных устройств. . Устройство для обмена данными в распределенной вычислительной системе (фиг.1) содержит блок 1 памяти микрокоманд, блок 2 выбора канала, буферный запоминающий блок 3, блок 4 синхронизации с выходами 4.1 - 4.5, регистр 5 адреса, регистр 6

микрокоманд с полями кода проверяемого логического условия 6.1, модифицируемого разряда адреса 6.2с полем немодифицируемых разрядов адреса 6.3, операционным полем 6.4, также с полями признака передачи управления 6.5 и признака конца микропрограммы 6.6, мультиплексор 7, мультиплексор 8 логических условий, демуль- типлексор 9, коммутатор 10 адреса, вход логических условий 11 устройства, первый 12, второй 13 и третий 14 информационные входы устройства, управляющий вход 15 устройства, операционный выход 16.1 устройства, второй выход 16.2 демультиплек- сора, первый 17 и второй 18 информационные выходы устройства.

Кроме того, устройство содержит (фиг.1) третий информационный 19 и управляющий 19.1 выходы блока 2 выбора канала, информационный 20 и управляющий 21 выходы буферного запоминающего блока.

Блок 2 выбора канала (фиг.2) содержит первый 22, второй 23 и третий

24буферные запоминающие блоки, блок

25памяти константы с полями 25.1 и 25.2, определяющими составной код местоположения устройства для обмена данными в распределенной системе по горизонтали и вертикали, де мультиплексор 26, регистр 27 команд, счетчик 28, блок 29 элементов ИЛИ, первый 30 и второй 31 дешифраторы,

первую 32 и вторую 33 схемы сравнения, элемент И 34, элемент ИЛИ 35 и элемент 36 задержки. Кроме того,устройство содержит (фиг.2) управляющие входы 37-39 соответствующих буферных запоминающих блоков 22-24.

Буферный запоминающий блок 3 и первый-третий буферные запоминающие блоки блока 2 выбора канала (фиг.З) содержат блок регистров 40.1-40.N (где N - глубина очереди), блок информационных коммутаторов 41.1-41.N- -1, первый 42 и второй И 43 блоки элементов, блок синхронизирующих коммутаторов 44.1-44.N, третий блок элементов И 45.1-45.N-1, элемент И 46, блок элементов ИЛИ 47.1-47.N,- одно- вибратор 48 и синхронизирующий вход 49

Блок 4 синхронизации (фиг.4) содержит триггер 50 запуска, генератор 51 тактовых импульсов, счетчик 52, дешифратор 53, первый 54 и второй 55 элементы И,

0

5

0

5

0

5

0

5

0

5

Мультиплексор 8 логических условий (фиг.5) содержит мультиплексор 56 и элемент ИЛИ 57.

Назначение основных блоков и эле-i ментов устройства заключается в следующем .

Блок 1 памяти микрокоманд предназначен для хранения множества микрокоманд М М ЛМ2. ч

Блок 2 выбора канала предназначен для анализа поступившей информации с целью определения направления дальнейшей передачи в одном из трех направлений: на обработку данному устройству, для транзитной передачи в кольце устройств передачи по горизонтали, для транзитной передачи в кольце устройств по вертикали.

Буферный запоминающий блок 3 предназначен для хранения кодов (номеров) микропрограмм, поступивших для обслуживания данным устройством.

Блок 4 синхронизации предназначен для синхронизации работы устройства.

Мультиплексор 7 предназначен для коммутации поступивших на обслуживание запросов от супервизорного устройства или от одного чиз двух направлений (горизонтального или вертикального) .

Демулътиплексор 9 предназначен для коммутации нанокоманды для управления операционным блоком и для выдачи нанокоманды передачл управления.

Назначение основных элементов блока выбора канала (фиг.2) заключается в следующем.

Первый-третий буферные запоминающие блоки 22-24 предназначены для временного хранения поступивших для - анализа сообщений от собственного устройства и от соседних слева и снизу модульных устройств матрицы, образующих соответственно горизонтальный и вертикальный конвейеры (фиг.7).

Блок 25 памяти константы предназначен для хранения кода, идентифицирующего местоположение устройства в матрице устройств для обмена данными в распределенной вычислительной системе.

Блок элементов ИЛИ 29 предназначен для хранения передачи хранимых в блоках 22-24 сообщений для их анализа принадлежности информации на первой 32 и второй 33 схемах сравнения.

Счетчик 28, дешифратор 30 и элемент И 34 предназначены для организации опроса и считывания информации из буферных запоминающих блоков 22-24.

Демультиплексор 26 предназначен для коммутации сообщения после его анализа из трех направлений: либо собственному устройству, либо в горизонтальный, либо вертикальный конвейеры.

Регистр 27 команд и элемент 36 задержки предназначены для синхронной выдачи команд в одно из трех направлений передачи информации.

Устройство для обмена данными в распределенной вычислительной системе может функционировать в двух режимах: в режиме реализации собственных микропрограмм или в режиме приема и обработки команд.

Перед началом работы элементы памяти устройства находятся в нулевом состоянии (за исключением разряда регистра 6 микрокоманд, поле 6.6 которого определяет признак конца микропрограммы (фиг.1).

Микропрограммное устройство начинает работу путем подачи импульсов запуска ц на управляющий вход 15 устройства. Первым импульсом С., триггер 50 запуска блока 4 синхронизации (фиг.4) устанавливается в единичное состояние. Генератор 51 начинает вырабатывать тактовые импульсы, которые поступают на счетный вход счетчика 52 и V-вход дешифратора 53. На выхбдах дешифратора 53 синхроимпульсы 2 поступают на выход 4.1 блока 4 синхронизации и подаются на синхро- вход регистра 5 адреса. С второго выхода дешифратора 53 синхроимпульсы Cj поступают на вход элемента И 55, закрытого нулевым сигналом с управляющего выхода 21 буферного запоминающего блока 3 (фиг.1, 3 и 4). С третьего выхода дешифратора 53 синхроимпульсы Ј поступают на вход закрытого единичным сигналом на выходе поля 6.6 регистра 6 микрокоманд элемента И 54. С четвертого выхода дешифратора 53 синхроимпульсы проходят на выход 4.3 блока 4 синхронизации и далее на синхровход блока 2 выбора канала. Синхроимпульсы Јс пятого выхода дешифратора 53 проходят на выход 4.4 блока 4 синхронизации и далее на второй вход синхронизации блока 2 выбора канала и вход синхронизации буферного запоминающего блока 3 (фиг.1). Кроме того, синхроим

0

5

0

5

0

5

0

5

0

5

пульсы U переводят в нулевое состояние триггер 50. С приходом очередного импульса запуска С , на вход 15 цикл работы блока 4 синхронизации повторяется.

Устройство в режиме реализации собственных микропрограмм начинает работать при поступлении кода операции с входа 14 на информационный вход мультиплексора 7 (фиг.1), на управляющем входе которого находится нулевой потенциал. Этот сигнал поступает с выхода 19.1 блока 2 выбора канала, элементы памяти которого находятся в нулевом состоянии (фиг.2). Код операции с входа 14 поступает на информационный вход буферного запоминающего блока 3 и на вход блока коммутаторов 41.1-41.N-1, а также на вход блока элементов И 42. Одновременно единичный сигнал с входа 49, информационного входа буферного запоминающего блока 3 устанавливается на входах коммутаторов 44.1-44.N и закрывает элементы И 4j.1-45.N-1 и элемент И 46. Нулевые потенциалы с выходов элементов И 45.1-45.N-1 запирают коммутаторы 44.1-44.N-1. Таким образом, при поступлении первого синхроимпульса

& с выхода 4.4 блока 4 синхронизации последний проходит через открытый коммутатор 44.N на вход синхронизации регистра 40.N. При этом код операции заносится в регистр 40.N, на информационные входы которого он проходит через открытый нулевым сигналом на выходе одновибра- тора 48 коммутатор 41.N-1. В результате на выходе элемента ИЛИ 47.N появляется единичный сигнал, который устанавливается на входах элементов И 45.1-45.N-1, открывает элемент И 46 и проходит на выход 21 буферного запоминающего блока 3.

С выхода 21 буферного запоминающего блока 3 (фиг.1) единичный сигнал проходит на вход блока 4 синхронизации (фиг.4) и открывает элемент И 55 для прохождения синхроимпульсов . с второго выхода дешифратора 53 на выход 4.5 блока 4 синхронизации. Единичный сигнал с выхода поля 6.6 регистра 6 проходит через открытый элемент И 46 (фиг.З) и открывает блок элементов И 43 При этом код операции с выходов регистра 40.N проходит через блок элементов И 43 на выход 20 буферного запоминающего блока 3. С

91

выхода 20 буферного запоминающего блока 3 код операции проходит через открытый единичным сигналом в поле 6.6 регистра 6 микрокоманд коммутатор 10 адреса на вход регистра 5 ад- реса (фиг.1). По синхроимпульсу Ј с выхода 4.1 блока 4 синхронизации код операции заносится в регистр 5 адреса. Начальный адрес микропрограм мы с выхода регистра 5 адреса проходит на адресные входы блока 1 памяти микрокоманд. На выходах блока 1 памяти микрокоманд формируется первая микрокоманда. По синхроимпульсу Ј с выхода 4.5 блока 4 синхронизации обнуляется регистр 6 микрокоманд. В результате единичный сигнал с выхода поля 6.6 регистра 6 микрокоманд снимается. При этом открывается элемент И 54 (фиг.4) и синхроимпульсы Ј+ проходят на выход 4.2 блока 4 синхронизации. Кроме то

го, закрывается элемент И 46 и на выходе одновибратора 48 (фиг.З) формируется единичный импульс. Этим сигналом запирается блок элементов И 42 и блок коммутаторов 4t.1-41.N-1 по информационному входу буферного- запоминающего блока 3, открывается блок коммутаторов 41.1-41.N-1 по выходам соответствующих регистров 40.i (i 1,N) и через открытый блок коммутаторов 44.1-44.N синхронизируются регистры 40.1-40.N. В результате происходит сдвиг информации на один регистр в буферном запоминающем блоке 3. По первому синхроимпульсу Сн с выхода 4.2 блока синхронизации микрокоманда формата А (фиг.6) заносится в регистр 6 микрокоманд.

Поля 6.1-6.3 регистра 6 микрокоманд формируют адрес очередной микрокоманды с использованием мультиплексора 8 (фиг.5) логических условий. Мультиплексор 8 логических условий предназначен для формирования значения модифицируемого разряда адреса очередной микрокоманды и ре апизует логическую функцию вида

У|

xt a +

xt zf + x3z2 +

+ ...+

xMzfc

где

- выходной сигнал мультиплексора 8 логических условий ;

10

- КОНЪЮНКЦИЯ

«и

соответствующая комбинации с выхода 6.1 кода логических условий, разрешающей прохождение модифицируемого адресного разряда без изменений;

«л

X j -e OjOfj. . . «i

Q

5

0

. .. /t - конъюнкции, соответствующие кодам, определяющим прохождение на выход мультиплексора 8 одного из сигналов логических

УСЛОВИЙ Zj, Z2,...,

входа 11 логических условий устройства.

Код проверяемого логического ус- ловия с выхода поля 6.1 и модифицируемый разряд адреса с выхода поля 6.2 регистра 6 совместно с логически5 ми условиями на входе 11 модульного устройства поступают в мультиплексор 8 логических условий (если микрокоманда является микрокомандой ветвления) . С выхода последнего модифициро0 ванный разряд адреса совместно с ад- i ресом на выходе поля 6.3 регистра 6 микрокоманд проходит через открытый нулевым сигналом на выходе поля 6.6 регистра 6 микрокоманд коммутатор Ю адреса на входы регистра 5 адреса. Микрооперации с выходов поля 6.4 регистра 6 микрокоманд по нулевому сигналу в поле 6.5 регистра 6 микрокоманд проходят через демультиплеКл сор 9 и поступают на выход 16.1 микроопераций.

Далее после перезапуска синхроим- Q по входу 15 устройства по

пульсом

очередному синхроимпульсу

адрес

очередной микрокоманды заносится в регистр 5 адреса и работа устройства повторяется. Если в процессе выполнения микропрограммы на вход 14 устройства поступают коды операций, которые необходимо реализовать после выполнения текущей микропрограммы, то они записываются в порядке поступления в буферный запоминающий блок 3. Первый код операции заносится в регистр 40.N. Единичный сигнал с выхода элемента ИЛИ 47.N проходит на выход 21 буферного запоминающего блока 3 (фиг.З), закрывает коммутатор 44.N и открывает элемент И 45.N-1,

11

1580382

на выходе которого формируется единичный сигнал. Этот сигнал открывает коммутатор 44.N-1.

При поступлении очередного кода операции на вход буферного запоминающего блока 3 по синхроимпульсу %& последний заносится в регистр 40.N-1 Остальные регистры буферного запоминающего блока 3 заполняются аналогично. Запись в регистр 40.1 происходит при наличии единичных сигналов со всех элементов ИЛИ 47.1+1 - 47.N на входе элемента И 45.1 и нулевого сигнала на выходе элемента ИЛИ 47.1. По окончании реализации микропрограммы в регистр 6 микрокоманд заносится микрокоманда формата В (фиг.6). Единичный сигнал с выхода поля 6.6 регистра 6 микрокоманд переключает коммутатор 10 адреса на прием кода операции из буферного запоминающего блока 3, поступает на вход блока 4 синхронизации, запрещая формирование синхроимпульсов {. на выходе 4.2 блока 4 синхронизации, и подается на вход считывания буферного запоминающего блока 3. При этом на информационном выходе 20 буферного запоминающего блока 3 формируется очередной код операции, который проходит через коммутатор 10 адреса на вход регистра 5 адреса. По очередному синхроимпульсу Сг на выходе 4.1 блока 4 синхронизации код операции заносится в регистр 5 адреса -и работа устройства продолжается аналогично.

Режим приема и обработки команд реализуется в модульном устройстве при поступлении команд формата Д на входы 12 и 13 устройства и при запис в регистр 6 микрокоманд микрокоманды формата С (фиг.6). В последнем случае в поле 6.5 регистра 6 микрокоманд появляется единичный сигнал, который поступает на управляющий вхо демультиплексора 9. При этом команда формата Д с выходов поля 6.4 регистра 6 микрокоманд проходит через демультиплексор 9 на выход 16.2 поступает на одноименный вход бло- ,ка 2 выбора канала. Команды формата Д с входов 12 и 13 поступают на одноименные входы блока 2 выбора каналов . По синхроимпульсу Су с выхода i4,3 блока 4 синхронизации команды с входов 12 и 13 и выхода 1J.2 демультиплексора 9 заносятся в соответствующие буферные запоминающие блоки

5

0

5

0

5

0

5

0

5

12

22-24 блока 2 выбора каналов (фиг.2). Устройство и функционирование буферных запоминающих блоков 22-24 аналогично буферному запоминающему блоку 3 (фиг.З). В результате, на управляющих выходах соответствующих блоков 22-24 появляются единичные сигналы, которые формируют на выходе элемента ИЛИ 3,5 единичный потенциал. Этот сигнал открывает элемент И 34. Одновременно в соответствии с нулевым кодом на выходе счетчика 28 единичный сигнал с выхода дешифратора 30 поступает на одноименный вход считывания буферного запоминающего блока 22. Команда с информационных выходов буферного запоминающего блока 22 проходит через блок элементов ИЛИ 29 и поступает на информационный вход демультиплексора 26. Кроме того, горизонтальная составляющая адреса команда формата Д (фиг.7) поступает на вход схемы 32 сравнения, на второй вход которой поступает горизонтальный адрес устройства с ыхода поля 25.1, блока 25 памяти константы.Вертикальная составляющая поступает на вход схемы 33 сравнения, на второй вход которой подается вертикальный адрес устройства с выхода блока 25 памяти константы. Если оба адреса на схемах 32 и 33 сравнения совпали, то по сигналам на выходе дешифратора 31 демультиплексор 26 передает подкоманды на вход регистра 27 команд. Затем по задержанному элементом 36 задержки синхроимпульсу О код команды заносится в поле регистра 27 команд. Если совпадение происходит только по схеме 32 сравнения, то по сигналам дешифратора 31 демультиплексор 26 передает код команды на вход регистра 27 команд, который заносится в поле регистра 27 команд. Если совпадение происходит только на схеме 33 сравнения, то команда заносится в поле регистра 27 команд. Если совпадения адресов на схемах 32 и 33 сравнения не происходит, то код команды заносится в поле регистра 27 команд. Далее коды команд с выходов полей регистра 27 команд , проходят на выходы 17 и 18 модуля соответственно. Коды команд с выхода, поля регистра 27 команд проходят на выход 19 блока 2 выбора начала и поступают на одноименный вход мультиплексора 7. Управляющий разряд команды с выхода 19.1 блока 2 выбора канала поступает на управляющий вход мультиплексора 7. При этом код операции команды с выхода 19 блока 2 выбора канала передается через мультиплексор 7 на информационный вход буферного запоминающего блока 3. По синхроимпульсу С1 .код операции заносится в буферный запоминающий блок 3. По этому же синхроимпульсу в блоке 2 выбора канала увеличивается на .единицу содержимое счетчика 28 (фиг.2). .При этом на выходе дешифратора 30 формируется единичный сигнал, который разрешает выборку и анализ команды из буферного запоминаю- щего блока 23. Далее после перезапуска по входу 15 синхроимпульсом о1, по синхроимпульсу С2адрес очередной мирокоманды заносится в регистр 5 адреса, и работа устройства продолжается аналогично. Таким образом, прием и обработка кома-нд происходит одновременно с выполнением текущей микропрограммы. I

Устройство завершает работу при окончании подачи синхроимпульсов Јг на вход 15 модульного устройства. При этом триггер 50 (фиг.4) остается в нулевом состоянии и генератор 51 прекращает формирование синхроимпульсов .

Формула изобретения

Устройство для обмена данными в распределенной вычислительной системе, содержащее коммутатор адреса, регистр адреса, блок памяти микрокоманд, регистр микрокоманд, мультиплексор логических условий, блок синхронизации и буферный запоминающий блок, причем первый вход блока синхронизации является управляющим входом устройства, первый и второй выходы блока синхронизации соединены с входами синхронизации регистра адреса и регистра микрокоманд, соответственно, третий и четвертый выходы блока синхронизации соединены с первым управ- ляющим входом буферного запоминающего блока и входом установки поля регистра микрокоманд соответственно, первый и второй выходы регистра микрокоманд соединены с первым информационным входом и управляющим входом мультиплексора логических условий,

5

0

5

0

5

0

5

0

5

соответственно, второй информационный вход мультиплексора логических условий является входом логических условий устройства, выход мультиплексора логических условий и третий выход регистра микрокоманд соединены с первым и вторым информационными входами коммутатора адресу соответственно, выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход которого подключен к информационному входу регистра микрокоманды, четвертый выход которого соединен с управляющим входом коммутатора адреса, вторым входом блока синхронизации и вторым управляющим входом буферного запоминающего блока, управляющий выход которого подключен к третьему входу блока синхронизации, информационный выход буферного запоминающего блока соединен с третьим информационным входом коммутатора адреса, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности обмена информацией в матричной распределенной вычислительной системе по двум направлениям, устройство содержит демультиплек- сор, мультиплексор и блок выбора канала, причем пятый и шестой выходы регистра команды соединены с информационным и управляющим входами де- мультиплексора соответственно, первый выход демультиплексора является управляющим выходом устройства, второй выход демульгиплексора соединен с первым информационным входом блока выбора канала, второй и третий информационные входы которого являются первым и вторым информационными входами устройства соответственно, третий и пятый выходы блока синхронизации соединены с первым и вторым управляющими входами блока выбора канала соответственно, первый и второй информационные выходы блока выбора канала являются первым и вторым информационными выходами устройства соответственно, третий информа- ционный выход и управляющий выход блока выбора канала подключены к первому информационному входу и управляющему входу мультиплексора соответственно, второй информационный вход мультиплексора является третьим ин12

| название | год | авторы | номер документа |

|---|---|---|---|

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

Изобретение относится к вычислительной технике и может найти применение при построении высокопроизводительных вычислительных систем, векторных, матричных и конвейерных процессоров. Цель изобретения - расширение области применения за счет обеспечения возможности обмена информацией в матричной распределенной вычислительной системе по двум направлениям. Для этого в устройство дополнительно введены блок 2 выбора канала, мультиплексор 7 и демультиплексор 9. Введение указанных элементов и порожденных ими связей позволяет организовать вертикальный и горизонтальный конвейеры в матричной вычислительной системе, что в сочетании с циклической организацией данных конвейеров позволяет обеспечить эффективный, в смысле аппаратурных затрат, обмен данными между всеми элементами матричной вычислительной системы. 7 ил.

I

Фиг. 7

Вертикальный конвейер

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-06-06—Подача