Изобретение относится к вычислительной технике и может быть использовано в системах считывания цифровой информации в виде конечного числа кодов.

Цель изобретения - упрощение устройства при считывании информации с подвижных кодированных объектов за счет обнаружения незадействованного кода или повторного приема одного и того же кода и блокировки их прохождения.

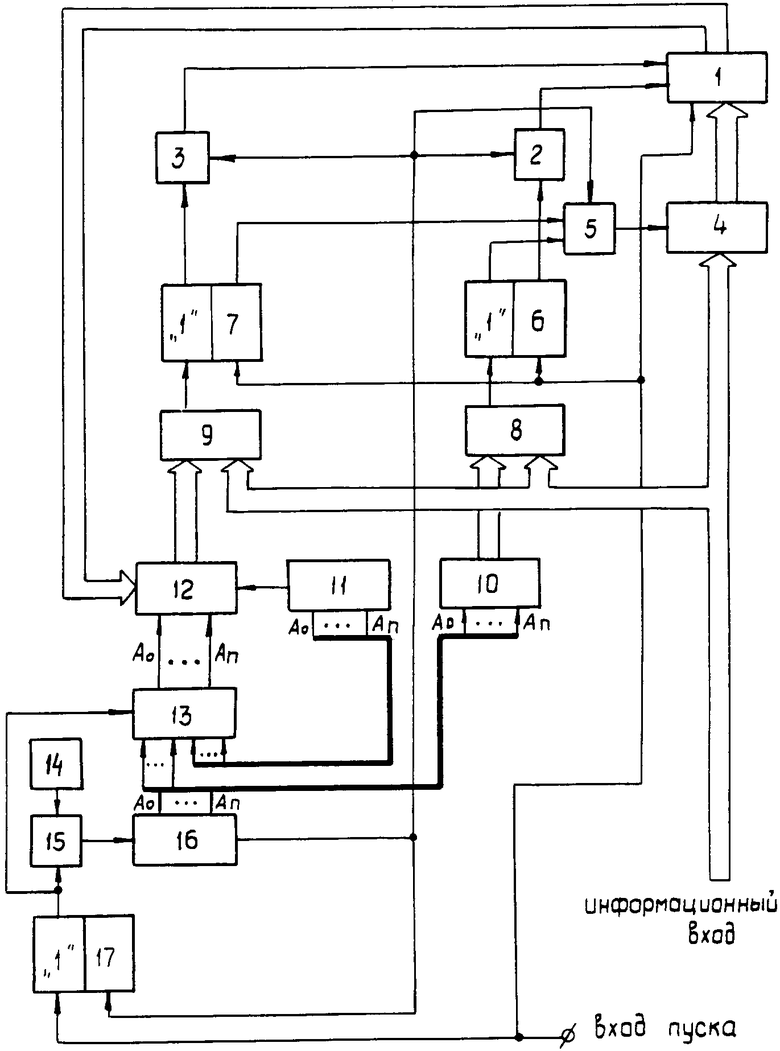

Блок-схема устройства приведена на чертеже.

Устройство содержит блок 1 индикации информации, третий элемент И 2, четвертый элемент И 3, блок 4 ключей, второй элемент И 5, первый триггер 6, второй триггер 6, первый элемент 8 равнозначности, второй элемент 9 равнозначности, блок 10 перепрограммируемой памяти, второй генератор 11 импульсов, блок 12 оперативной памяти, коммутатор 13, первый генератор 14 импульсов, первый элемент И 15, счетчик 16 импульсов, третий триггер 17.

Информационный вход устройства подключен к информационным входам блока 4 ключей и первым группам входов первого 8 и второго 9 элементов равнозначности.

Вход пуска устройства подключен к входу начальной установки блока 1 индикации информации, входам обнуления первого 6 и второго 7 триггеров и установочному входу третьего триггера 17.

Выход первого генератора 14 импульсов подключен к первому входу первого элемента И 15, второй вход которого и управляющий вход коммутатора 13 подключены к прямому выходу третьего триггера 17, а выход - к входу счетчика 16 импульсов, разрядные выходы которого подключены к входам блока 10 перепрограммируемой памяти и первой группе информационных входов коммутатора 13, а выход переполнения - к входу обнуления третьего триггера 17, третьему входу второго элемента И 5 и вторым входам третьего и четвертого элементов И 2 и И 3. Выходы третьего и четвертого элементов И 2 и И 3 соединены с первым и вторым управляющими входами блока 1 индикации информации, информационные входы соединены с выходами блока 4 ключей, а выходы - с информационными входами блока 12 оперативной памяти. Тактовый выход второго генератора 11 импульсов соединен с тактовым входом блока 12 оперативной памяти, а адресные выходы - с второй группой информационных входов коммутатора 13, выходами подключенного к адресным входам блока 12 оперативной памяти, разрядные выходы которого подключены к второй группе входов второго элемента 9 равнозначности, а вторая группа входов первого элемента 8 равнозначности подключена к выходам блока 10 перепрограммируемой памяти. Выход первого элемента 8 равнозначности подключен к установочному входу первого триггера 6, прямой выход которого подключен к первому входу второго элемента И 5, а инверсный выход - к первому входу третьего элемента И 2. Выход второго элемента 9 равнозначности подключен к установочному входу второго триггера 7, прямой выход которого подключен к первому входу четвертого элемента И 3, а инверсный выход - к второму входу второго элемента И 5, выходом подключенного к управляющему входу блока 4 ключей.

Реализация устройства основана на проверке достоверности считанного кода для конечного числа подвижных кодированных объектов с задействованными (известными) кодами, например, в производственной системе.

Считанный с кодированного объекта и поступающий на вход устройства код должен, во-первых, присутствовать в составе задействованных кодов подвижных кодированных объектов и, во-вторых, среди считываемых кодов один и тот же не должен повторяться. Достоверный код, поступающий на информационный вход устройства, передается через блок 1 индикации информации в блок 12 оперативной памяти, но при выявлении ошибки его передача не производится, а формируется и передается в блок 1 индикации информации сообщение об ошибке. Таким образом, в блоке 12 оперативной памяти хранятся считываемые с подвижных кодированных объектов реальные коды, а в блок 10 перепрограммируемой памяти при реализации устройства записываются коды всех задействованных в системе подвижных кодированных объектов.

Количество адресов блока 10 перепрограммируемой памяти должно быть не менее количества задействованных подвижных кодированных объектов. Количество адресов блока 12 оперативной памяти должно быть не менее количества задействованных считывателей кодов, к которым стыкуются подвижные кодированные объекты. Количество разрядов счетчика 16 импульсов должно быть не менее максимального количества адресов блока 12 оперативной памяти и блока 10 перепрограммируемой памяти.

Поскольку количество подвижных кодированных объектов в системе всегда меньше количества считывателей кодов, то количество разрядов счетчика 16 импульсов должно быть не менее количества адресов блока 12 оперативной памяти.

Число блоков 1 индикации информации устанавливается по числу позиций считывания кодов подвижных кодированных объектов.

На чертеже показано подключение одного блока 1 индикации информации. Остальные подключаются параллельно показанному.

Элементы 2. ..9 реализуются для каждого блока индикации (т.е. по числу позиций считывания кодов).

Элементы 10...17 реализуются в единственном экземпляре.

Устройство работает следующим образом.

Считанный с подвижного кодированного объекта код через информационные входы устройства поступает на информационные входы блока 4 ключей и первые группы входов первого и второго элементов 8 и 9 равнозначности.

Запуск устройства для контроля поступившего кода осуществляется импульсом, поступающим на вход пуска устройства (например, с устройства считывания кода). Этот импульс поступает на вход начальной установки блока 1 индикации информации для подготовки к приему информации, на входы обнуления первого 6 и второго 7 триггеров, устанавливая их в нулевое состояние, и на установочный вход третьего триггера 7, устанавливая его в единицу. Высоким потенциалом с прямого выхода триггер 17 переключает коммутатор 13 на передачу адресов с разрядных выходов счетчика 16 импульсов и открывает первый элемент И 15 для прохождения на вход счетчика 16 импульсов с выхода первого генератора 14 импульсов.

В процессе работы счетчика 16 с его разрядных выходов Ао...Аn снимаются последовательные адреса опросов блоков памяти, которые поступают на входы блока 10 перепрограммируемой памяти и через коммутатор 13 - на адресные входы блока 12 оперативной памяти. В результате этого последовательного опроса с выхода блока 10 перепрограммируемой памяти на вторую группу входов первого элемента 8 равнозначности последовательно поступают запрограммированные при реализации устройства коды задействованных подвижных кодированных объектов, а с разрядных выходов блока 12 оперативной памяти на вторую группу входов второго элемента 9 равнозначности последовательно синхронно поступают коды подвижных кодированных объектов, подключенных в этот момент времени ко всем считывателям кодов системы.

Таким образом, в первом элементе 8 равнозначности осуществляется последовательное сравнение поступившего на информационные входы устройства кода с кодами всех задействованных в системе подвижных кодированных объектов. Поступивший в устройство код должен совпадать с одним из записанных в блоке 10 перепрограммируемой памяти кодов. Если такое совпадение есть, то сигналом с выхода первого элемента 8 равнозначности первый триггер 6 устанавливается в единичное состояние, подготавливая второй элемент И 5. Если результат проверки неудовлетворительный (поступившего кода нет в заданном составе), то триггер 6 остается в нулевом состоянии, подготавливая третий элемент И 2.

Во втором элементе 9 равнозначности осуществляется последовательное сравнение поступившего на информационные входы устройства кода со всеми считанными ранее кодами других (пристыкованных к считывателям кодов) подвижных кодированных объектов. Поступивший код не должен совпадать ни с одним из записанных в блоке 12 оперативной памяти кодов. Если это условие выполняется, то в результате сравнения сигнала на выходе элемента 9 равнозначности не появляется, триггер 7 остается в нулевом состоянии, высоким потенциалом с инверсного выхода подготавливая второй элемент И 5.

При неудовлетворительном результате проверки (в считанных с другим подвижных кодированных объектов уже есть такой код), при совпадении кодов на выходе второго элемента 9 равнозначности появляется сигнал, устанавливающий триггер 7 в единичное состояние, а высоким потенциалом с прямого выхода триггера 7 подготавливается четвертый элемент И 3.

По окончании опроса блоков 10 и 12 памяти импульсом переполнения счетчика 16 импульсов третий триггер 17 устанавливается в нулевое состояние, перекрывая через первый элемент И 15 вход счетчика 16 импульсов и переключая коммутатор 13 на передачу адресов с второго генератора 11 импульсов для последующей организации периодических сеансов опроса кодов, записанных в блоке 1 индикации информации. Этот же импульс переполнения поступает на элементы И 2,3,5.

Если результат проверки поступившего кода положительный (этот код имеется в составе задействованных, записанных в блоке 10 перепрограммируемой памяти, и отсутствует в составе считанных ранее кодов, записанных в блоке 12 оперативной памяти), то высокими потенциалами с прямого выхода первого триггера 6 и инверсного выхода триггера 7 подготовлен второй элемент И 5 и импульс переполнения счетчика 16, пройдя через элемент И 9 на управляющий вход блока 4 ключей, осуществляет передачу считанного кода в блок 1 индикации информации.

При отрицательном результате проверки либо первый триггер 6 остается в нулевом состоянии, если поступившего кода нет в составе задействованных, либо второй триггер 7 устанавливается в единичное состояние, если поступивший код повторяет один из считанных ранее, либо обнаружены сразу обо несоответствия. В любом из этих случаев второй элемент И 5 закрыт и разрешающего сигнала в блок 4 ключей для прохождения поступившего кода в блок 1 индикации информации не поступает. При этом либо высоким потенциалом с инверсного выхода первого триггера 6 оказывается подготовленным третий элемент И 2, либо высоким потенциалом с прямого выхода второго триггера 7 оказывается подготовлен четвертый элемент И 3, либо оба вместе, в результате чего импульс переполнения счетчика 16 импульсов проходит на блок 1 индикации информации для фиксации ошибки.

Передача из блока 1 индикации информации записанных там кодов в блок 12 оперативной памяти осуществляется периодическим опросом блоков 1 в соответствии с адресами, формируемыми вторым генератором 11 импульсов и поступающими в блок 12 оперативной памяти через коммутатор. Канал команды опроса, поступающей в блок 1 индикации информации, на чертеже не показан. В ответ на запрос записанный в блоке 1 индикации информации код передается через информационные входы в блок 12 оперативной памяти и записывается по заданному адресу (адресу опрашиваемого блока 1).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1357998A1 |

Изобретение относится к вычислительной технике. Использование изобретения в системах считывания информации, представленной конечным числом кодов, позволяет упростить устройство при считывании информации с подвижных кодированных объектов. Устройство содержит блок ключей, элементы И, триггер, блок оперативной памяти, генератор импульсов и счетчик импульсов. Благодаря введению блока индикации информации, элементов И, триггеров, элементов равнозначности, блока перепрограммируемой памяти, генератора импульсов и коммутатора в устройстве обеспечивается обнаружение незадействованного кода или повторный прием одного и того же кода с блокировкой их прохождения. 1 ил.

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК, содержащее первый генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого подключен к входу счетчика импульсов, коммутатор, блок оперативной памяти, первый триггер, второй элемент И и блок ключей, отличающееся тем, что, с целью упрощения устройства при считывании информации с подвижных кодированных объектов, в него введены первый и второй элементы равнозначности, второй и третий триггеры, блок перепрограммируемой памяти, третий и четвертый элементы И, второй генератор импульсов и блок индикации информации, входы обнуления первого и второго и установочный вход третьего триггеров и вход начальной установки блока индикации информации объединены и являются входом пуска устройства, первые группы входов элементов равнозначности и информационные входы блока ключей соответственно объединены и являются информационными входами устройства, выходы блока ключей соединены с информационными входами блока индикации информации, разрядные выходы счетчика импульсов подключены к первой группе информационных входов коммутатора и входам блока перепрограммируемой памяти, выходы которого соединены со второй группой входов первого элемента равнозначности, выход которого подключен к установочному входу первого триггера, тактовый выход второго генератора и импульсов соединен с тактовым входом блока оперативной памяти, разрядные выходы которого подключены ко второй группе входов второго элемента равнозначности, выход которого соединен с установочным входом второго триггера, прямой выход первого и инверсный выход второго триггеров подключены к первому и второму входам второго элемента И, выход которого соединен с управляющим входом блока ключей, инверсный выход первого и прямой выход второго триггеров подключены к первым входам соответственно третьего и четвертого элементов И, выходы которых соединены с первым и вторым управляющими входами блока индикации информации, выходы которого соединены с информационными входами блока оперативной памяти, адресные выходы второго генератора импульсов подключены к второй группе информационных входов коммутатора, выходы которого соединены с адресными входами блока оперативной памяти, выход переполнения счетчика импульсов соединен с третьим входом второго и вторыми входами третьего и четвертого элементов И и входом обнуления третьего триггера, прямой выход которого подключен к второму входу первого элемента И и управляющему входу коммутатора.

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1547078A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-08-30—Публикация

1990-09-03—Подача