Изобретение относится к радиолокации, а именно к адаптивным антенным системам.

Известна адаптивная антенная система, построенная по схеме с предварительной компенсацией помех и последующим формированием лучей, содержащая N-элементную фазированную антенную решетку (ФАР), выходы которой подключены к блоку векторно-матричного перемножения и к устройству вычисления обратной корреляционной матрицы, блоки скалярного перемножения и источники управляющих сигналов, при этом выходы блока векторно-матричного перемножения подключены к входам блоков скалярного перемножения, другие входы каждого из которых подключены к выходам соответствующего источника управляющих сигналов, а выходы устройства вычисления обратной корреляционной матрицы подключены к другим входам блока векторно-матричного перемножения. Однако данная адаптивная антенная система требует оценивания и обращения корреляционной матрицы помех размера N х N, что при больших N делает сложной реализацию устройства.

Наиболее близкой по технической сущности к данному изобретению является цифровая фазированная антенная система, содержащая L-элементную ФАР, диаграммообразующую схему (ДОС) с аналогоцифровыми преобразователями (АЦП), процессор, блок управления (БУ) и адаптивное устройство (АУ), выполненное в виде трех оперативных ЗУ (ОЗУ), вычислителя скалярного произведения векторов (ВСПВ), вычислителя произведения вектора на скаляр (ВПВС), вычислителя разности векторов (ВРВ), сумматора, делителя, первого и второго коммутаторов, причем L выходов ФАР подключены к соответствующим L входам ДОС, N двухпроводных выходов которой подключены к соответствующим N двухпроводным входам процессора, N двухпроводных выходов которого соединены с N двухпроводным входами ЗУ, N двухпроводных выходов которого соединены с соответствующими N двухпроводными входами первого и третьего ОЗУ, а также с первыми N двухпроводными входами второго коммутатора и ВСПВ, двухпроводный выход которого подключен к первому двухпроводному входу первого коммутатора и первому входу сумматора, второй вход которого является входом для подачи параметра регуляризации, а выход через делитель подключен к второму входу первого коммутатора, двухпроводный выход которого соединен с первым двухпроводным входом ВПВС, N двухпроводных выходов которого соединены с первыми N двухпроводными входами ВРВ и с вторыми двухпроводными входами второго коммутатора, N двухпроводных выходов которого подключены к соответствующим входам второго ОЗУ, N двухпроводных выходов которого подключены к вторым N двухпроводным входам ВПВС, причем вторые N двухпроводные входы ВРВ подключены к соответствующим выходам третьего ОЗУ, а N двухпроводных выходов подключены к вторым N двухпроводным входам процессора и являются выходом цифровой адаптивной фазированной антенной системы, при этом управляющие входы ЗУ, всех ОЗУ, коммутаторов, процессора соединены с соответствующими выходами БУ.

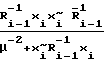

Данное устройство реализует модифицированный алгоритм известной итерационной процедуры вычисления регуляризованной оценки обратной выборочной коррекляционной матрицы (ВКМ) помех Ri-1, согласно которому

R , (1а) где xi - i-й обучающий вектор,

, (1а) где xi - i-й обучающий вектор,

μ-2 - параметр регуляризации; - знак эрмитового сопряжения.

- знак эрмитового сопряжения.

Как известно, в алгоритмах такого типа для получения потерь в эффективности (отношение сигнал/помеха + шум (ОСПШ)) 3dB по сравнению с оптимальной обработкой, необходимое число обучающих векторов определяется из соотношения K ≈ 2P, где P - число источников активных помех. Однако при априорном незнании числа помеховых источников, требуемое число обучающих векторов определится из условия K ≈2Pmax, где Pmax - максимально допустимое число действующих источников помех (Pmax < N), а при P < Pmax итерационная процедура вычисления обратной оценки ВКМ помех по алгоритму (1а) обуславливает высокую чувствительность этого алгоритма к ошибкам вычислений. В результате этого динамические характеристики (зависимость ОСПШ от числа обучающих векторов) при конечной разрядности арифметических устройств (умножителей, сумматоров) имеют для числа обучающих векторов, не превышающего числа действующих помех, нарастающий характер, а при увеличении числа обучающих векторов сверх числа действующих помех либо нарастающий, либо спадающий в зависимости от разрядности арифметических устройств.

Таким образом, при конечной разрядности арифметических устройств и числе обучающих векторов, большем числа действующих помех, наблюдается ухудшение эффективности их подавления, при этом ухудшение пропорционально отношению K/P.

Целью изобретения является повышение эффективности подавления активных помех при сохранении разрядности арифметических устройств.

Это достигается тем, что в цифровую адаптивную фазированную антенную систему, содержащую L-элементную ФАР, ДОС с АЦП, ЗУ, процессор, БУ и адаптивное устройство, выполненное в виде трех ОЗУ, ВСПВ, ВПВС, ВРВ первого и второго коммутаторов, причем L выходов ФАР подключены к соответствующим L входам ДОС, N двухпроводных выходов которой подключены к соответствующим N двухпроводным входам процессора, N-1 двухпроводных выходов которого соединены с N-1 двухпроводными входами первого ЗУ, N двухпроводных выходов которого соединены с соответствующими N двухпроводными входами первого и второго ОЗУ, а также с первыми N двухпроводными входами первого коммутатора и ВСПВ, вторые N двухпроводные входы которого подключены к N двухпроводным выходам первого ОЗУ, причем двухпроводный выход ВСПВ подключен к первому двухпроводному входу второго коммутатора, двухпроводный выход которого соединен с первым двухпроводным входом ВПВС, N двухпроводных выходов которого соединены с соответствующими первыми N двухпроводными входами ВРВ с вторыми N двухпроводными входами первого коммутатора, N двухпроводных выходов которого через третье ОЗУ подключены к вторым N двухпроводным входам ВПВС, причем N вторых двухпроводных входов ВРВ подключены к соответствующим выходам второго ОЗУ, а N двухпроводных выходов подключены к вторым N двухпроводным входам процессора и являются N двухпроводными выходами адаптивной антенной системы, при этом управляющие входы ЗУ, всех ОЗУ, первого комутатора и процессора соединены с соответствующими выходами БУ, введены дополнительно второе и третье ЗУ, третий коммутатор, четвертое ОЗУ, вычислитель скалярных коэффициентов (ВСК), а второй коммутатор выполнен четырехвходовым, причем N-й двухпроводный выход процессора соединен с первым двухпроводным входом третьего коммутатора, второй двухпроводный вход которого соединен с двухпроводным выходом третьего ЗУ, а первый и второй двухпроводные выходы подключены соответственно к N-му двухпроводному входу первого ЗУ и двухпроводному входу второго ЗУ, двухпроводный выход которого соединен с двухпроводным входом четвертого ОЗУ и вторым двухпроводным входом ВСК, третий двухпроводный вход которого соединен с двухпроводным выходом четвертого ОЗУ, а первый двухпроводный вход соединен с двухпроводным выходом ВСПВ, причем первый выход ВСК соединен с вторым входом второго коммутатора, третий и четвертый двухпроводные входы которого подключены соответственно к второму и третьему двухпроводным выходам ВСК, при этом управляющие входы ВСК второго и третьего ЗУ, четвертого ОЗУ, второго и третьего коммутаторов подключены к дополнительным выходам БУ.

Вычислитель скалярных коэффициентов содержит четвертый коммутатор, семь сумматоров, восемь умножителей, первое и второе устройство нахождения обратной величины, устройство извлечения квадратного корня, причем первым входом ВСК является первый двухпроводный вход первого сумматора, вторым двухпроводным входом которого является двухпроводный выход первого умножителя, а двухпроводный выход соединен с входом коммутатора, первый выход которого соединен с первым входом второго сумматора и входом устройства извлечения корня, выход которого соединен с первыми входами второго и третьего умножителей, третьего сумматора и входом первого устройства нахождения обратной величины, выход которого соединен с первым входом четвертого умножителя и является первым выходом ВСК, вторым двухпроводным входом которого являются первые двухпроводные входы первого умножителя, четвертого сумматора и второй двухпроводный вход второго умножителя, двухпроводный выход которого соединен с первым двухпроводным входом пятого сумматора, вторым двухпроводным входом которого является второй двухпроводный выход коммутатора, причем двухпроводный выход пятого сумматора соединен с первым двухпроводным входом пятого умножителя, двухпроводный выход которого соединен с первым двухпроводным входом шестого умножителя и является вторым двухпроводным выходом ВСК, третьим двухпроводным входом которого являются вторые двухпроводные входы третьего сумматора, первого и седьмого умножителей, второй вход третьего умножителя, первый и второй входы восьмого умножителя, выход которого является вторым входом второго сумматора, выход которого является первым входом шестого сумматора, вторым входом которого является выход третьего умножителя, а выход подключен к входу второго устройства нахождения обратной величины, выход которого соединен с первым входом седьмого сумматора и вторым входом четвертого умножителя, выход которого является первым входом седьмого умножителя, двухпроводный выход которого является вторым двухпроводным входом седьмого сумматора, двухпроводный выход которого подключен к второму входу пятого умножителя, кроме того, двухпроводным выходом третьего сумматора является двухпроводный вход шестого умножителя, двухпроводный выход которого соединен с вторым двухпроводным входом четвертого сумматора, двухпроводный выход которого является третьим двухпроводным выходом ВСК, при этом управляющий вход коммутатора подключен к дополнительному выходу БУ.

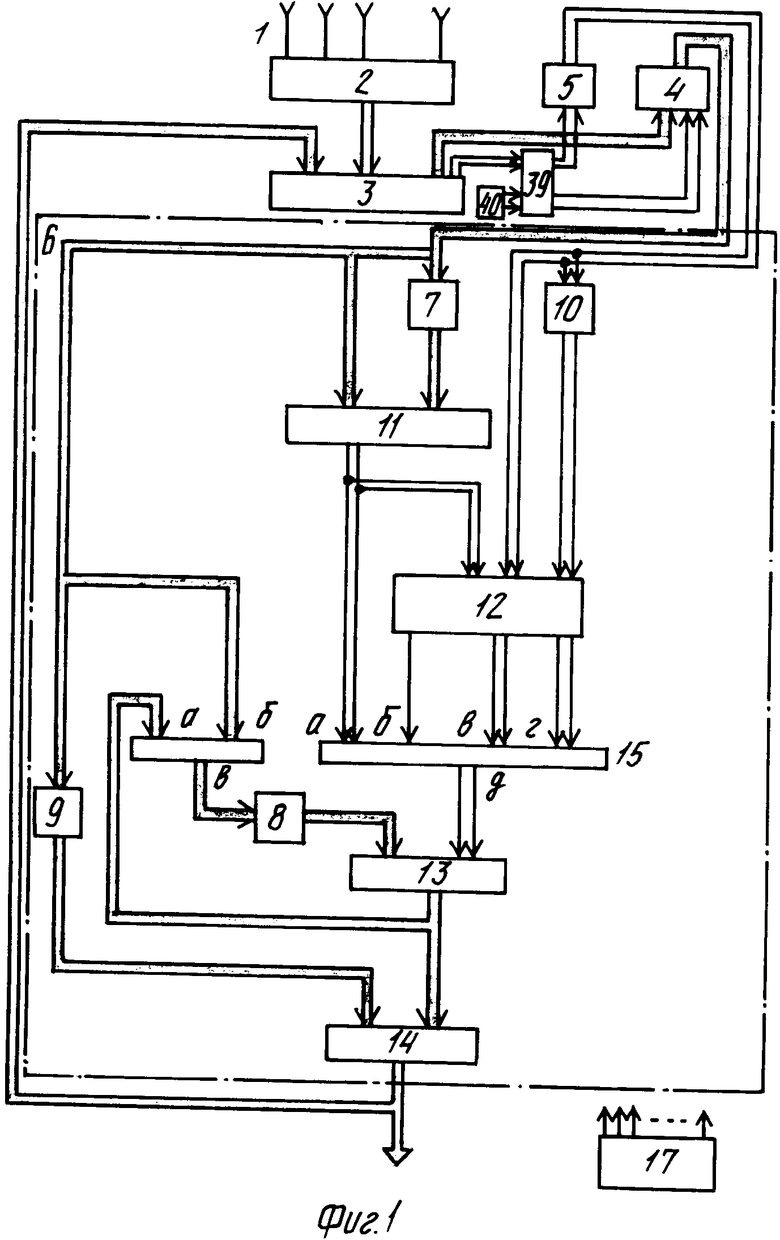

На фиг.1 представлена структурная схема предлагаемого устройства.

Адаптивная антенная система содержит L-элементную ФАР 1, ДОС 2 с АЦП, процессор 3, ЗУ 4, ЗУ 5, ЗУ 40, коммутатор 39, адаптивное устройство 6, содержащее четыре ОЗУ 7,8,9,10, ВСПВ 11, ВПВС 13, ВРВ 14, первый и второй коммутаторы 16, 15, ВСК 12, БУ 17, при этом L выходов ФАР 1 подключены к соответствующим L входам ДОС 2, N двухпроводных выходов которой подключены к соответствующим двухпроводным входам процессора 3, N-1 двухпроводных выходов которого соединены с N-1 двухпроводными входами первого ЗУ 4, а N-й двухпроводный выход процессора 3 соединен с первым двухпроводным входом третьего коммутатора 39, второй двухпроводный вход которого соединен с двухпроводным выходом третьего ЗУ 40, а первый и второй двухпроводные выходы подключены соответственно к двухпроводному входу второго ЗУ 5 и N-му двухпроводному входу первого ЗУ 4, N двухпроводных выходов которого соединены с соответствующими N двухпроводными входами ОЗУ 7 и ОЗУ 9, а также с первыми N двухпроводными входами первого коммутатора 16 и ВСПВ 11, вторые N двухпроводных входов которого подключены к N двухпроводным выходам первого ОЗУ 7, причем двухпроводный выход ВСПВ 11 подключен к первому двухпроводному входу второго коммутатора 15, двухпроводный выход которого соединен с первым двухпроводным входом ВПВС 13, N двухпроводных выходов которого соединены с соответствующими первыми N двухпроводными входами ВРВ 14 и вторыми N двухпроводными входами первого коммутатора 16, N двухпроводных выходов которого через второе ОЗУ 8 подключены к вторым N двухпроводным входам ВПВС 13, причем N вторых двухпроводных входов ВРВ 14 подключены к соответствующим выходам второго ОЗУ 9, а N двухпроводных выходов подключены к вторым N двухпроводным входам процессора 3 и являются N выходами адаптивной антенной системы, кроме того, двухпроводный выход второго ЗУ 5 соединен с двухпроводным входом четвертого ОЗУ 10 и вторым двухпроводным входом четвертого ОЗУ 10 и вторым двухпроводным входом ВСК 12, третий двухпроводный вход которого соединен с двухпроводным выходом четвертого ОЗУ 10, а первый двухпроводный вход соединен с двухпроводным выходом ВСПВ 11, причем первый выход ВСК 12 соединен с вторым входом второго коммутатора 15, третий и четвертый двухпроводные входы которого подключены соответственно к второму и третьему двухпроводным выходам ВСК 12, при этом управляющие входы всех ЗУ, ОЗУ, коммутаторов, процессора подключены к управляющим выходам БУ 17 (на фиг.1 связи управляющих входов с выходами БУ 17 не показаны).

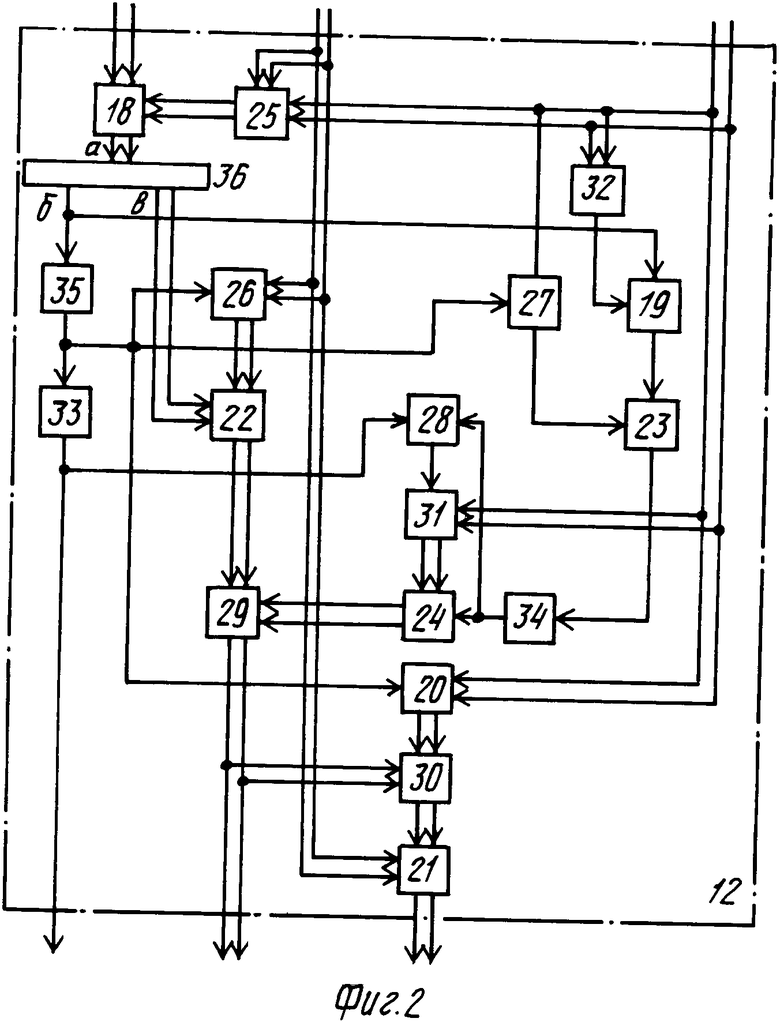

На фиг. 2 представлена функциональная схема ВСК 12, который содержит коммутатор 36, семь сумматоров 18...24, восемь умножителей 25...32, первое и второе устройства нахождения обратной величины 33, 34, устройство извлечения квадратного корня 35, причем первым входом ВСК 12 является первый двухпроводный вход сумматора 18, вторым двухпроводным входом которого является двухпроводный выход умножителя 25, а двухпроводный выход соединен с входом коммутатора 36, первый выход которого соединен с первым входом сумматора 19 и входом устройства извлечения квадратного корня 35, выход которого соединен с первыми входами умножителей 26, 27, сумматора 20 и входом устройства нахождения обратной величины 33, выход которого соединен с первым входом умножителя 28 и является первым выходом ВСК 12, вторым двухпроводным входом которого являются первые двухпроводные входы умножителя 25, сумматора 21 и второй двухпроводный вход умножителя 26, двухпроводный выход которого соединен с первым двухпроводным входом сумматора 22, вторым двухпроводным входом которого является двухпроводный выход коммутатора 36, причем двухпроводный выход сумматора 22 соединен с первым двухпроводным входом умножителя 29, двухпроводный выход которого соединен с первым двухпроводным входом умножителя 30 и является вторым двухпроводным выходом ВСК 12, третьим двухпроводным входом которого являются вторые двухпроводные входы сумматора 20, умножителей 25 и 31, второй вход умножителя 27, первый и второй входы умножителя 32, выход которого является вторым входом сумматора 19, выход которого является первым входом сумматора 23, вторым входом которого является выход умножителя 27, а выход подключен к входу устройства нахождения обратной величины 34, выход которого соединен с первым входом сумматора 24 и вторым входом умножителя 28, выход которого является первым входом умножителя 31, двухпроводный выход которого является вторым двухпроводным входом сумматора 24, двухпроводный выход которого подключен к второму входу умножителя 29, кроме того, двухпроводным выходом сумматора 20 является двухпроводный вход умножителя 30, двухпроводный выход которого соединен с вторым двухпроводным входом сумматора 21, двухпроводный выход которого является третьим двухпроводным выходом ВСК 12, при этом управляющий вход коммутатора подключен к дополнительному выходу БУ 17 (на фиг.2 связь управляющего входа с БУ 17 не показана).

Устройство работает следующим образом.

Сигналы с выходов L-элементной ФАР 1, пришедшие в i-й момент времени, представляющие собой L-элементные векторы χi, поступают на L входов ДОС 2, в которой при помощи матрицы преобразования D, размерности L x N выполняется формирование диаграммы направленности в соответствии с выражением Xi = D , где

, где  знак эрмитова сопряжения. Полученные таким образом векторы Xi преобразуются в ДОС 2 с помощью АЦП в цифровую форму, представлены в виде синфазных и квадратурных составляющих и записываются в ЗУ 4 и 5. Таким образом в ЗУ 4 и 5 записываются k обучающих и m защищаемых векторов, т.е. матрица X =

знак эрмитова сопряжения. Полученные таким образом векторы Xi преобразуются в ДОС 2 с помощью АЦП в цифровую форму, представлены в виде синфазных и квадратурных составляющих и записываются в ЗУ 4 и 5. Таким образом в ЗУ 4 и 5 записываются k обучающих и m защищаемых векторов, т.е. матрица X =  X

X X

X  размерности N x (k+m). С выходов ЗУ 4 и 5 сигналы подаются в АУ 6, состоящее из набора k однотипных модулей, которые работают в трех режимах: обучение, фильтрация обучающих векторов, фильтрация защищаемых векторов. Вначале из ЗУ 4 и 5 считываются элементы обучающих векторов, с помощью которых производится обучение АУ 6 и фильтрация обучающих векторов. После этого АУ 6 имеет характеристику передачи, соответствующую оценке обратной корреляционной матрице помех Rk-1, сформированной по k обучающим векторам. Затем из ЗУ 4 считываются защищаемые векторы, которые в АУ 6 подвергаются пространственной фильтрации согласно выражению

размерности N x (k+m). С выходов ЗУ 4 и 5 сигналы подаются в АУ 6, состоящее из набора k однотипных модулей, которые работают в трех режимах: обучение, фильтрация обучающих векторов, фильтрация защищаемых векторов. Вначале из ЗУ 4 и 5 считываются элементы обучающих векторов, с помощью которых производится обучение АУ 6 и фильтрация обучающих векторов. После этого АУ 6 имеет характеристику передачи, соответствующую оценке обратной корреляционной матрице помех Rk-1, сформированной по k обучающим векторам. Затем из ЗУ 4 считываются защищаемые векторы, которые в АУ 6 подвергаются пространственной фильтрации согласно выражению

Wj = R .

.

Для получения оценки Rk-1 используется формула Морисона-Вудбери, согласно которой

R X

X X

X . . .

. . .  Xi. ..

Xi. .. X

X - матрица размерности Nxk, состоящая из выборки k обучающих векторов Xi =

- матрица размерности Nxk, состоящая из выборки k обучающих векторов Xi =  Xi1, Xi2,..., XiN

Xi1, Xi2,..., XiN , μ-2 - параметр регуляризации; IN - единичная матрица размера N; Т - знак транспонирования. Опуская масштабирующий множитель IN μ-2, представим (1) в виде

, μ-2 - параметр регуляризации; IN - единичная матрица размера N; Т - знак транспонирования. Опуская масштабирующий множитель IN μ-2, представим (1) в виде

Rk-1 = IN - ZkZ , (2) где Ζk =

, (2) где Ζk =

- матрица размерности N х k, являющаяся решением системы уравнений

- матрица размерности N х k, являющаяся решением системы уравнений

Lk Z = X

= X , (3) а Lk - нижняя треугольная матрица, элементы которой lij ((i=

, (3) а Lk - нижняя треугольная матрица, элементы которой lij ((i=  , j=

, j=  )) определяются разложением матрицы Ak = μ-2 + X

)) определяются разложением матрицы Ak = μ-2 + X Xk = LkL

Xk = LkL на треугольные множители.

на треугольные множители.

В предлагаемом устройстве используется наиболее устойчивое к ошибкам вычислений преобразование Хаусхолдера, позволяющее для получения элементов матрицы Lk использовать преобразование над матрицей Xk, не формируя в явном виде матрицу Ak, причем в вычислительных операциях участвуют только векторные величины.

Опишем алгоритм получения элементов lij с помощью преобразования Хаусхолдера. Представим матрицу Ak в виде

Ak = (QYk) (QYk) = G

(QYk) = G Gk, (4) где Yk=

Gk, (4) где Yk=

- матрица размерности (N + k) х k;

- матрица размерности (N + k) х k;

Dk - квадратная диагональная матрица размера k с элементами dii= diag{ μ-1}, i = 1,k,

Gk=

- матрица размера (N + k) х k,

- матрица размера (N + k) х k,

Q - ортогональная матрица Хаусхолдера.

Представив Q в факторизованном виде и с учетом (4) запишем

Gk = Qk...Qi...QiYk = Qk...QiYki-1, (5) где Yki-1 = Qi-1...Q1Yk, (6) причем Y -

-  -

- , Qi = IN+k- UiU

, Qi = IN+k- UiU /uiCi,

/uiCi,

Ui =  yii-1+ δεCi

yii-1+ δεCi - вектор столбец размерности N + k,

- вектор столбец размерности N + k,

y ,

,  ,

,  (8)

(8)

i-й столбец матрицы Yki-1,

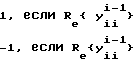

δ=

Re{ ζ } обозначает действительную часть элемента ζ ;

e= 1,0,0

1,0,0 - вектор строка размерности N + k;

- вектор строка размерности N + k;

ui - i-й элемент вектора Ui, Ci2= y yii-1.

yii-1.

Выражение (6) представим в виде операций над векторами

y IN+1 -

IN+1 -  y

y , (9)

, (9)

i= , j=

, j= .

.

Выражение (9) с учетом выражений (7), (8) представим в виде -

- =

= -

- -

- y

y y

y (10) где

(10) где

θi= y

y 1 +

1 +  (11)

(11)

При этом элементы yjii соответствуют элементам lij*, где * - знак комплексного сопряжения. Выражение (10) определяет алгоритм получения элементов lij в предлагаемом устройстве.

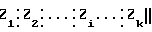

Как следует из выражения (3), вектор Zi определится следующим образом:

Zi=Z xi-

xi- lijZ

lijZ /lii=Z

/lii=Z

Zio = Xi, i= ,

,

Zij = Zij-1 - lij*Zjj, j= ,

,

Zii = Zii-1/lii. Полученные векторы Zi соответствуют оценке обратной корреляционной матрицы помех согласно выражению (2).

Фильтрация защищаемых векторов осуществляется в соответствии с выражением

Wj= X ZiZ

ZiZ .

.

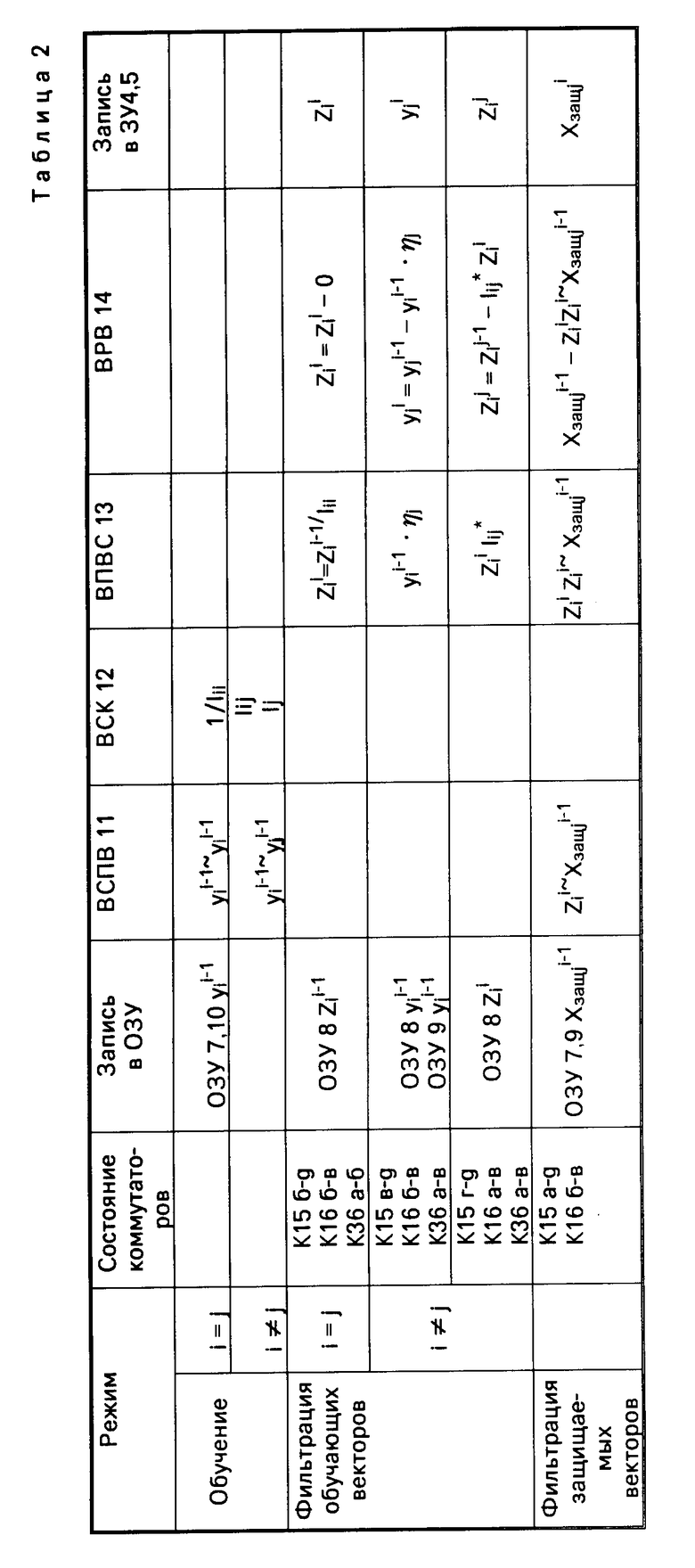

Таким образом i-й модуль работает в трех режимах: обучение (получение элементов lij и ортогонализация векторов yji-1), фильтрация обучающих векторов (получение векторов Zi), фильтрация защищаемых векторов (получение вектора Wj).

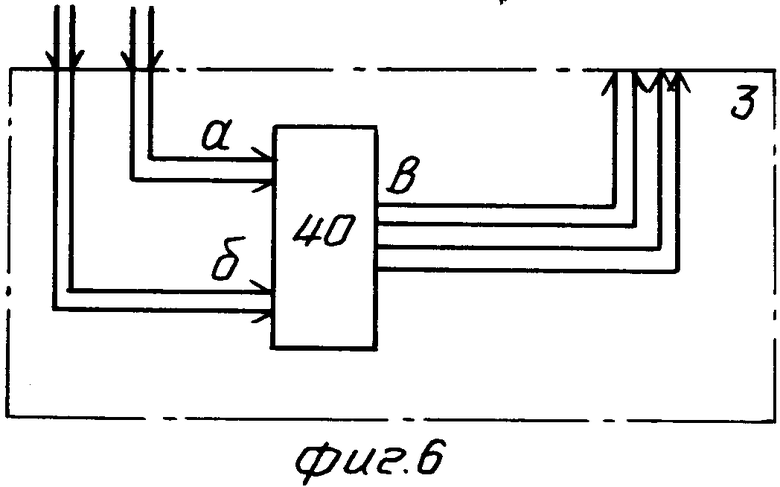

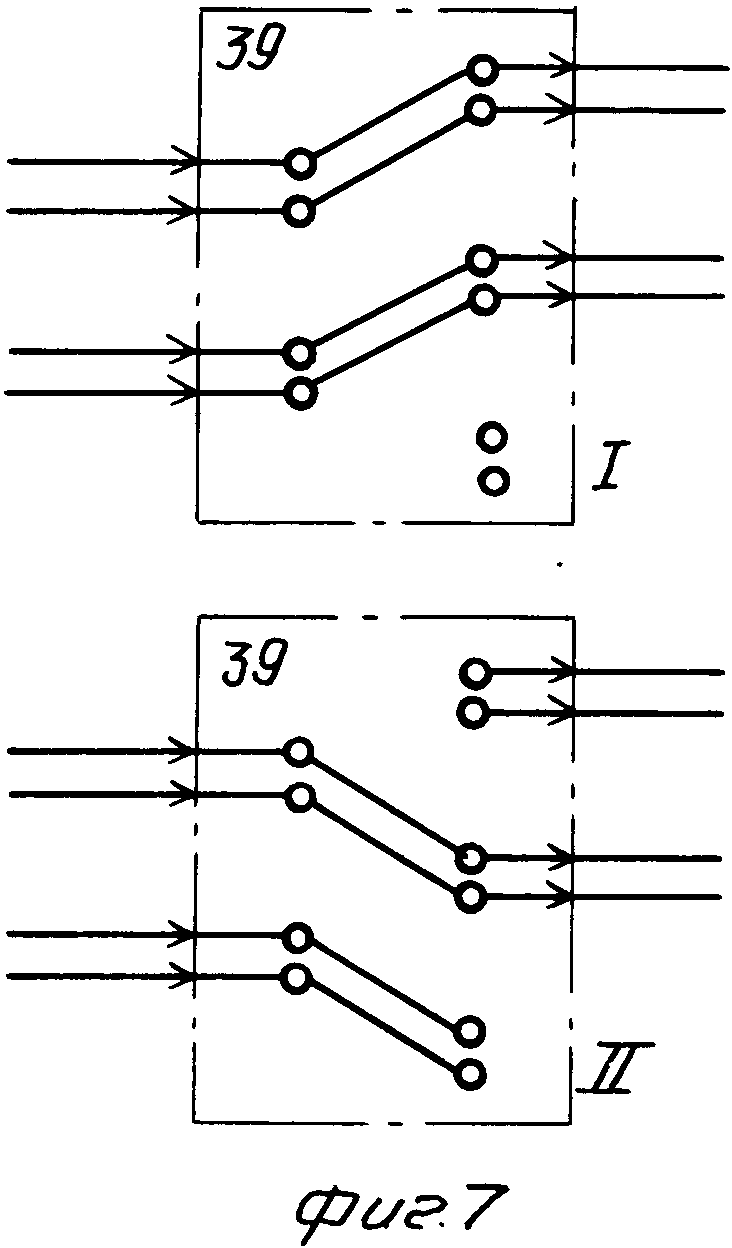

В начальный момент времени, предшествующий обучению, обнуляюnся все ЗУ и ОЗУ. В ЗУ 4 и 5 записываются обучающие векторы Xi ((i= )) в виде синфазных и квадратурных составляющих, для этого коммутатор процессора 3 (см. фиг. 6) соединяет выход ДОС 2 с выходом процессора (замыкаются контакты a-b). При этом первые элементы векторов записываются в ЗУ 5, а остальные, начиная с второго, - в ЗУ 4. В первую N-ю ячейку ЗУ 4 записывается величина μ-1, хранящаяся в ЗУ 40, остальные N-е ячейки ЗУ 4 остаются обнуленными. Запись в ЗУ 4 и 5 осуществляется при положении коммутатора 39, показанном на фиг. 7.I. Затем в ЗУ 4 записываются также m защищаемых векторов размера N (коммутатор 39 в положении, показанном на фиг.7.II.).

)) в виде синфазных и квадратурных составляющих, для этого коммутатор процессора 3 (см. фиг. 6) соединяет выход ДОС 2 с выходом процессора (замыкаются контакты a-b). При этом первые элементы векторов записываются в ЗУ 5, а остальные, начиная с второго, - в ЗУ 4. В первую N-ю ячейку ЗУ 4 записывается величина μ-1, хранящаяся в ЗУ 40, остальные N-е ячейки ЗУ 4 остаются обнуленными. Запись в ЗУ 4 и 5 осуществляется при положении коммутатора 39, показанном на фиг. 7.I. Затем в ЗУ 4 записываются также m защищаемых векторов размера N (коммутатор 39 в положении, показанном на фиг.7.II.).

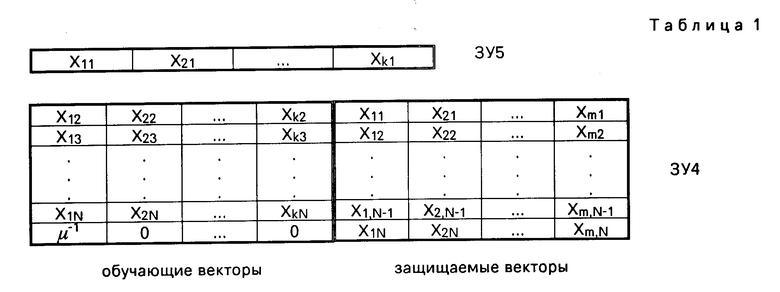

После записи информация в ЗУ 4 и 5 располагается в следующем порядке (см. табл.1).

Обучение i-го модуля.

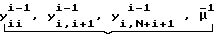

В ОЗУ 7 и 8 записываются из ЗУ 4 N элементов вектора yii-1 ≡  yi,i+1i-1, yi,i+2i-1, . . ., yi,N+i-1i-1, μ-1

yi,i+1i-1, yi,i+2i-1, . . ., yi,N+i-1i-1, μ-1 (в коммутаторе 16 на фиг.1 замкнуты контакты б-в). В ОЗУ 10 из ЗУ 5 записывается величина yiii-1. Затем из ЗУ 4 и 5 начинают поступать векторы yji-1, j=

(в коммутаторе 16 на фиг.1 замкнуты контакты б-в). В ОЗУ 10 из ЗУ 5 записывается величина yiii-1. Затем из ЗУ 4 и 5 начинают поступать векторы yji-1, j= , первые элементы которых из ЗУ 5 поступают на второй вход ВСК12, а последующие из ЗУ 4 на вход ВСПВ 11 и записываются в ОЗУ 9. ВСПВ 11 вычисляет величину y

, первые элементы которых из ЗУ 5 поступают на второй вход ВСК12, а последующие из ЗУ 4 на вход ВСПВ 11 и записываются в ОЗУ 9. ВСПВ 11 вычисляет величину y yji-1 (i=

yji-1 (i=  , j=

, j=  ) за вычетом величины yiii-1*yiji-1 , которая вычисляется в ВСК12 умножителем 25. В сумматоре 18 находится полное значение y

) за вычетом величины yiii-1*yiji-1 , которая вычисляется в ВСК12 умножителем 25. В сумматоре 18 находится полное значение y yji-1. Если i = j, тогда синфазный вход коммутатора 36 соединен с входом устройства извлечения корня 35, выход которого подключен к устройству нахождения обратной величины 33, на выходе которого формируется величина 1/lii, которая хранитися в регистре этого устройства (фиг.2). При i ≠ j двухпроводный вход коммутатора 36 соединен с двухпроводным входом сумматора 22, на второй и третий вход ВСК 12 поступают величины yjii-1 и yiii-1 соответственно. На выходе умножителя 29 формируется величина ηj = θi(y

yji-1. Если i = j, тогда синфазный вход коммутатора 36 соединен с входом устройства извлечения корня 35, выход которого подключен к устройству нахождения обратной величины 33, на выходе которого формируется величина 1/lii, которая хранитися в регистре этого устройства (фиг.2). При i ≠ j двухпроводный вход коммутатора 36 соединен с двухпроводным входом сумматора 22, на второй и третий вход ВСК 12 поступают величины yjii-1 и yiii-1 соответственно. На выходе умножителя 29 формируется величина ηj = θi(y yji-1 + Ciyjii-1), причем θi формируется на выходе сумматора 7. Следующий шаг - ортогонализация векторов yji-1 и получение элементов lij согласно выражению (10). При этом элементы Iij вычисляются в ВСК 12 согласно формуле

yji-1 + Ciyjii-1), причем θi формируется на выходе сумматора 7. Следующий шаг - ортогонализация векторов yji-1 и получение элементов lij согласно выражению (10). При этом элементы Iij вычисляются в ВСК 12 согласно формуле

lij* = yjii = yjii-1 - (yiii-1 + Ci) ηj (14) с использованием сумматоров 20, 21 и умножителя 30, а ортогонализация векторов yji-1, начиная с (i+1)-го элемента, производится следующим образом: величина ηj с второго выхода ВСК 12 через коммутатор 15 (в-д) поступает на первый вход ВСПВ 13, на второй вход которого поступает из ОЗУ 8 величина yii-1, начиная с (i+1)-го элемента. ВСПВ 13 находит величину yii-1 ηj, которая затем поступает на первый вход ВРВ 14, на второй вход которого из ОЗУ 9 поступает вектор yji-1, начиная с (i+1)-го элемента. Результатом вычислений в ВРВ 14 является вектор yji, i-й элемент которого записывается в ЗУ 5, а начиная с (i+1)-го - в ЗУ 4 (коммутатор процессора 3 в положении б-в (см. фиг.6)). Таким образом с получением элементов lij и векторов yji обучение i-го модуля заканчивается.

Фильтрация обучающих векторов.

В ОЗУ 8 записывается вектор Zii-1 (коммутатор 16 в состоянии б-в), ОЗУ 9 обнуляется. При i = j на первый вход ВПВС 13 через второй вход коммутатора 15 (б-д) из ВСК 12 поступает величина 1/lii, на второй вход ВПВС 13 из ОЗУ 8 поступает вектор Zii-1. ВПВС 13 вычисляет величину Zii= Zii-1/lii. Полученный таким образом вектор Zii через коммутатор 16 (a-в) перезаписывается в ОЗУ 8, а также поступает на первый вход ВРВ 14, на второй вход которого из ОЗУ 9 поступает О-вектор и на выходе ВРВ 14 вектор Zii остается без изменений, является выходом обученной адаптивной антенной системы и записывается в ЗУ 4.

При i ≠ j в ОЗУ 9 записывается вектор Zji-1. На вход ВПВС 13 через коммутатор 15 (г-д) поступает величина lij с третьего выхода ВСК 12. ВПВС 13 вычисляет элементы вектора lijZii, которые затем поступают на первый вход ВРВ 14, на второй вход которого из ОЗУ 9 поступают элементы вектора Zji-1. Результатом вычислений в ВРВ 12 является вектор Zji = Zji-1 - lij*Zii, который записывается в ЗУ 4 и поступает на фильтрацию в следующий (i+1)-й модуль.

Получением векторов Zii (i= ) заканчивается процесс фильтрации обучающих векторов.

) заканчивается процесс фильтрации обучающих векторов.

Фильтрация защищаемых векторов осуществляется согласно выражению (13). Вход ВПВС 11 через первый вход коммутатора 15 (а-д) подключен к выходу ВПВС 11. В ОЗУ 7 и ОЗУ 9 записываются векторы Xзащ.ji-1, поступающие с (i-1)-го модуля. В ОЗУ 8 хранится вектор Zii. После выполнения операции согласно 13 на выходе ВРВ 14 вычисляется вектор Xзащ.ji, который является выходным эффектом адаптивной антенной системы. Для наглядности основные операции, выполняемые в предлагаемом устройстве, сведены в табл.2.

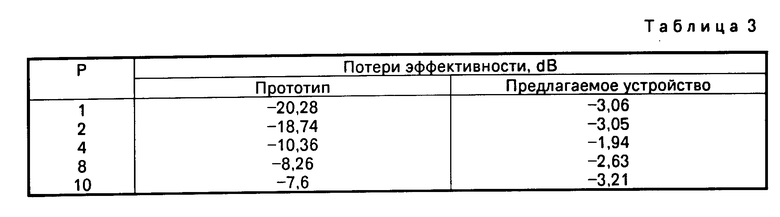

Применение предлагаемого устройства позволило повысить эффективность подавления помех при сохранении разрядности арифметических устройств умножителей и сумматоров, причем эффективность повышается с ростом отношения k/p.

Для примера в табл.3 приведены значения потерь эффективности отношения сигнал/помеха+шум от числа действующих помех при числе обучающих векторов k = 20 (Pmax = 10), для N = 30, μ-2 = 2-12, при суммарной мощности помех PΕ = 43dB, действующих по максимумам боковых лепестков (начиная с первого) для прототипа и предлагаемого устройства при разрядности арифметических устройств 14 бит и выполнении арифметических операций с фиксированной запятой.

Как следует из табл. 3, в широком диапазоне изменений и при заданной разрядности арифметических устройств потери в предлагаемом устройстве не превышают -3,21dB, в то время как в прототипе достигают -20,28dB, что свидетельствует о более высокой эффективности подавления помех предлагаемым устройством.

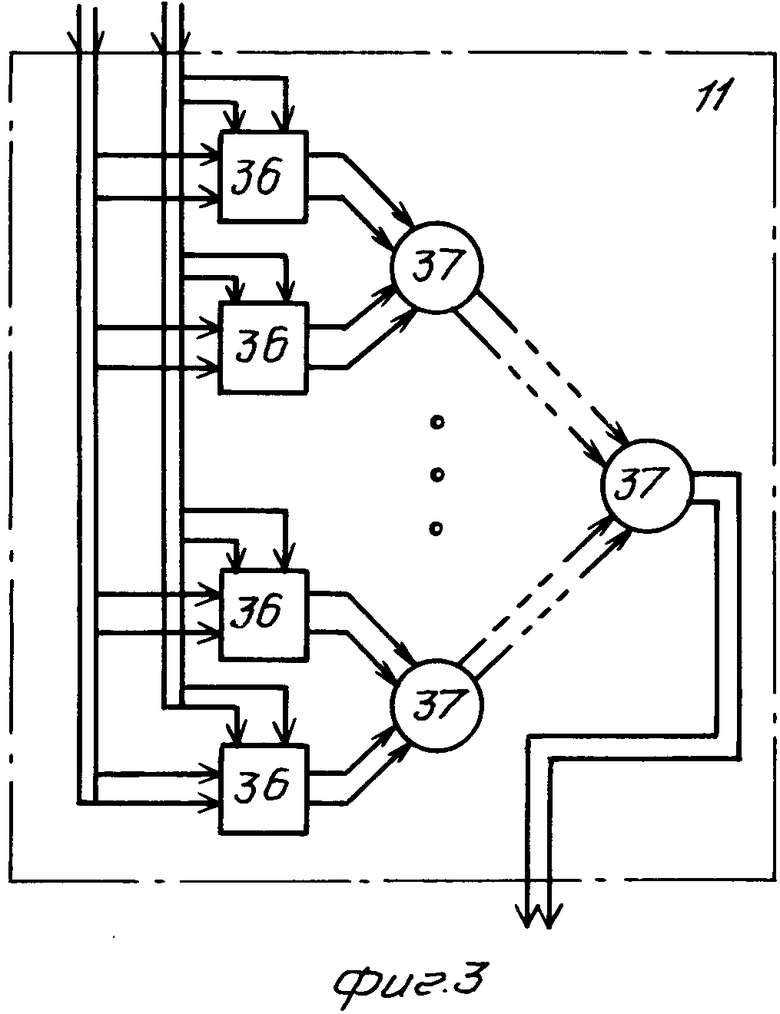

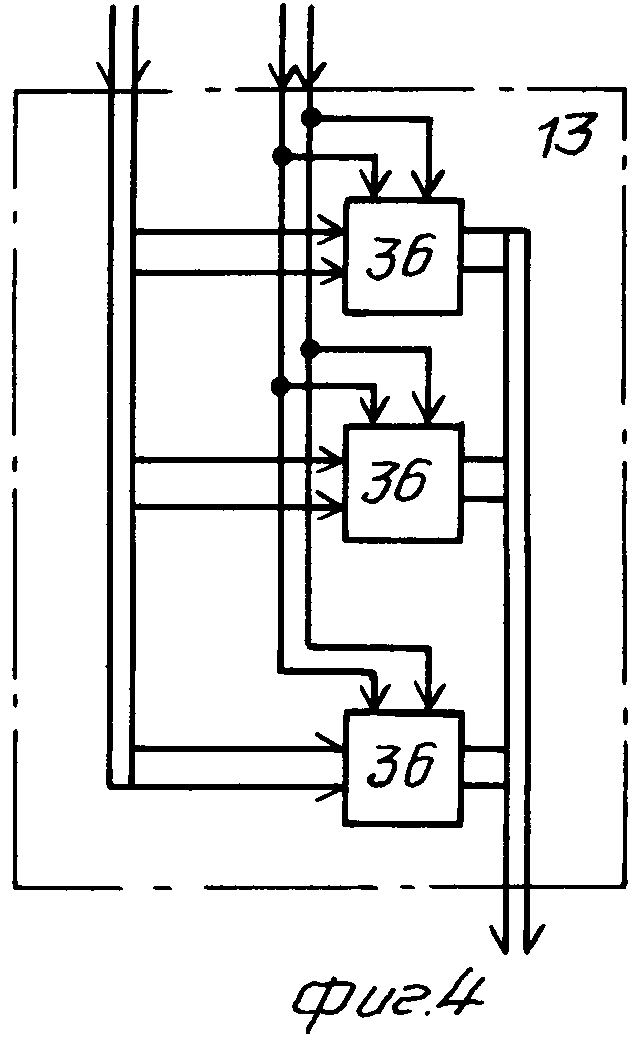

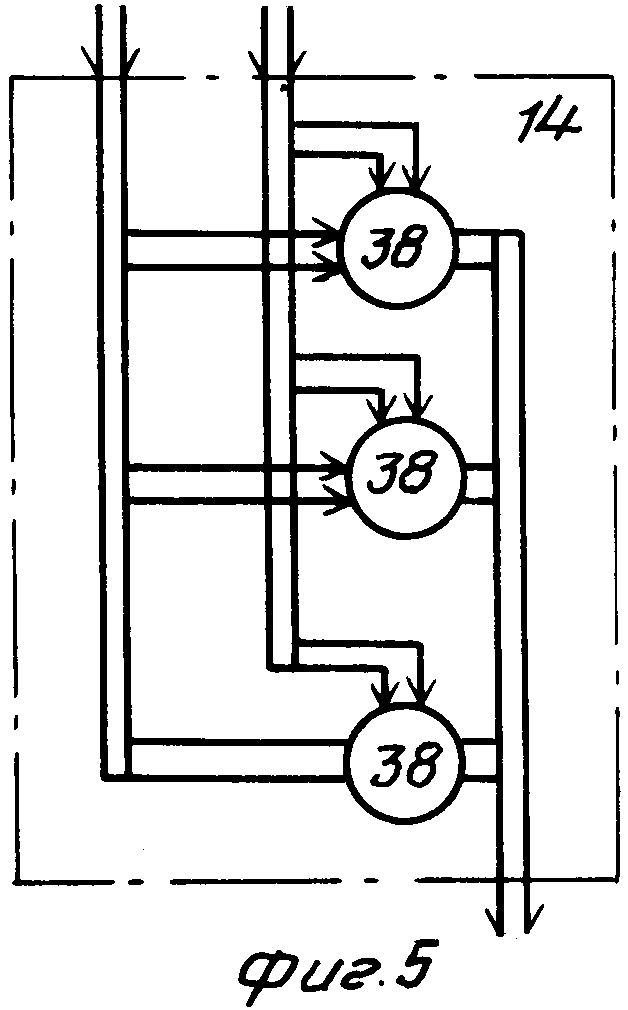

Возможные варианты реализации ВСПВ 11, ВПВС 13, ВРВ 14 представлены на фиг. 3-5, соответственно, где 36 - комплексные умножители, 37 - комплексные сумматоры, 38 - комплексные вычитаторы. Для нахождения произведения двух операндов могут применяться комплексные умножители, использующие действительные умножители серии 1802 ВР5. Комплексные сумматоры (вычитаторы) могут быть реализованы на базе сумматоров той же серии - 1802 МИ1. Коммутаторы могут быть реализованы на мультиплексорах 155 КП11. В качестве ЗУ 4, 5 и 40 можно использовать ЗУ серии 132 РУ10, а в качестве ОЗУ 7, 8, 9, 10 - 155 ИР23. Устройства нахождения обратной величины 33, 34 и извлечения квадратного корня 35 могут быть рализованы на ПЗУ, использующих табличные методы нахождения результата.

Таким образом, предлагаемое устройство позволяет повысить эффективность подавления активных помех при числе обучающих векторов, большем числа действующих помех, и сохранении разрядности арифметических устройств. Это стало возможным благодаря использованию в предлагаемом устройстве одного из самых устойчивых к ошибкам вычислений методов линейной алгебры - преобразования Хаусхолдера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая адаптивная фазированная антенная система (ее варианты) | 1982 |

|

SU1228172A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| ЦИФРОВАЯ АДАПТИВНАЯ МНОГОЛУЧЕВАЯ АНТЕННАЯ СИСТЕМА | 1990 |

|

RU2033670C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для нахождения оптимального вектора решения системы линейных неравенств | 1985 |

|

SU1315996A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДИСКРЕТНОГО КОСИНУСНОГО ПРЕОБРАЗОВАНИЯ | 2010 |

|

RU2430407C1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

Использование: в радиолокации, для защиты радиолокационных станций от активных помех, повышение эффективности подавления помех при сохранении разрядности арифметических устройств. Сущность изобретения: антенная система содержит фазированную антенную решетку, диаграммообразующую схему с аналого-цифровыми преобразователями, процессор, три запоминающих устройства, коммутатор, блок управления, адаптивное устройство, содержащее четыре оперативных запоминающих устройства, вычислитель скалярного произведения векторов, вычислитель скалярных коэффициентов, вычислитель произведения вектора на скаляр, вычислитель разности векторов, первый, второй коммутаторы. 1 з.п. ф-лы, 7 ил, 2 табл.

| Цифровая адаптивная фазированная антенная система (ее варианты) | 1982 |

|

SU1228172A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-09-30—Публикация

1991-07-08—Подача