(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения интерфейсов | 1991 |

|

SU1798791A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ИНТЕРФЕЙСОВ | 1990 |

|

RU2022345C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для передачи информации | 1989 |

|

SU1762307A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1339896A1 |

Изобретение относится к вычислительной технике и может быть использовано для подключения периферийных устройств, имеющих интерфейс типа И41, к электронным цифровым машинам (например, персональной ЭВМ ЕС1840), имеющим выходной интерфейс стык С2. Цель изобретения - упрощение устройства. Для этого, в устройство, содержащее элементы приема и передачи информации, тактовый генератор распределитель импульсов, два регистра адреса и четыре регистра, введены два узла укорочения длительности импульса, два делителя числа импульсов, пять триггеров, элементы И-НЕ, элемент И, элемент ИЛИ- НЕ и узел начального сброса. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано для подключения периферийных устройств, имеющих интерфейс типа И41, к электронным цифровым машинам (например, персональной ЭВМ ЁС1840), имеющим выходной интерфейс стык С2 (Р - 232С). причем периферийное устройство и ЭВМ могут быть расположены на больших расстояниях друг от друга.

Цель изобретения - упрощение устройства.

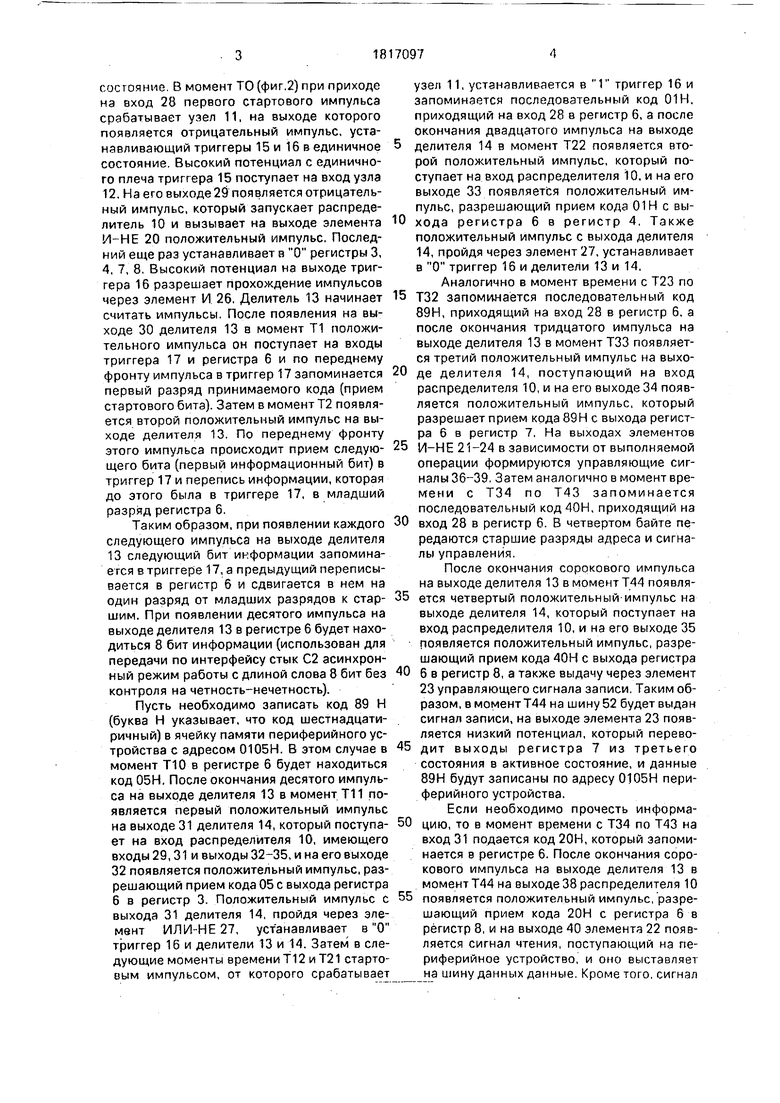

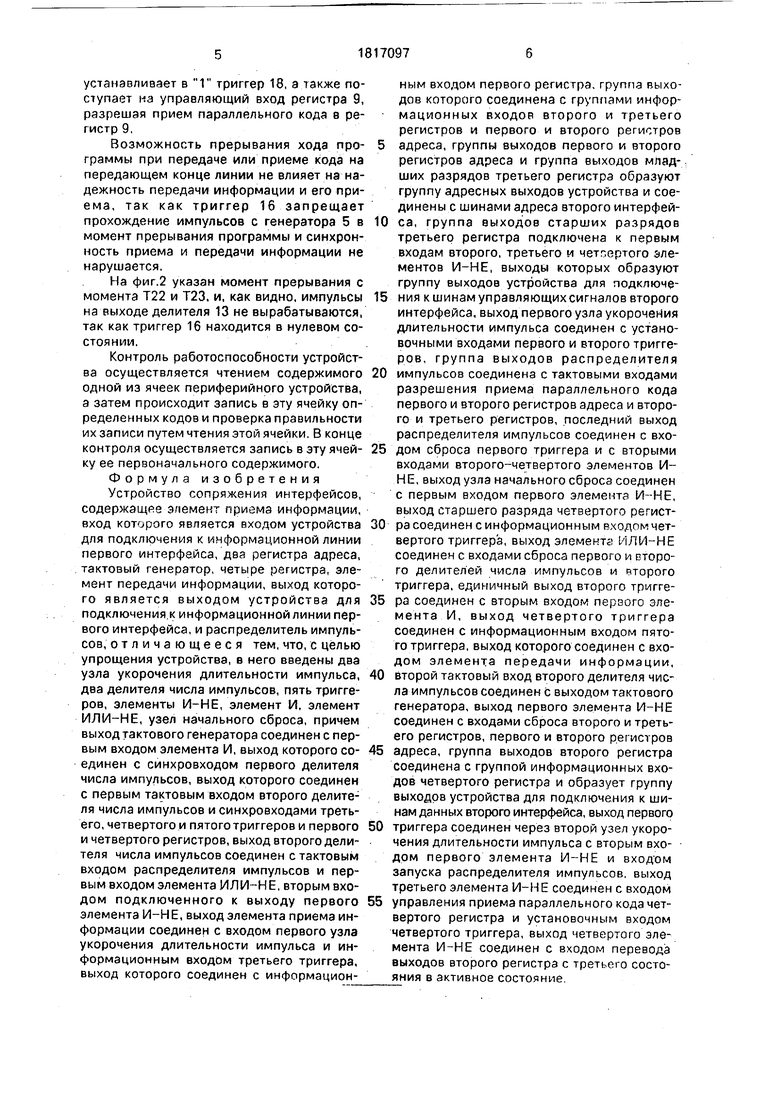

Структурная схема устройства представлена на фиг.1; временная диаграмма - на фиг.2.

Устройство сопряжения (фиг.1) содержит элемент 1 приема, элемент 2 передачи информации, регистры адреса 3 и 4 интерфейса И41 (второго интерфейса), тактовый генератор 5, четыре регистра 6-9, причем регистр 7 имеет возможность перевода выходов в третье состояние, распределитель 10 импульсов, узлы 11, 12 укорочения длительности импульса, делители 13, 14 числа импульсов, триггеры 15-19, элементы И-НЁ 20-24, узел 25 начального сброса, элемент И 26, элемент ИЛИ-НЕ 27, линии 28-39 входов и выходов элементов устройства, регистр 40 и элементы И 41-44 распределителя импульсов, линии 45 и 46 выходов элементов устройства.

Устройство работает следующим образом,

При включении питания на вход элемента И-НЕ 20 поступает с узла 25 отрицательный импульс и на выходе элемента И-НЕ 20 появляется высокий потенциал, устанавливающий регистры 3, 4, 7, 8 в О и поступающий на вход элемента ИЛИ-НЕ 27, на выходе которого появляется низкий потенциал. Этот потенциал устанавливает триггер 16 и делители 13.и 14 в нулевое

со

-ч о о

NJ

состояние. В момент ТО (фиг.2) при приходе на вход 28 первого стартового импульса срабатывает узел 11, на выходе которого появляется отрицательный импульс, устанавливающий триггеры 15 и 16 в единичное состояние. Высокий потенциал с единичного плеча триггера 15 поступает на вход узла 12. На его выходе 29 появляется отрицательный импульс, который запускает распределитель 10 и вызывает на выходе элемента И-НЕ 20 положительный импульс. Последний еще раз устанавливает в О регистры 3, 4, 7, 8. Высокий потенциал на выходе триггера 16 разрешает прохождение импульсов через элемент И 26. Делитель 13 начинает считать импульсы, После появления на выходе 30 делителя 13 в момент Т1 положительного импульса он поступает на входы триггера 17 и регистра 6 и по переднему фронту импульса в триггер 17 запоминается первый разряд принимаемого кода (прием стартового бита). Затем в момент Т2 появляется второй положительный импульс на выходе делителя 13, По переднему фронту этого импульса происходит прием следующего бита (первый информационный бит) в триггер 17 и перепись информации, которая до этого была в триггере 17, в младший разряд регистра 6.

Таким образом, при появлении каждого следующего импульса на выходе делителя 13 следующий бит информации запоминается в триггере 17, а предыдущий переписывается в регистр 6 и сдвигается в нем на один разряд от младших разрядов к старшим. При появлении десятого импульса на выходе делителя 13 в регистре 6 будет находиться 8 бит информации (использован для передачи по интерфейсу стык С2 асинхронный режим работы с длиной слова 8 бит без контроля на четность-нечетность).

Пусть необходимо записать код 89 Н (буква Н указывает, что код шестнадцатиричный) в ячейку памяти периферийного устройства с адресом 0105Н. В этом случае в момент Т10 в регистре 6 будет находиться код 05Н. После окончания десятого импульса на выходе делителя 13 в момент Т11 появляется первый положительный импульс на выходе 31 делителя 14, который поступает на вход распределителя 10, имеющего входы 29,31 и выходы 32-35, и на его выходе 32 появляется положительный импульс, разрешающий прием кода 05 с выхода регистра 6 в регистр 3. Положительный импульс с выхода 31 делителя 14, пройдя через элемент И Л И-НЕ 27, устанавливает в О триггер 16 и делители 13 и 14. Затем в следующие моменты времени Т12 иТ21 стартовым импульсом, от которого срабатывает

узел 11, устанавливается в 1 триггер 16 и запоминается последовательный код 01 Н, приходящий на вход 28 в регистр 6, а после окончания двадцатого импульса на выходе

делителя 14 в момент Т22 появляется второй положительный импульс, который поступает на вход распределителя 10, и на его выходе 33 появляется положительный импульс, разрешающий прием кода 01Н с вы0 хода регистра 6 в регистр 4, Также положительный импульс с выхода делителя 14, пройдя через элемент 27, устанавливает в О триггер 16 и делители 13 и 14.

Аналогично в момент времени с Т23 по

5 Т32 запоминается последовательный код 89Н, приходящий на вход 28 в регистр 6. а после окончания тридцатого импульса на выходе делителя 13 в момент ТЗЗ появляется третий положительный импульс на выхо0 де делителя 14, поступающий на вход распределителя 10, и на его выходе 34 появляется положительный импульс, который разрешает прием кода 89Н с выхода регистра 6 в регистр 7, На выходах элементов

5 И-НЕ 21-24 в зависимости от выполняемой операции формируются управляющие сигналы 36-39, Затем аналогично в момент вре- мени с Т34 по Т43 запоминается последовательный код40Н, приходящий на

0 вход 28 в регистр 6. В четвертом байте передаются старшие разряды адреса и сигналы управления.

После окончания сорокового импульса на выходе делителя 13 в момент Т44 появля5 ется четвертый положительный импульс на выходе делителя 14, который поступает на вход распределителя 10, и на его выходе 35 Появляется положительный импульс, разрешающий прием кода 40Н с выхода регистра

0 б в регистр 8, а также выдачу через элемент 23 управляющего сигнала записи, Таким образом, в момент Т44 на шину 52 будет выдан сигнал записи, на выходе элемента 23 появляется низкий потенциал, который перево5 дит выходы регистра 7 из третьего состояния в активное состояние, и данные 89Н будут записаны по адресу ОЮ5Н периферийного устройства.

Если необходимо прочесть информа0 цию, то в момент времени с Т34 по Т43 на вход 31 подается код 20Н, который запоминается в регистре 6. После окончания сорокового импульса на выходе делителя 13 в момент Т44 на выходе38 распределителя 10

5

появляется положительный импульс, разрешающий прием кода 20Н с регистра 6 в регистр 8, и на выходе 40 элемента 22 появляется сигнал чтения, поступающий на периферийное устройство, и оно выставляет на шину данных данные. Кроме того, сигнал

устанавливает в 1 триггер 18, а.также поступает «а управляющий вход регистра 9, разрешая прием параллельного кода в регистр 9,

Возможность прерывания хода программы при передаче или приеме кода на передающем конце линии не влияет на надежность передачи информации и его при- ема, так как триггер 16 запрещает прохождение импульсов с генератора 5 в момент прерывания программы и синхронность приема и передачи информации не нарушается.

На фиг.2 указан момент прерывания с момента Т22 и Т23. и, как видно, импульсы на выходе делителя 13 не вырабатываются, так как триггер 16 находится в нулевом состоянии..

Контроль работоспособности устройства осуществляется чтением содержимого одной из ячеек периферийного устройства, а затем происходит запись в эту ячейку определенных кодов и проверка правильности их записи путем чтения этой ячейки. В конце контроля осуществляется запись в эту ячейку ее первоначального содержимого.

Формула изобретения

Устройство сопряжения интерфейсов, содержащее элемент приема информации, вход которого является входом устройства для подключения к информационной линии первого интерфейса, два регистра адреса, тактовый генератор, четыре регистра, элемент передачи информации, выход которого является выходом устройства для подключения информационной линии первого интерфейса, и распределитель импульсов, отличающееся тем, что, с целью упрощения устройства, в него введены два узла укорочения длительности импульса, два делителя числа импульсов, пять триггеров, элементы И-НЕ, элемент И, элемент ИЛИ-НЕ, узел начального сброса, причем выход тактового генератора соединен с первым входом элемента И, выход которого соединен с синхровходом первого делителя числа импульсов, выход которого соединен с первым тактовым входом второго делителя числа импульсов и синхровходами третьего, четвертого и пятого триггеров и первого и четвертого регистров, выход второго делителя числа импульсов соединен с тактовым входом распределителя импульсов и первым входом элемента ИЛИ-НЕ, вторым входом подключенного к выходу первого элемента И-НЕ, выход элемента приема информации соединен с входом первого узла укорочения длительности импульса и информационным входом третьего триггера, выход которого соединен с информационным входом первого регистра, группа выходов которого соединена с группами инфор- мационных входов второго и третьего регистров и первого и второго регистров адреса, группы выходов первого и второго регистров адреса и группа выходов млад-; ших разрядов третьего регистра образуют группу адресных выходов устройства и соединены с шинами адреса второго интерфей0 са, группа выходов старших разрядов третьего регистра подключена к первым входам второго, третьего и четвертого элементов И-НЕ, выходы которых образуют группу выходов устройства для подключе5 ния к шинам управляющих сигналов второго интерфейса, выход первого узла укорочения длительности импульса соединен с установочными входами первого и второго триггеров, группа выходов распределителя

0 импульсов соединена с тактовыми входами разрешения приема параллельного кода первого и второго регистров адреса и второго и третьего регистров, последний выход распределителя импульсов соединен с вхо5 дом сброса первого триггера и с вторыми входами второго-четвертого элементов И- НЕ, выход узла начального сброса соединен с первым входом первого элемента И-НЕ, выход старшего разряда четвертого регист0 ра соединен с информационным входом четвертого триггера, выход элемента ИЛИ-НЕ соединен с входами сброса первого и второго делителей числа импульсов и второго триггера, единичный выход второго тригге5 ра соединен с вторым входом первого элемента И, выход четвертого триггера соединен с информационным входом пятого триггера, выход которого соединен с входом элемента передачи информации,

0 второй тактовый вход второго делителя числа импульсов соединен с выходом тактового генератора, выход первого элемента И-НЕ соединен с входами сброса второго и третьего регистров, первого и второго регистров

5 адреса, группа выходов второго регистра соединена с группой информационных входов четвертого регистра и образует группу выходов устройства для подключения к шинам данных второго интерфейса, выход первого

0 триггера соединен через второй узел укорочения длительности импульса с вторым входом первого элемента И-НЕ и входом запуска распределителя импульсов, выход третьего элемента И-НЕ соединен с входом

5 управления приема параллельного кода четвертого регистра и установочным входом четвертого триггера, выход четвертого элемента И-НЕ соединен с входом перевода выходов второго регистра с третьего состояния в активное состояние.

28

46

77 75 ТП 7№ПЗ Т28 Ш Т39 Щ W Т5Ь Т57

У)

Л

сг

К

V

Л6 37 38 ЗЭ

| Патент США № 3587058, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-23—Публикация

1989-12-08—Подача