Изобретение относится к вычислительной технике и может быть использовано для подключения периферийных устройств к электронным цифровым машинам (например, к персональной ЭВМ), имеющим выходной интерфейс стык С2 (RS-232C).

Цель изобретения - упрощение устройства.

Указанная цель достигается тем, что устройство сопряжения интерфейсов, содержащее шины первого и второго интерфейсов, элементы приема и передачи информации, первый и второй регистры адреса, тактовый генератор, содержит пять регистров, элемент задержки, формирователь импульсов, два делителя числа импульсов, с .первого по пятый триггеры, элемент ИЛИ- НЕ, пять элементов ИЛИ-НЕ, узел начального сброса, выход тактового генератор соединен через элемент И с входом первого из последовательно включенных делителей числа импульсов; выход второго элемента И соединен через элемент задержки И и элемент ИЛИ-НЕ с R-входом RS-триггера и первым и вторым регистрами.

Выход первого делителя соединен с С- входом третьего и четвертого регистров и с С-входом второго, третьего и четвертого триггеров, выход второго делителя соединен с входами элементов И, начиная со второго, с входом С пятого триггера и второго регистра, выходы элементов И, начиная со второго, соединены с входами С соответственно первого и пятого регистров первого и второго регистров адреса, единичный выход RS-триггера соединен с входом формирователя и входом первого элемента И, выход формирователя соединен с входом S пятого триггера и через первый эгемент И-НЕ с входом R всех делителей и вторым входом элемента ИЛИ-НЕ. Выход элемента приема соединен с входом S RS-триггера, с D-вхо- дом второго триггера, выход которого соединен с DR-входом третьего регистра, выходы которого соединены с внутренней шиной устройства, которая соединена с входами всех разрядов регистров адреса и перIn|С

v| О 00 VI

ю

вого и пятого регистров, выходы регистров адреса и четыре младших разряда первого регистра поступают на шины адреса второго интерфейса, выходы пятого и входы четвертого регистров поступают на шины данных второго интерфейса, выходы стар- -ших разрядов первого регистра поступают через элементы И-НЕ, начиная со второго, на шины управляющих сигналов второго интерфейса. Выход схемы начального сброс- соединен с входом первого элемента И-НЕ, выход старшего разряда четвертого регистра соединен со входом D третьего триггера, выход которого соединен с D входом четвертого триггера, инверсный выход которого соединен с входом элемента передачи, выход которого соединен с выходом устройства, вход элемента приема соединен с входом устройства, выход третьего элемента И-НЕ - с входом установки в единицу третьего триггера и с входом разрешения приема параллельного кода в четвертый регистр, выход четвертого элемента И-ИЕ соединен с входом перевода в третье состояние пятого регистра, выход пятого триггера соединен с входом второго регистра, выводы которого соединены с входами элементов И, начиная со второго.

В устройство дополнительно введены пять регистров, элемент задержки, форми- рователь импульсов , два Делителя числа импульсов, элемент ИЛИ-НЕ, пять элементов И-НЕ и И, схема начального сброса, три Dt-триггера, один RS-триггер, установкой в единицу которого разрешается прохожде- ние тактовых импульсов на вход делителей числа импульсов, которые определяют синхронизацию приема кода и выдачу кода и определяют время выдачи управляющих сигналов. Это позволяет осуществить связь ЭВМ, имеющей интерфейс С2, с периферийным устройством с интерфейсом И 41, не применяя в интерфейсном устройстве дополнитёльного микропроцессора связи и ОЗУ и ПЗУ, его обслуживающих, и позволя- ет существенно сократить более чем на 10% количество оборудования,

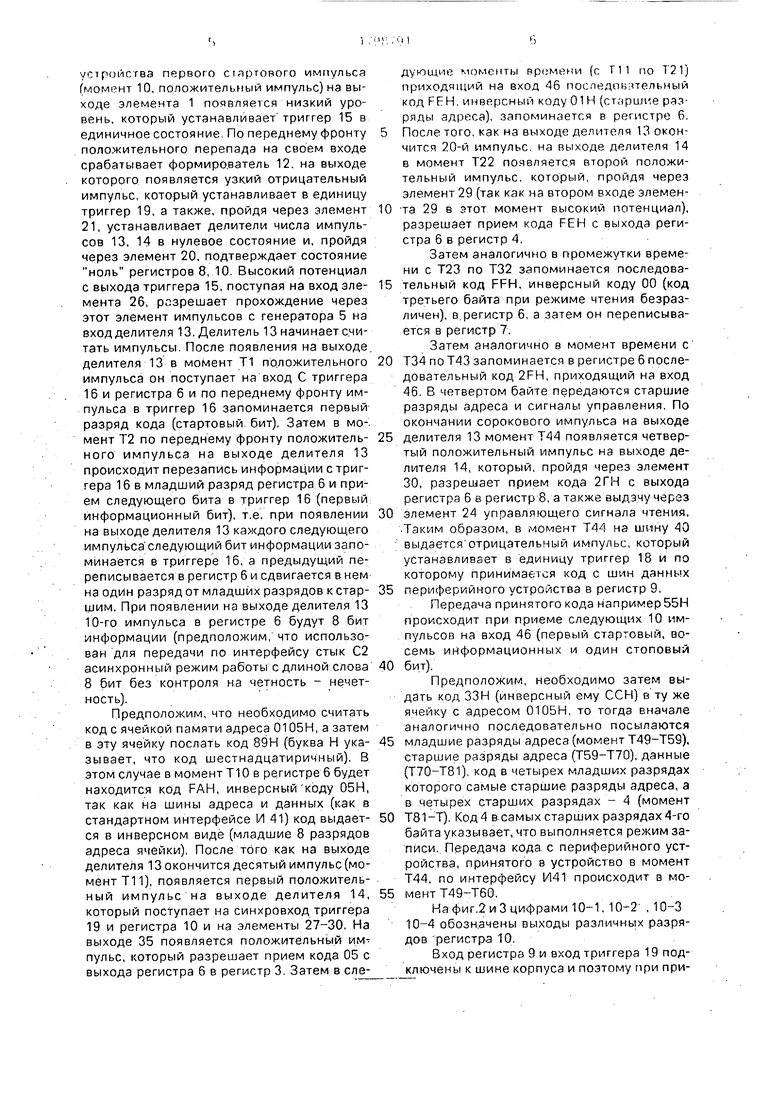

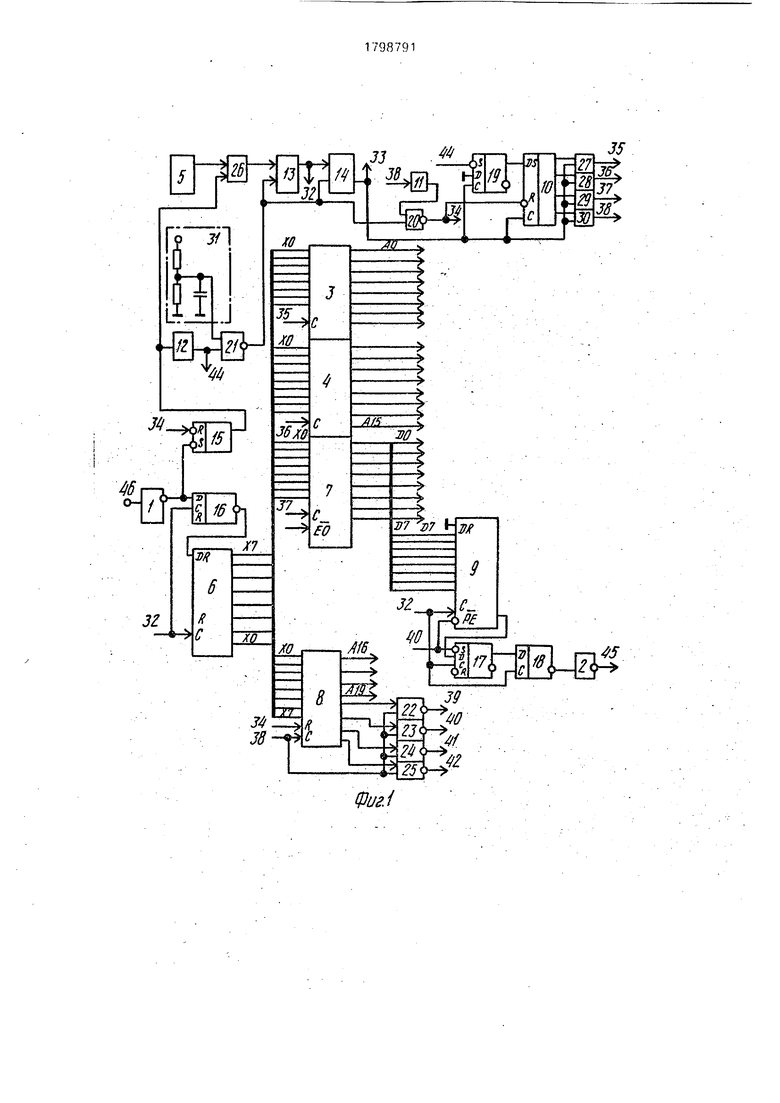

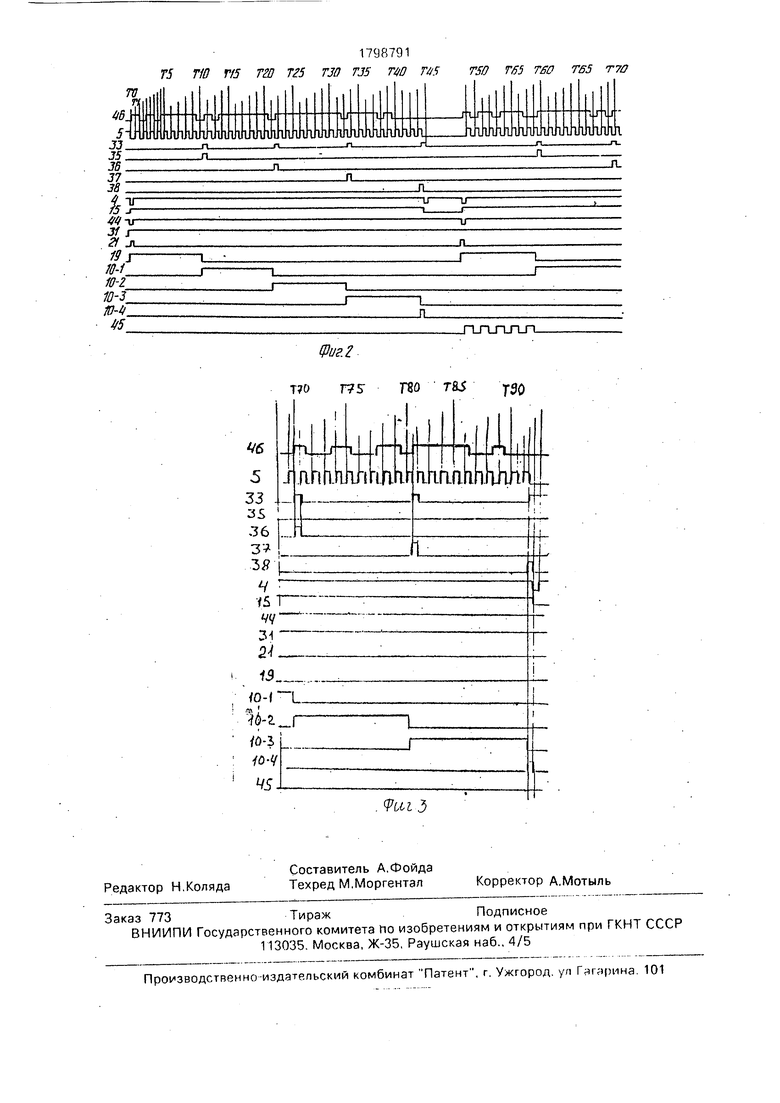

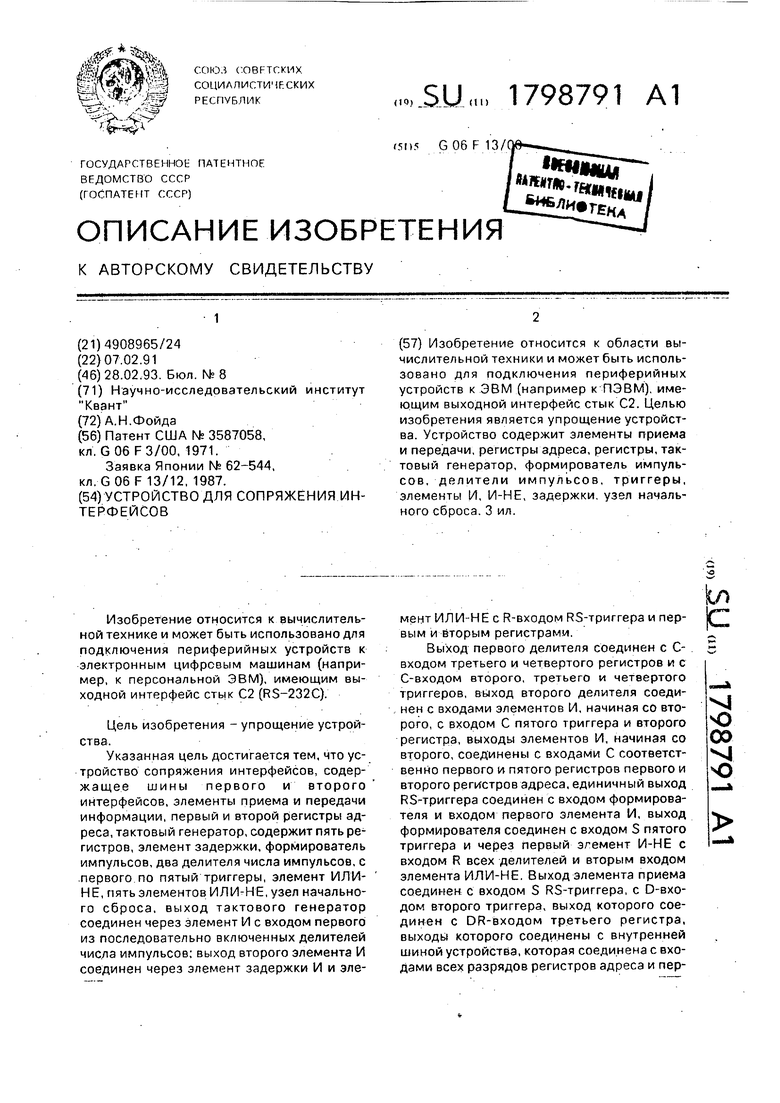

Структурная схема устройства представлена на фиг.1; временная диаграмма - на фиг.2 и 3.

Устройство сопряжения интерфейсов содержит элементы .приема 1 и передачи 2 информации, первый и. второй регистры ад- . реса 3 и 4, тактовый генератор 5, регистры 6-10, элемент задержки 11, формирователь импульсов 12. делители числа импульсов 13, 14, триггеры 15-19, элемент ИЛИ-НЕ 20, пять элементов И-НЕ 21-25,и И 26-30, узел начального сброса 31.

Выход тактового генератора соединен 5 через элемент И 26 с входом первого делителя числа импульсов 13, выход второго элемента И 30 соединен через элемент задержки 11 и элемент ИЛИ-НЕ 20 с входами сброса триггера 15 и регистров 8, 10, выход 32 первого делителя 13 соединен с синхровходами третьего 6 и четвертого 9 регистров и второго 16, третьего 17 и четвертого 18 триггеров, выход 33 второго делителя 14 соединен с входами элементов И 27-30, с синхровходами пятого триггера 19 и второго регистра 10, выходы 35-38 элементов И 27-30 соединены с синхровходами соответственно регистров 3, 4, 7, 8, единичный выход триггера 15 соединен с входом формирователя 12 и входом элемента И 26, выход 44 формирователя 12 соединен с входом S триггера 19 и через элемент И-НЕ 21 с входом сброса делителей 13, 14 и вторым входом элемента ИЛИ-НЕ 20, выход элемента приема 1 соединен с входом триггера 15, с входом триггера 16, выход которого соединен с входом регистра 6, выходы которого соединены с входами всех разрядов регистров адреса 3, 4 и регистров 7, 8; выходы регистров адреса 3, 4 и четыре младших разряда регистра 8 поступают на шины адреса второго интерфейса, выходы регистра .7 и входы регистра 9 поступают на шины данных второго интерфейса, выходы старших разрядов регистра 8 поступают через элементы И-НЕ 22-25 на шины 39-42 управляющих сигналов второго интерфейса: выход узла начального сброса 3.1 соединен с входом элемента И-НЕ 21, выход старшего разряда регистра 9 соединен со входом триггера 17,.выход которого соединен с входом триггера 18, инверсный выход которого соединен с входом элемента передачи, выход которого соединен с выходом 45 устройства, вход элемента приема соединен с входом 46 устройства, выход 40 элемента И-НЕ 23 соединен с входом установки в единицу триггера и с входом разрешения приема параллельного кода в регистр 9, выход 41 элемента И-НЕ 24 соединен с входом перевода в третье состояние регистра 7, выход триггера 19 соединен с входом регистра 10, выходы которого соединены с входами элементов И 27-30.

Устройство работает следующим образом.

При включении питающего напряжения (см; фиг. 1-3) на вход элемента И-НЕ 21 поступает с узла начального сброса 31 отрицательный импульс и на выходе элемента 21 . появляется высокий потенциал, который устанавливает в ноль делители 13. 14 и регистры 8. 10. При приход о но вход 46

устройства первого стартового импульса (момент 10, положительный импульс) на выходе элемента 1 появляется низкий уровень, который устанавливает триггер 15 в единичное состояние. По переднему фронту положительного перепада на своем входе срабатывает формирователь 12, на выходе которого появляется узкий отрицательный импульс, который устанавливает в единицу триггер 19, а также, пройдя через элемент 21, устанавливает делители числа импульсов 13, 14 в нулевое состояние и, пройдя через элемент 20, подтверждает состояние ноль регистров 8, ТО. Высокий потенциал с выхода триггера 15, поступая на вход элемента 26, разрешает прохождение через этот элемент импульсов с генератора 5 на вход делителя 13. Делитель 13 начинает считать импульсы. После появления на выходе, делителя 13 в момент Т1 положительного импульса он поступает на вход С триггера 16 и регистра 6 и по переднему фронту импульса в триггер 16 запоминается первый разряд кода (стартовый бит). Затем в момент Т2 по переднему фронту положительного импульса на выходе делителя 13 происходит перезапись информации с триггера 16 в младший разряд регистра 6 и прием следующего бита в триггер 16 (первый информационный бит), т.е. при появлении на выходе делителя 13 каждого следующего импульса следующий бит информации запоминается в триггере 16, а предыдущий переписывается в регистр 6 и сдвигается в нем на один разряд от младших разрядов к старшим. При появлении на выходе делителя 13 10-го импульса в регистре 6 будут 8 бит информации (предположим, что использован для передачи по интерфейсу стык С2 асинхронный режим работы с длиной слова 8 бит без контроля на четность - нечетность).

Предположим, что необходимо считать код с ячейкой памяти адреса 0105Н, а затем в эту ячейку послать код 89Н (буква Н указывает, что код шестнадцатиричный). В этом случае в момент Т10 в регистре 6 будет находится код РАН, инверсный коду 05Н, так как на шины адреса и данных (как в стандартном интерфейсе И 41) код выдается в инверсном виде (младшие 8 разрядов адреса ячейки). После того как на выходе делителя 13 окончится десятый импульс (момент Т11), появляется первый положительный импульс на выходе делителя 14, который поступает на синхровход триггера 19 и регистра 10 и на элементы 27-30. На выходе 35 появляется положительный импульс, который разрешает прием кода 05 с выхода регистра 6 в регистр 3. Затем в следующие моменты времени (с Т11 по Т21) приходящий на вход 46 последовательный код FEH. инверсный коду 01 Н (старшие разряды адреса), запоминается в регистре 6. После того, как на выходе делителя 13 окончится 20-й импульс, на выходе делителя 14 в момент Т22 появляется второй положительный импульс, который, пройдя через элемент 29 (так как на втором входе элемен0 та 29 в этот момент высокий потенциал), разрешает прием кода FEH с выхода регистра 6 в регистр 4.

Затем аналогично в промежутки времени с Т23 по Т32 запоминается последова5 тельный код FFH, инверсный коду 00 (код третьего байта при режиме чтения безразличен), в.регистр 6, а затем он переписывается в регистр 7.

Затем аналогично в момент времени с

0 Т34 по Т43 запоминается в регистре 6 последовательный код 2FH, приходящий на вход 46. В четвертом байте передаются старшие разряды адреса и сигналы управления. По окончании сорокового импульса на выходе

5 делителя 13 момент Т44 появляется четвертый положительный импульс на выходе делителя 14, который, пройдя через элемент 30, разрешает прием кода 2ГН с выхода регистра 6 в регистр 8, а также выдачу через

0 элемент 24 управляющего сигнала чтения. Таким образом, е момент Т44 на шину 40 выдэется отрицэтельный импульс, который устанавливает в единицу триггер 18 и по которому принимается код с шин данных

5 периферийного устройства в регистр 9,

Передача принятого кода например55Н происходит при приеме следующих 10 импульсов на вход 46 (первый стартовый, восемь информационных и один стоповый

0 бит).

Предположим, необходимо затем выдать код ЗЗН (инверсный ему ССН) в ту же ячейку с адресом 0105Н, то тогда вначале аналогично последовательно посылаются

5 младшие разряды адреса (момент Т49-Т59), старшие разряды адреса (Т59-Т70), данные (Т70-Т8Т), код в четырех младших разрядах которого самые старшие разряды адреса, а в четырех старших разрядах - 4 (момент

0 Т81-Т). Код 4 в самых старших разрядах 4-го байта указывает, что выполняется режим записи. Передача кода с периферийного устройства, принятого в устройство в момент Т44, по интерфейсу 1/141 происходит в мо5 ментТ49-Т60.

На фиг.2 и 3 цифрами 10-1, 10-2 , 10-3 10-4 обозначены выходы различных разрядов -регистра 10.

Вход регистра 9 и вход триггера 19 подключены к шине корпуса и поэтому при приходе на вход с этих устройств тактовых импульсов заносится последовательно код нуля.

Формула изобретения Устройство для сопряжения интерфейсов, содержащее шины первого и второго интерфейсов, элементы приема и передачи информации, первый и второй регистры адреса, тактовый генератор,о тличающее- с я тем, что, с целью упрощения, оно содержит пять регистров, элемент задержки, формирователь импульсов, два делителя числа импульсов, пять триггеров, элемент ИЛИ- НЕ, пять элементов И-НЕ и пять элементов И, узел начального сброса, выход тактового генератора соединен с первым входом первого элемента И, выход которого соединен с входом первого делителя числа импульсов, выход второго элемента И соединен через элемент задержки с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с входами сброса первого триггера, первого и второго регистров, выход первого делителя числа импульсов соединен с синхровходами третьего и четвертого регистров, второго, третьего и четвертого, триггеров, выход второго делителя числа импульсов соединен с первыми входами с второго по пятый элементов И, синхровхо- дом пятого триггера и второго регистра,выходы с второго rio пятый элементов И соединены с синхровходами соответственно первого, пятого регистров, первого и второго регистров адреса, единичный выход первого триггера соединен с входом формирователя импульсов и вторым входом первого элемента И, выход формирователя импульсов соединен с установочным входом пятого триггера и первым входом первого элемента И-НЕ, выход которого

соединен с входом сброса первого и второго делителей числа импульсов и вторым входом элемента ИЛИ-НЕ. выход элемента приема соединен с установочным входом

первого триггера, с входом данных второго триггера, выход которого соединен с входом данных третьего регистра, выходы которого соединены с входами данных первого и второго регистров адреса, первого и пятого ресистров, выходы первого и второго регистров адреса и четыре младших разряда первого регистра являются выходом адреса устройства, выходы пятого и входы данных четвертого регистров являются входом-выходом данных устройства, выходы старших разрядов первого регистра соединены с первыми входами с второго по пятый элементов И-НЕ, выходы которых являются выходами управляющих сигналов устройства, выход узла начального сброса соединен с вторым входом первого элемента И-НЕ, выход старшего разряда четвертого регистра соединен с входом данных третьего триггера, выход которого соединен с входом

данных четвертого триггера, инверсный выход которого соединен с входом элемента передачи, выход которого соединен с выходом данных устройства, вход элемента приема соединен с входом данных устройства,

выход третьего элемента И-.НЕ соединен с входом установки в 1 третьего триггера и с входом разрешения приема параллельного кода четвертого регистра, выход четвертого элемента И-НЕ соединен с входом

перевода в третье состояние пятого регистра, выход пятого триггера соединен с входом данных второго регистра, выходы которого соединены с вторыми входами с второго по пятый элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения интерфейсов | 1989 |

|

SU1817097A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ИНТЕРФЕЙСОВ | 1990 |

|

RU2022345C1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

Изобретение относится к области вычислительной техники и может быть использовано для подключения периферийных устройств к ЭВМ (например к ПЭВМ), имеющим выходной интерфейс стык С2. Целью изобретения является упрощение устройства. Устройство содержит элементы приема и передачи, регистры адреса, регистры, тактовый генератор, формирователь импульсов, делители импульсов, триггеры, элементы И, И-НЕ, задержки, узел начального сброса.3 ил.

| Патент США N° 3587058, кл, G06 F3/00, 1971 | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1991-02-07—Подача