Изобретение относится к запоминающим устройствам и может быть использовано, в частности, в системах параллельной обработки информации.

Известно запоминающее устройство с одновременной выборкой нескольких слов, содержащее матрицу из m запоминающих элементов, адресный блок выборки, n регистров направлений выбора, первую группу n˙m элементов И, адресный блок записи, триггеры сбоя, регистр направлений записи, вторую и третью группы элементов И, причем первые входы элементов И первой группы подключены к выходам соответствующих запоминающих элементов, вторые входы элементов И первой группы соединены с выходами адресного блока выборки, выходы элементов И первой группы подключены к соответствующим входам регистров направлений выборки, первые входы элементов И второй группы подключены к выходам адресного блока записи, вторые входы элементов И второй группы соединены с выходами адресного блока выборки, выходы элементов И второй группы подключены к входам триггеров сбоя, выходы которых являются управляющими выходами устройства, информационными выходами которого являются выходы регистров направлений выборки, первые входы элементов И третьей группы соединены с выходами регистра направлений записи, вторые входы элементов И третьей группы подключены к выходам адресного блока записи, а выходы элементов И третьей группы соединены с одним из входов соответствующих запоминающих элементов, входы адресного блока выборки адресного блока записи и регистра направлений записи являются соответствующими входами устройства.

В этом устройстве не предусмотрена возможность организации повторного считывания информации при возникновении конфликта (обращение к одной и той же ячейке памяти на выборку по одному направлению и одновременно на запись по другому).

Целью изобретения является расширение области применения устройства за счет организации повторного считывания информации.

Цель достигается тем, что в запоминающее устройство с одновременной выборкой нескольких слов, содержащее матрицу m запоминающих элементов, адресный блок выборки, n регистров направлений выбора, первую группу n˙m элементов И, адресный блок записи, триггеры сбоя, регистр направлений записи, вторую и третью группы элементов И, причем первые входы элементов И первой группы подключены к выходам соответствующих запоминающих элементов, вторые входы элементов И первой группы соединены с выходами адресного блока выборки, выходы элементов И первой группы подключены к соответствующим входам регистров направлений выборки, первые входы элементов И второй группы подключены к выходам адресного блока записи, вторые входы элементов И второй группы соединены с выходами адресного блока выборки, выходы элементов И второй группы подключены к входам триггеров сбоя, выходы которых являются управляющими выходами устройства, информационными выходами которого являются выходы регистров направлений выборки, первые входы элементов И третьей группы соединены с выходами регистра направлений записи, вторые входы элементов И третьей группы подключены к входам адресного блока записи, а выходы элементов И третьей группы соединены с одним из входов соответствующих запоминающих элементов, входы адресного блока выборки адресного блока записи и регистра направлений записи являются соответствующими входами устройства, введены элемент ИЛИ, формирователь импульсов, группа элементов задержки и четвертая группа элементов И, выходы которых соединены с соответствующими входами повторного считывания адресного блока выборки и входами соответствующих элементов задержки, выходы которых соединены с нулевыми входами соответствующих триггеров сбоя, выходы которых соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых объединены и соединены с выходом формирователя импульсов, вход которого соединен с выходом элемента ИЛИ, входы которого соединены с соответствующими выходами адресного блока записи.

Введение указанных элементов и соответствующих связей позволяет повысить достоверность функционирования устройства при возникновении конфликтов за счет повторного считывания информации. В других известных технических решениях отсутствуют подобные признаки в их общей совокупности, поэтому заявляемый объект соответствует критерию "существенные отличия". Наличие существенных отличий приводит к положительному эффекту, так как, исключая любой элемент или связь, нельзя достичь поставленной цели.

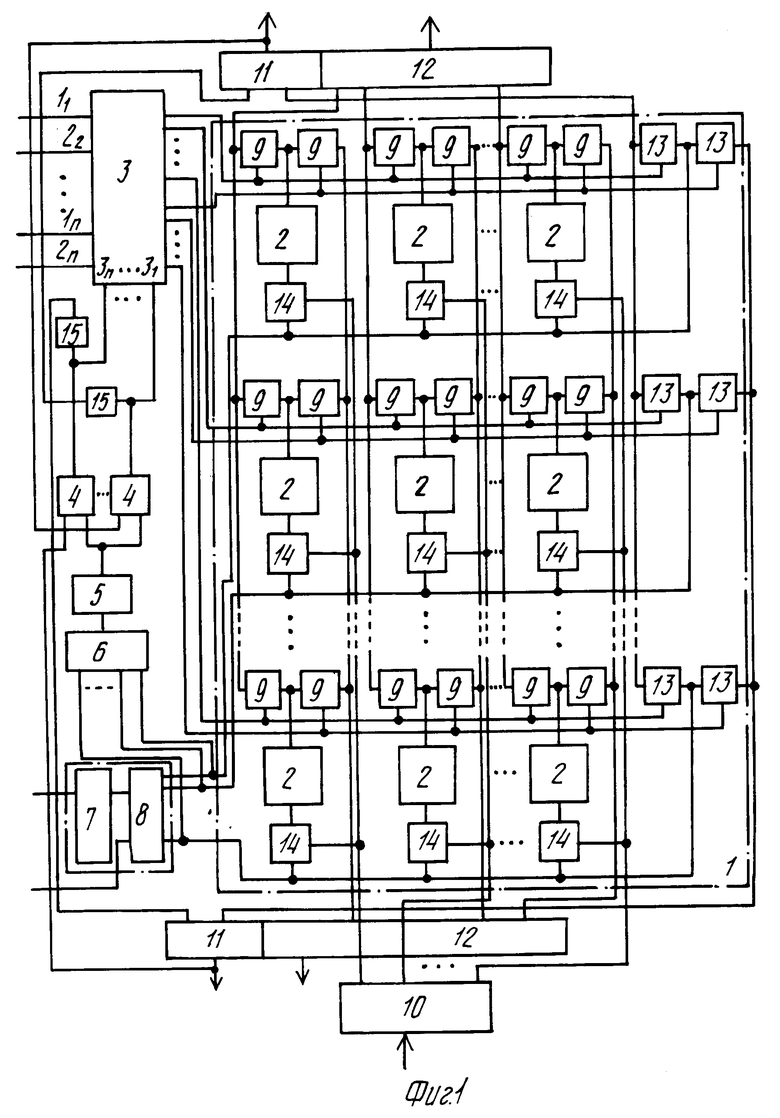

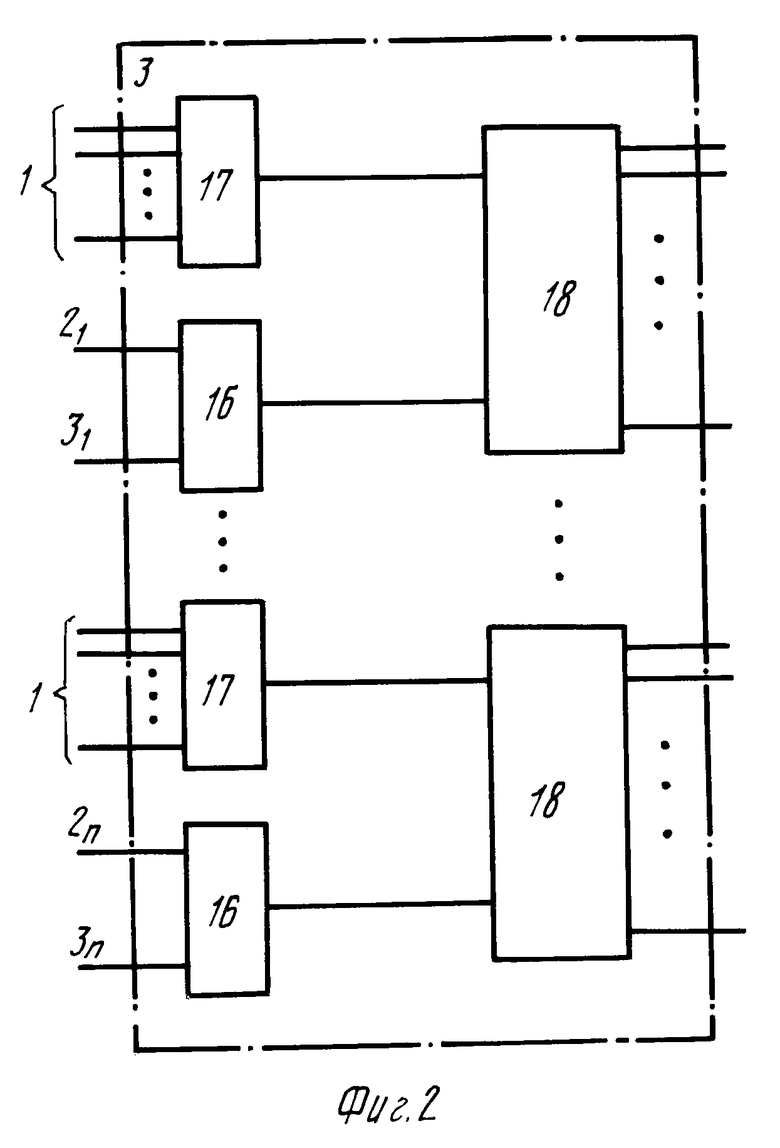

На фиг. 1 представлена функциональная схема запоминающего устройства с одновременной выборкой нескольких слов при n=2; на фиг.2 - функциональная схема адресного блока выборки.

Устройство содержит матрицу 1 из m запоминающих элементов 2, образующих k ячеек памяти, каждая из которых состоит из m/k разрядов, адресный блок 3 выборки, четвертую группу элементов И 4, формирователь 5 импульсов по заднему фронту, элемент ИЛИ 6, регистр 7 адреса записи, дешифратор 8 адреса записи, первую группу из n m элементов И 9, регистр 10 направления записи, триггеры 11 сбоя, n регистров 12 направлений выборки, вторую группу из k n элементов И 13, третью группу из m элементов И 14 и n элементов 15 задержки.

Адресный блок 3 выборки (фиг.2) содержит n групп элементов ИЛИ 16, n регистров 17 адреса выборки, n дешифраторов 18 адреса выборки.

Выходы n элементов 15 задержки соединены с нулевыми входами соответствующих триггеров 11 сбоя, выходы которых соединены с соответствующими выходами устройства и первыми входами соответствующих элементов И 4 четвертой группы. Вторые входы элементов И 4 объединены и объединены с выходом формирователя 5 импульсов по заднему фронту, вход которого соединен с выходами элементов ИЛИ 6. Входы элементов ИЛИ 6 соединены с соответствующими выходами дешифратора 8 адреса записи, информационные входы которого соединены с выходами регистра 7 адреса записи. Парафазные входы регистра 7 соединены с выходами адреса записи устройства, управляющий вход записи которого соединен с управляющим входом дешифратора 8 адреса записи. Каждый выход дешифратора 8 соединен с объединенными первыми входами элементов И каждой ячейки памяти элементов И второй 13 и третьей 14 групп элементов И, вторые входы элементов И 14 третьей группы каждого разряда объединены и соединены с выходами соответствующего разряда регистра 10 направлений записи, информационный вход которого соединен с информационным входом устройства. Парафазные адресные входы устройства соединены с одноименными входами блока 3 выборки, входы повторного считывания которого соединены с выходами соответствующего элемента И 4 четвертой группы и входами соответствующих элементов задержки. Каждый выход соответствующего направления выборки блока 3 выборки соединен с первыми входами элементов И 9 всех разрядов каждой ячейки памяти соответствующего направления выборки первой группы элементов И и вторым входом элемента И 13 каждой ячейки памяти соответствующего направления второй группы элементов И. Выход каждого элемента И 14 третьей группы элементов И соединен с входом соответствующего запоминающего элемента 2 матрицы 1, выход которого соединен с вторыми входами соответствующих элементов И, объединенных по направлениям выборки. Выходы элементов И 9 каждого разряда всех k ячеек памяти первой группы элементов И соответствующего направления выборки через эмиттерные повторители с открытым эмиттером объединены по схеме монтажного ИЛИ и соединены с входом отдельно каждого разряда регистра 12 соответствующего направления выборки, выходы которого соединены с соответствующими информационными выходами устройства. Управляющие входы считывания устройства соединены с соответствующими одноименными входами блока 3 выборки, выходы всех элементов И 13 второй группы каждого направления через эмиттерные повторители с открытым эмиттером объединены по схеме монтажного ИЛИ и соединены с единичным входом триггера 11 сбоя соответствующего направления. Объединение выходов элементов И через эмиттерные повторители с открытым эмиттером по схеме монтажного ИЛИ исключает влияние их друг на друга [2].

В адресном блоке 5 выборки выход элемента ИЛИ 16 соединен с управляющим входом дешифратора 18, информационные входы которого соединены с выходами регистра 17 адреса выборки. Парафазные входы регистра 17 соединены с адресными входами соответствующего направления блока, входы первичного и повторного считывания соответствующего направления которого соединены соответственно с первым и вторым входами элемента ИЛИ 16. Выходы блока соединены с выходами дешифратора 18 соответствующего направления.

Запоминающее устройство работает следующим образом.

Перед началом работы регистр 7 адреса записи, регистр 10 направления записи, триггер 11 сбоя, регистр 12 направлений выборки и регистр 17 адреса выборки устанавливаются в нулевое состояние. Триггеры 11 сбоя сбрасываются в нулевое состояние по окончании каждого повторного считывания.

На вход устройства поступают сигналы считывания или записи, адрес чтения или записи и информация, которую необходимо записать. С выхода устройства выдаются считанная по соответствующему направлению информация и сигнал о конфликте с триггера сбоя соответствующего направления.

Выборка информации осуществляется независимо друг от друга по каждому из n направлений, а запись - по одному направлению. Пpи записи информации в устройство адрес записывается в регистр 7 адреса записи, а в регистре 10 направления записи находится записываемая информация. По сигналу записи, поступающему на управляющий вход дешифратора 8 адреса записи, выдается сигнал записи в одну из ячеек памяти матрицы 1 через элементы И 14, в результате чего информация с регистра 10 направления записи переписывается в запоминающие элементы 2 в течение времени действия сигнала на выходе дешифратора 8 адреса записи.

Выборка информации осуществляется по исполнительным сигналам считывания, поступающим на первый вход элемента ИЛИ 16 адресного блока 3. При этом дешифратор 18 адреса выборки по коду, находящемуся в регистре 17 адреса выборки, формирует сигнал на один из своих k выходов, который через первую группу элементов И 9 передает информацию из запоминающих элементов 2 матрицы 1 в регистр 12 направлений выборки соответствующего направления, причем адреса выборки и сигналы считывания могут поступить одновременно по нескольким направлениям. Например, поступили адреса в регистр 17 первого и второго направлений. При поступлении сигналов считывания на входы 2 адресного блока 3 выборки на одном из выходов первого и второго дешифраторов формируются сигналы (если адреса одинаковые, то сигналы сформированы на одноименных выходах дешифратора 18), которые поступают на первые входы элементов И 9 первой группы элементов И разных ячеек или одной и той же ячейки памяти с первого и второго направлений. На вторые входы этих элементов И поступают разряды считываемого слова с выходов запоминающих элементов 2. Разряды считываемого слова через элементы И 9 поступают на регистры 12 направлений выборки первого (через левые элементы И) и второго (через правые элементы И) направлений выборки. Считанные слова из регистров 12 направлений выборки выдаются на выход устройства.

Если в течение времени выборки из некоторой ячейки происходит запись в эту же ячейку новой информации, то прочитанная в регистр 12 направлений выборки информация оказывается искаженной, в этом случае на входы элемента И 13 соответствующего направления поступает одновременно два сигнала: считывания с одного из выходов адресного блока 3 выборки и записи с одного из выходов дешифратора 8 адреса записи. Сигнал с выхода элемента И 13 устанавливает триггер 11 сбоя соответствующего направления, в которое должна считываться информация, в единичное состояние.

Сигнал с выхода триггера 11 сбоя того направления, в котором произошел конфликт, выдается на выход устройства и далее потребителю информации как признак того, что считанное слово оказалось искаженным, и открывает соответствующий элемент И 4 четвертой группы элементов И по первому входу. На вторые входы всех элементов И 4 четвертой группы поступает сигнал повторного считывания, который формируется в формирователе импульсов по заднему фронту импульсов, поступающих с выходов дешифратора 8 адреса записи на входы элемента ИЛИ 6. Сигнал повторного считывания через открытый элемент И 4 четвертой группы элементов И поступает на второй вход соответствующего элемента ИЛИ 16 адресного блока 3 выборки. По этому сигналу с соответствующего дешифратора 18 адреса выборки на запоминающие элементы 2 матрицы 1 поступает сигнал повторного считывания. В результате в регистр 12 направлений выборки с выхода запоминающих элементов 2 занесена вновь записанная информация. После этого триггер 11 сбоя соответствующего направления устанавливается в нулевое состояние сигналом с выхода соответствующего направления, задержанным в элементе задержки на время считывания информации из запоминающих элементов 2 и передачи информации в регистр 12 соответствующего направления выборки. Нулевое состояние триггера 11 сбоя свидетельствует о том, что считанная информация оказывается неискаженной и может быть принята потребителем.

Таким образом, введенные в запоминающее устройство новые элементы позволяют осуществлять независимую запись и выборку достоверной информации по нескольким направлениям за счет фиксации достоверности выбираемой информации и ее исправления путем повторного считывания при возникновении конфликтов. Такая организация работы запоминающего устройства повышает достоверность его функционирования и быстродействие, так как нет необходимости тратить время на анализ и предотвращение конфликтных ситуаций, число которых составляет незначительную часть от общего числа обращений на запись и еще меньшую часть от общего числа обращений на выборку. Восстановление недостоверно считанной информации путем повторного считывания незначительно увеличивает время выборки по сравнению с любыми другими способами разрешения конфликтных ситуаций. Это позволяет существенно расширить функциональные возможности устройства, особенно при построении многопроцессорных вычислительных комплексов, допуская независимую запись и выборку информации различными процессорами.

Предлагаемое устройство рассчитано на работу с однотипными процессорами, работающими синхронно и имеющими одинаковые или кратные времени считывания циклы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с одновременной выборкой нескольких слов | 1981 |

|

SU970464A2 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля перепрограммируемых блоков постоянной памяти | 1988 |

|

SU1547034A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1984 |

|

SU1840542A2 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Устройство для контроля хода программы | 1986 |

|

SU1328819A2 |

Изобретение относится к запоминающим устройствам и может быть использовано, в частности, в системах параллельной обработки информации. Целью изобретения является расширение области применения устройства за счет организации повторного считывания информации. Устройство содержит матрицу запоминающих элементов, адресный блок выборки, адресный блок записи, регистры направлений с триггерами сбоя, формирователь импульсов, элемент ИЛИ, регистр направлений записи, группу элементов задержки и четыре группы элементов И. Запоминающее устройство позволяет осуществлять выборку информации независимо друг от друга по некольким направлениям, а запись - по одному направлению. При одновременном считывании и записи по одному направлению осуществляется повторное считывание. 2 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ ВЫБОРКОЙ НЕСКОЛЬКИХ СЛОВ, содержащее матрицу из m запоминающих элементов, адресный блок выборки, n регистров направлений выбора, первая группа n · m элементов И, адресный блок записи, триггеры сбоя, регистр направлений записи, вторая и третья группы элементов И, причем первые входы элементов И первой группы подключены к выходам соответствующих запоминающих элементов, вторые входы элементов И первой группы соединены с выходами адресного блока выборки, выходы элементов И первой группы подключены к соответствующим входам регистров направлений выборки, первые входы элементов И второй группы подключены к выходам адресного блока записи, вторые входы элементов И второй группы соединены с выходами адресного блока выборки, выходы элементов И второй группы подключены к входам триггеров сбоя, выходы которых являются выходами устройства, первые входы элементов И третьей группы соединены с выходами регистра направлений записи, вторые входы элементов И третьей группы подключены к выходам адресного блока записи, а выходы элементов И третьей группы соединены с одним из входов соответствующих запоминающих элементов, входы адресного блока записи и регистра направлений записи являются одними из входов устройства, отличающееся тем, что, с целью расширения области применения устройства за счет организации повторного считывания информации, в него введены элемент ИЛИ, формирователь импульсов, группа элементов задержки и четвертая группа элементов И, выходы которых соединены с соответствующими входами повторного считывания адресного блока выборки и входами соответствующих элементов задержки, выходы которых соединены с нулевыми входами соответствующих триггеров сбоя, выходы которых соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых объединены и соединены с выходом формирователя импульсов, вход которого соединен с выходом элемента ИЛИ, входы которого соединены с соответствующими выходами адресного блока записи.

| Запоминающее устройство с одновременной выборкой нескольких слов | 1981 |

|

SU970464A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-10-30—Публикация

1990-11-15—Подача