Изобретение относится к запоминающим устройствам и может быть использовано, в частности в системах napaiiлельной обработки информации.

По основному авт.св. № 542241 известно запоминающее устройство с одновременной выборкой нескольких слов, содержащее матрицу из m запоминающих элементов, адресный блок, п регистров направлении выборки и плт элементов И, первые входы которых подключены к выходам соответствующих запоминающих элементов, вторые - к выходам ъцресного блока, а выходы - к соотЬетствующим входам регистров направлений выборки.

В этом устройстве не предусматривается разрешение конфликтных ситуаций, возникающих при обращении к и той же ячейке памяти на выборку по ,одной магистрали и одновременно на запись информации по другой. В такой ситуации считывается искажен:ное слово, представляющее собой,как правило, поразрядную дизъюнкцию предыдущего и последующего записанных слов. Это снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с одновременной выборкой нескольких слов , введены адресный блок записи, триггеры сбоя, регистр направлений записи и две группы элементов И, причем первые входы элементов И первой группы подключены к выходам адресного блока записи, вторые - к выходам ад10ресного блока, а выходы - ко входам

триггеров сбоя, выходы которых ЯВ.Г1ЯЮТся выходами устройства, первые входы элементов И второй группы соединены с выходами регистра направлений за15писи, вторые - с выходами адресного блока записи, а выходы - с одним из входов соответствующих запоминающих элементов, входы адресного блока записи и регистра направлений записи

20 являются одними из входов устройства.

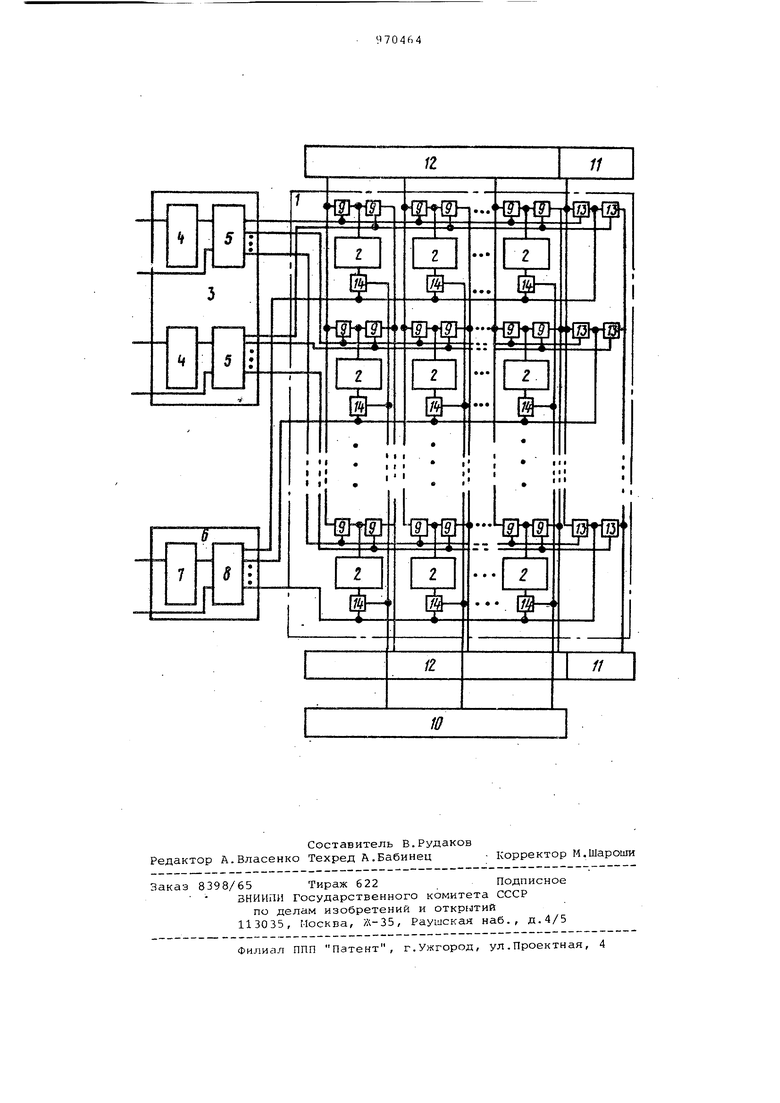

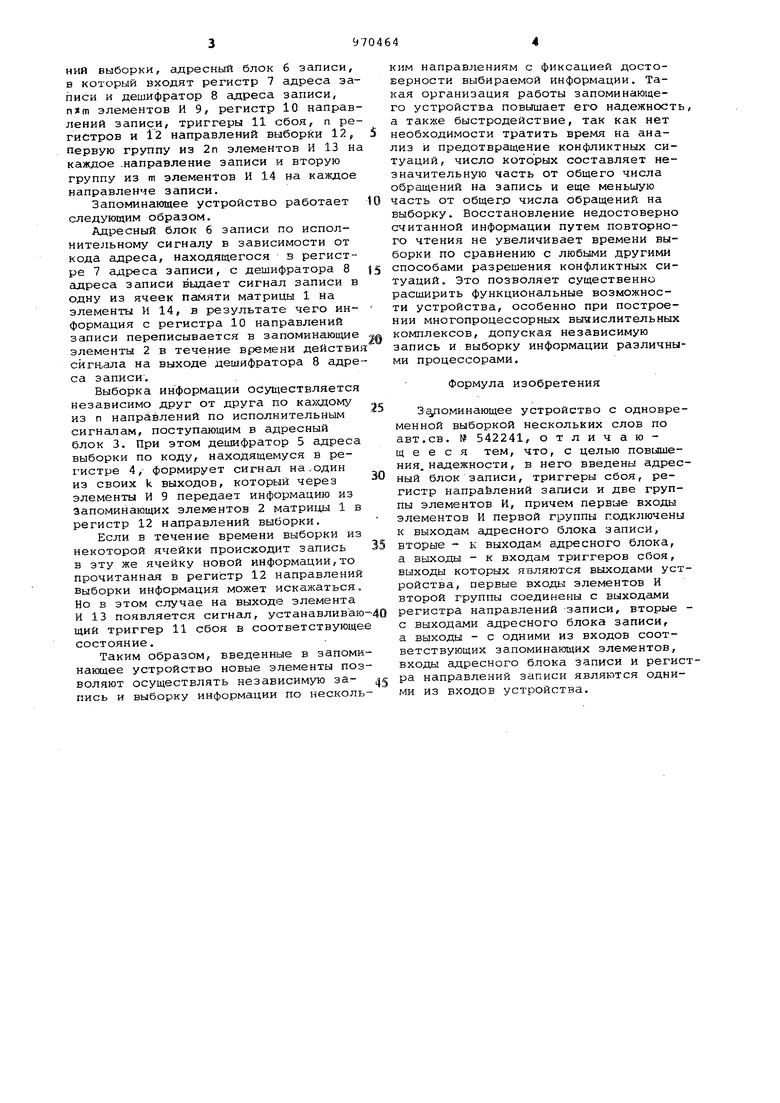

На чертеже изображена функциональная схема запоминающего устройства с одновременной выборкой нескольких слов.

Устройство содержит матрицу 1 из

25 m запоминающих элементов 2, образующих k ячеек памяти, адресный блок 3, в который, например, входят регистры 4 адреса выборки и дешифраторы 5 ад30реса выборки по количеству направлеНИИ выборки, адресный блок б записи, в который входят регистр 7 адреса записи и дешифратор 8 адреса записи, элементов И 9, регистр 10 направлений записи, триггеры 11 сбоя, п регистров и 12 направлений выборки 12, Первую группу из 2п элементов И 13 на каждое .направление записи и вторую группу из гл элементов И 14 на каждое направление записи. Запоминающее устройство работает следующим образом. Адресный блок б записи по исполнительному сигналу в зависимости от кода адреса, находящегося в регистре 7 адреса записи, с дешифратора 8 адреса записи выдает сигнал записи в одну из ячеек памяти матрицы 1 на элементы И 14, в результате чего информация с регистра 10 направлений записи переписывается в запоминающие элементы 2 в течение времени действи сигаала на выходе дешифратора 8 адре са записи . Выборка информации осуществляется Независимо друг от друга по каясдому из п направлений по исполнительным сигнапам, поступающим в адресный блок 3. При этом дешифратор 5 адреса выборки по коду, находящемуся в регистре 4, формирует сигнал на,один из своих k выходов, который через элементы И 9 передает информацию из Запоминающих элементов 2 матрицы 1 в регистр 12 направлений выборки. Если в течение времени выборки из некоторой ячейки происходит запись в эту же ячейку новой информации,то прочитанная в регистр 12 направлений Выборки информация может искажаться. Но в этом случае на выходе элемента И 13 появляется сигнал, устанавливаю щий триггер 11 сбоя в соответствующе состояние. Таким образом, введенные в запоми нающее устройство новые элементы поз воляют осуществлять независимую запись и выборку информации по несколь КИМ направлениям с фиксацией достоверности выбираемой информации. Такая организация работы запоминающего устройства повышает его надежность, а также быстродействие, так как нет необходимости тратить время на анализ и предотвращение конфликтных ситуаций, число которых составляет незначительную часть от общего числа обращений на запись и еще меньшую часть от общегр числа обращений на выборку. Восстановление недостоверно считанной информации путем повторного чтения не увеличивает времени выборки по сравнению с любыми другими способами разрешения конфликтных ситуаций. Это позволяет существенно расширить функциональные возможности устройства, особенно при построении многопроцессорных вычислительных комплексов, допуская независимую запись и выборку информации различными процессорами. Формула изобретения З оминающее устройство с одновременной выборкой нескольких слов по авт.св. № 542241, отличающееся тем, что, с целью повышения, надежности, в него введены адресный блок записи, триггеры сбоя, регистр направлений записи и две группы элементов И, причем первые входы элементов И первой группы подключены к выходам адресного блока записи, вторые - к выходам адресного блока, а выходы - к входам триггеров сбоя, выходы которых являются выходами устройства, первые входы элементов И второй группы соединены с выходами регистра направлений записи, вторые с выходами адресного блока записи, а выходы - с одними из входов соответствующих запоминающих элементов, входы адресного блока записи и регистра направлений записи являются одними из входов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ ВЫБОРКОЙ НЕСКОЛЬКИХ СЛОВ | 1990 |

|

RU2022371C1 |

| Запоминающее устройство | 1986 |

|

SU1336102A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU959166A1 |

| Запоминающее устройство с одновременным считыванием нескольких слов | 1986 |

|

SU1310899A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1989 |

|

SU1686453A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-08—Подача