Изобретение относится к вычислительной технике и может быть использовано для контроля при производстве перепрограммируемых постоянных запоминающих устройств.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства за счет выявления блоков памяти с ограниченной годностью, дефектов адресных дешифраторов, взаимного влияния элементов памяти.

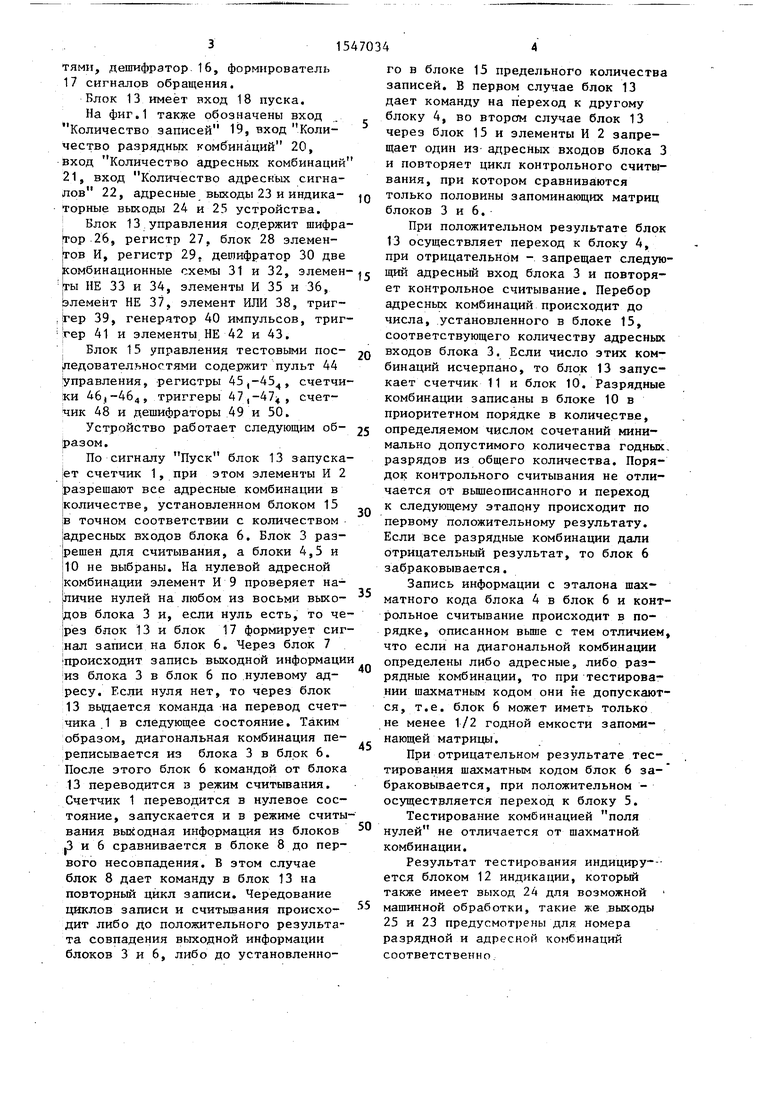

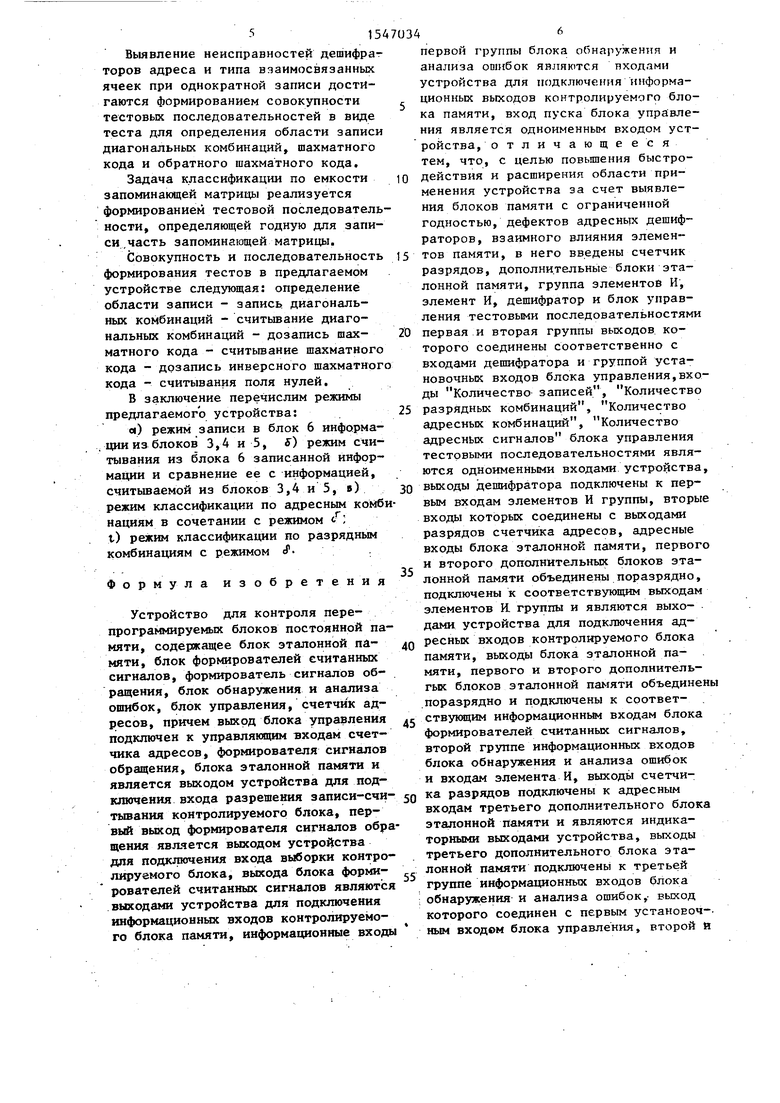

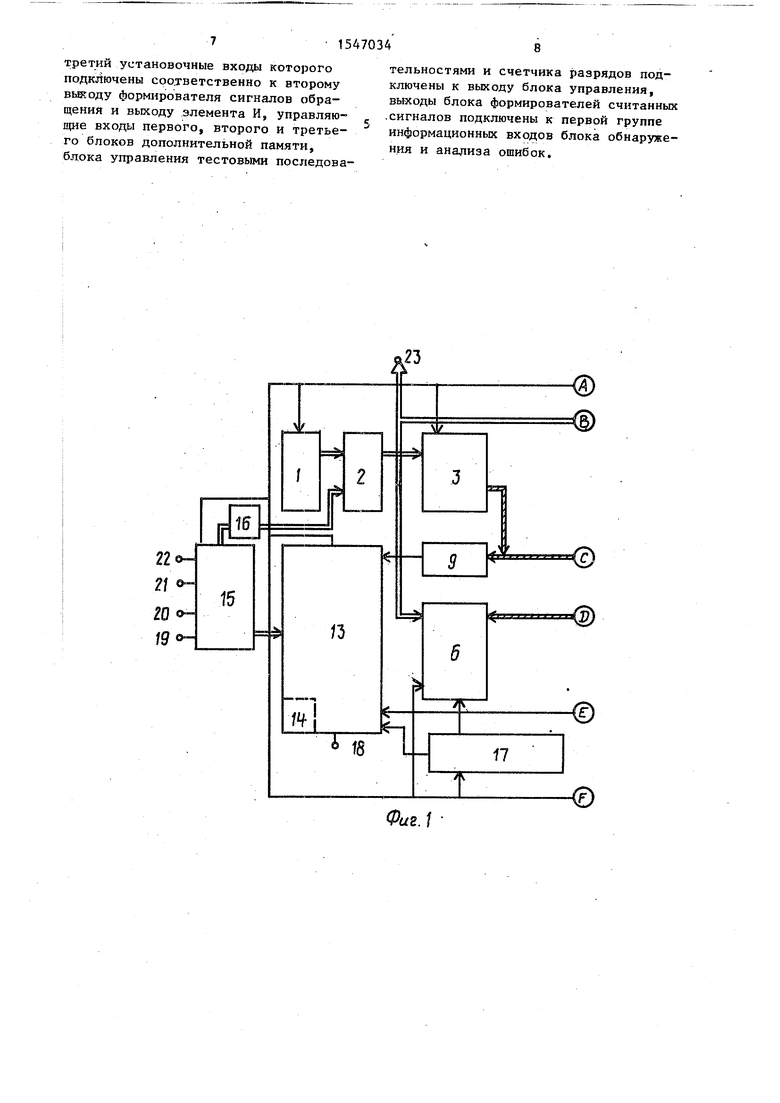

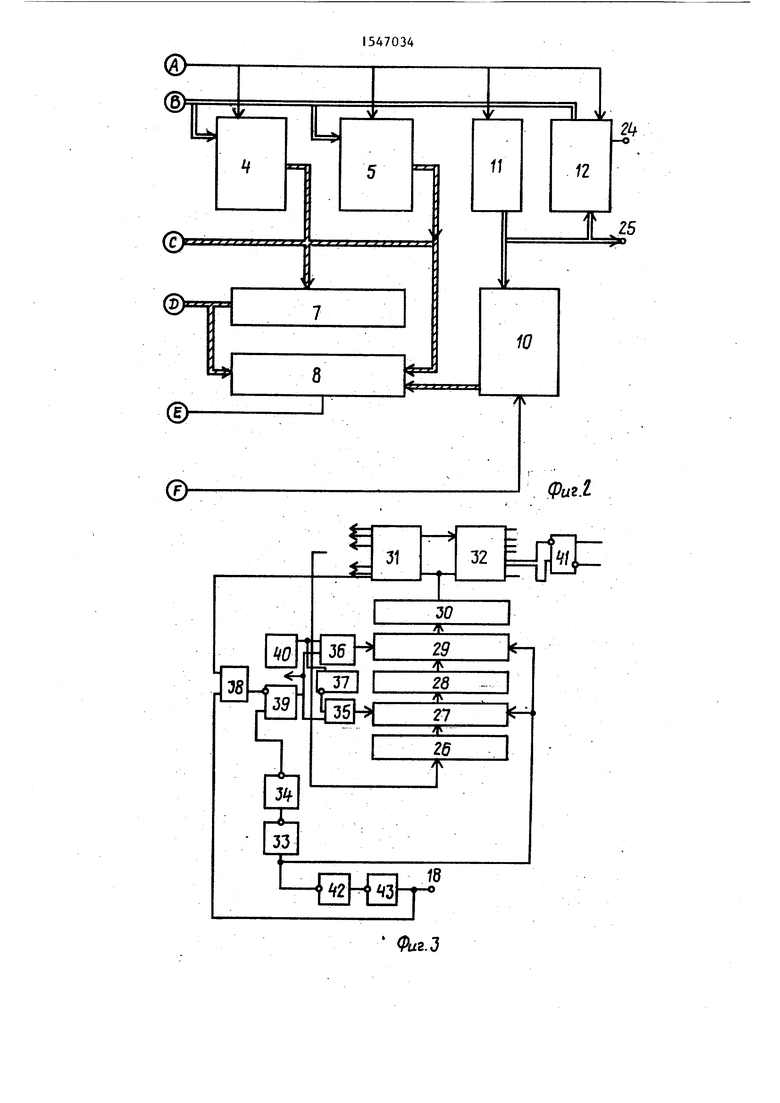

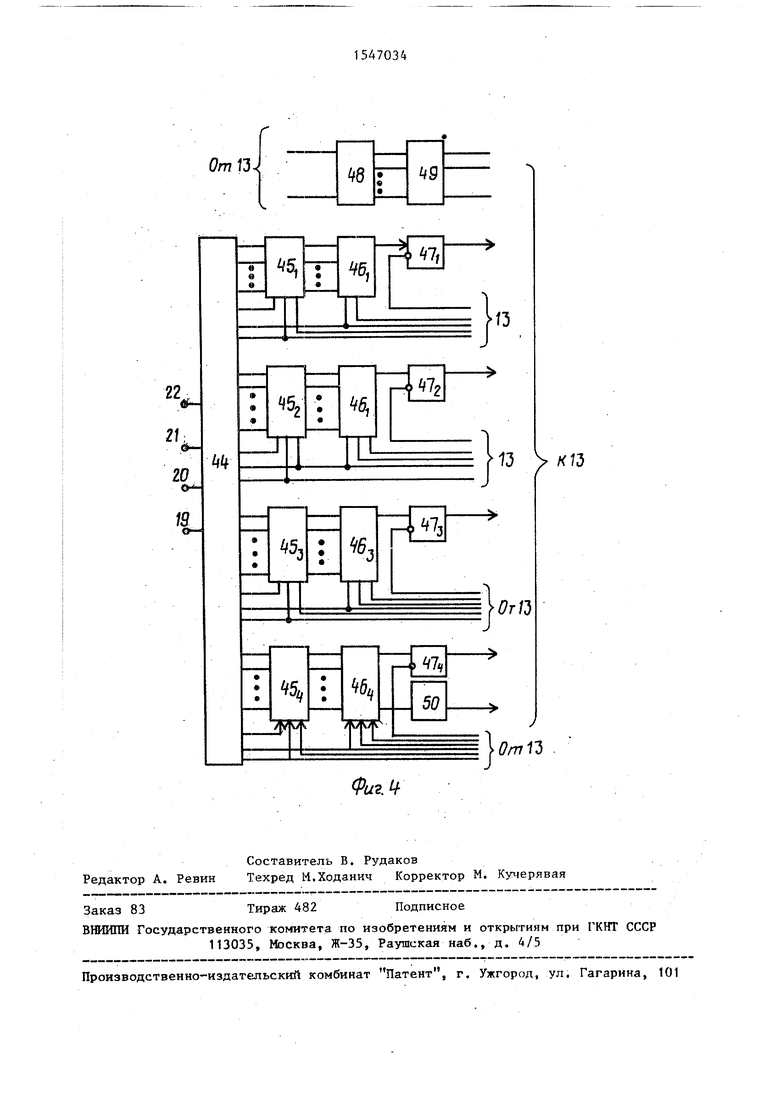

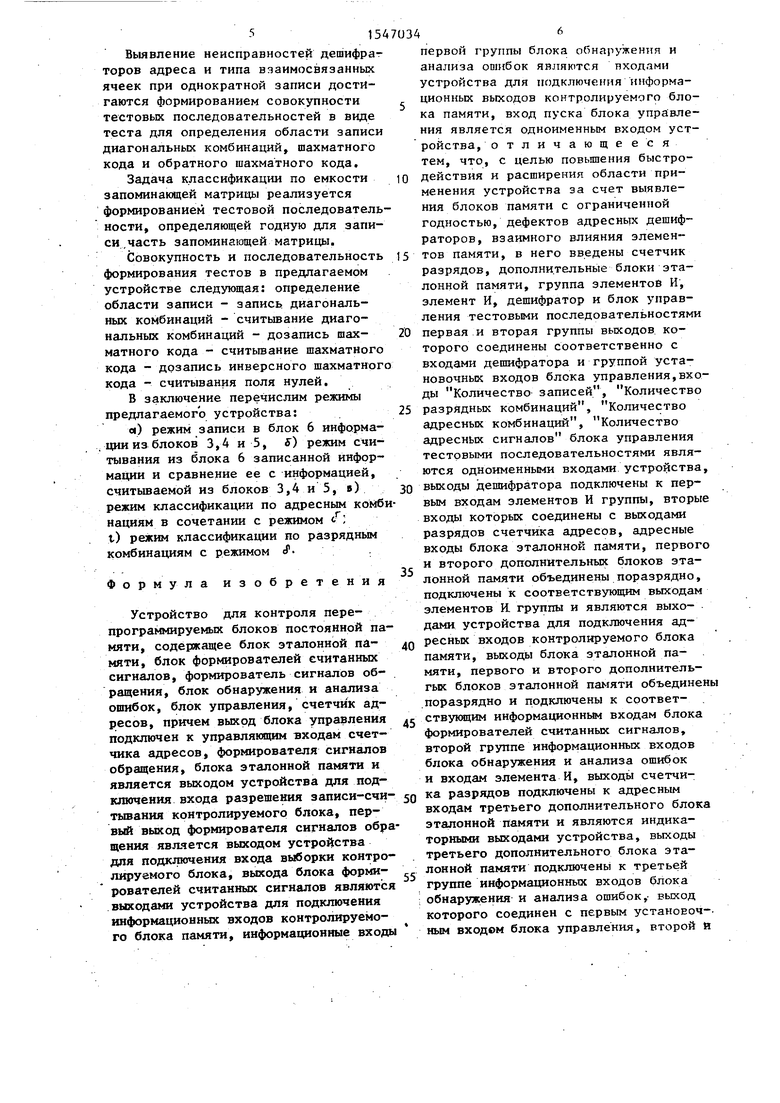

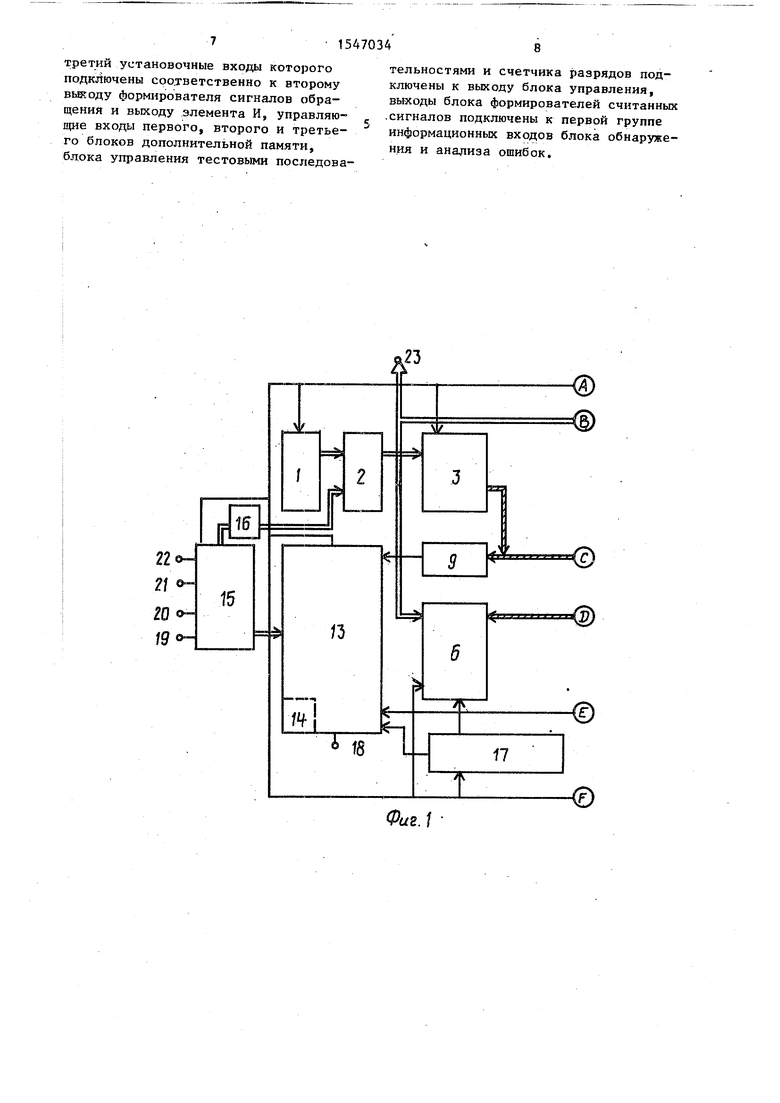

На Фиг.1 и фиг.2 изображена структурная схема предлагаемого устройства} на фиг.З - структурная схема блока управления; на фиг.4 - структурная схема блока управления тестовыми последовательностями.

Устройство содержит счетчик 1 адресов, группу элементов И 2, блок 3 эталонной памяти, первый 4 и второй

5дополнительные блоки эталонной памяти.

Устройство подключают к контролируемому перепрограммируемому блоку

6постоянной памяти.

сл

Јь

О 00 Јъ

Устройство также содержит блок 7 формирователей считанных сигналов, блок 8 обнаружения и анализа ошибок, элемент И 9, третий дополнительный блок 10 эталонной памяти, счетчик 11 разрядов, блок 12 индикации, блок 13 управления с входящим в него ге- нераторо 14 импульсов, блок 15 vn- равления тестовыми последовательноетями, дешифратор 16, формирователь 17 сигналов обращения.

Блок 13 имеет вход 18 пуска.

На фиг.1 также обозначены вход Количество записей 19, вход Количество разрядных комбинаций 20, вход Количество адресных комбинаций 21, вход Количество адресных сигналов 22, адресные выходы 23 и индикаторные выходы 24 и 25 устройства.

Блок 13 управления содержит шифратор 26, регистр 27, блок 28 элемен- гов И, регистр 29. дешифратор 30 две

омбинационные схемы 31 и 32, элемен-j5 щий адресный вход блока 3 и повторя20

ты НЕ 33 и 34, элементы И 35 и 36, (элемент НЕ 37, элемент ИЛИ 38, триггер 39, генератор 40 импульсов, триггер 41 и элементы НЕ 42 и 43.

Блок 15 управления тестовыми последовательностями содержит пульт 44 управления, регистры 45,-454, счетчики 46,-464, триггеры 47,-47+, счетчик 48 и дешифраторы 49 и 50.

Устройство работает следующим об- 25 разом.

По сигналу Пуск блок 13 запускает счетчик 1, при этом элементы И 2 разрешают все адресные комбинации в

ет контрольное считывание. Перебор адресных комбинаций происходит до числа, установленного в блоке 15, соответствующего количеству адресных входов блока 3. Если число этих комбинаций исчерпано, то блок 13 запускает счетчик 11 и блок 10. Разрядные комбинации записаны в блоке 10 в приоритетном порядке в количестве, определяемом числом сочетаний минимально допустимого количества годных, разрядов из общего количества. Порядок контрольного считывания не отличается от вышеописанного и переход к следующему эталону происходит по первому положительному результату. Если все разрядные комбинации дали отрицательный результат, то блок 6 забраковывается.

количестве, установленном блоком 15 ,в точном соответствии с количеством {адресных входов блока 6. Блок 3 разрешен для считывания, а блоки 4,5 и 10 не выбраны. На нулевой адресной комбинации элемент И 9 проверяет наличие нулей на любом из восьми выходов блока 3 и, если нуль есть, то через блок 13 и блок 17 формирует сигнал записи на блок 6. Через блок 7 происходит запись выходной информации из блока 3 в блок 6 по нулевому адресу. Если нуля нет, то через блок 13 выдается команда на перевод счетчика 1 в следующее состояние. Таким образом, диагональная комбинация пе- реписывается из блока 3 в блок 6. После этого блок 6 командой от блока 13 переводится в режим считывания. Счетчик 1 переводится в нулевое состояние, запускается и в режиме считывания выходная информация из блоков .3 и 6 сравнивается в блоке 8 до первого несовпадения. В этом случае блок 8 дает команду в блок 13 на повторный цикл записи. Чередование циклов записи и считывания происходит либо до положительного результата совпадения выходной информации блоков 3 и 6, либо до установленно

го в блоке 15 предельного количества записей. В перрон случае блок 13 дает команду на переход к другому блоку 4, во втором случае блок 13 через блок 15 и элементы И 2 запрещает один из адресных входов блока 3 и повторяет цикл контрольного считв)- вания, при котором сравниваются только половины запоминающих матриц блоков 3 и 6.

При положительном результате блок 13 осуществляет переход к блоку 4, при отрицательном - запрещает следующий адресный вход блока 3 и повторя0

5

0

0

0

5

ет контрольное считывание. Перебор адресных комбинаций происходит до числа, установленного в блоке 15, соответствующего количеству адресных входов блока 3. Если число этих комбинаций исчерпано, то блок 13 запускает счетчик 11 и блок 10. Разрядные комбинации записаны в блоке 10 в приоритетном порядке в количестве, определяемом числом сочетаний минимально допустимого количества годных, разрядов из общего количества. Порядок контрольного считывания не отличается от вышеописанного и переход к следующему эталону происходит по первому положительному результату. Если все разрядные комбинации дали отрицательный результат, то блок 6 забраковывается.

Запись информации с эталона шахматного кода блока 4 в блок 6 и контрольное считывание происходит в порядке, описанном выше с тем отличием, что если на диагональной комбинации определены либо адресные, либо разрядные комбинации, то при тестировании шахматным кодом они не допускаются, т.е. блок 6 может иметь только не менее 1/2 годной емкости запоминающей матрицы.

При отрицательном результате тестирования шахматным кодом блок 6 забраковывается, при положительном - осуществляется переход к блоку 5.

Тестирование комбинацией поля нулей не отличается от шахматной комбинации.

Результат тестирования индицируется блоком 12 индикации, который также имеет выход 24 для возможной машинной обработки, такие же выходы 25 и 23 предусмотрены для номера разрядной и адресной комбинаций соответственно

Выявление неисправностей дешифраторов адреса и типа взаимосвязанных ячеек при однократной записи достигаются формированием совокупности тестовых последовательностей в виде теста для определения области записи диагональных комбинаций, шахматного кода и обратного шахматного кода.

Задача классификации по емкости запоминающей матрицы реализуется формированием тестовой последовательности, определяющей годную для записи .часть запоминающей матрицы.

Совокупность и последовательность формирования тестов в предлагаемом устройстве следующая: определение области записи - запись диагональных комбинаций - считывание диагональных комбинаций - дозапись шах- матного кода - считывание шахматного кода - дозапись инверсного шахматного кода - считывания поля нулей.

В заключение перечислим режимы предлагаемого устройства:

«) режим записи в блок 6 информации из блоков 3,4 и 5, 5) режим считывания из блока 6 записанной информации и сравнение ее с информацией, считываемой из блоков 3,4и5,в) режим классификации по адресным комбинациям в сочетании с режимом -г , t) режим классификации по разрядным комбинациям с режимом Ј

Формула изобретения

Устройство для контроля перепрограммируемых блоков постоянной памяти, содержащее блок эталонной па- мяти, блок формирователей считанных сигналов, формирователь сигналов обращения, блок обнаружения и анализа ошибок, блок управления, счетчик адресов, причем выход блока управления подключен к управляющим входам счетчика адресов, формирователя сигналов обращения, блока эталонной памяти и является выходом устройства для подключения входа разрешения записи-счи- тывания контролируемого блока, первый выход формирователя сигналов обращения является выходом устройства для подключения входа выборки контролируемого блока, выхода блока форми- рователей считанных сигналов являются выходами устройства для подключения информационных входов контролируемого блока памяти, информационные входы

ю

5 20

5

о

5

о 0 ,

первой группы блока обнаружения и анализа ошибок являются входами устройства для подключения информационных выходов контролируемого блока памяти, вход пуска блока управления является одноименным входом устройства, отличающееся тем, что, с целью повышения быстродействия и расширения области применения устройства за счет выявления блоков памяти с ограниченной годностью, дефектов адресных дешифраторов, взаимного влияния элементов памяти, в него введены счетчик разрядов, дополнительные блоки эталонной памяти, группа элементов И, элемент И, дешифратор и блок управления тестовыми последовательностями первая и вторая группы выходов которого соединены соответственно с входами дешифратора и группой установочных входов блока управления,входы Количество записей, Количество разрядных комбинаций, Количество адресных комбинаций, Количество адресных сигналов блока управления тестовыми последовательностями являются одноименными входами устройства, выходы дешифратора подключены к первым входам элементов И группы, вторые входы которых соединены с выходами разрядов счетчика адресов, адресные входы блока эталонной памяти, первого и второго дополнительных блоков эталонной памяти объединены поразрядно, подключены к соответствующим выходам элементов И. группы и являются выходами устройства для подключения адресных входов контролируемого блока памяти, выходы блока эталонной памяти, первого и второго дополнитель- гых блоков эталонной памяти объединены поразрядно и подключены к соответствующим информационным входам блока формирователей считанных сигналов, второй группе информационных входов блока обнаружения и анализа ошибок и входам элемента И, выходы счетчика разрядов подключены к адресным входам третьего дополнительного блока эталонной памяти и являются индикаторными выходами устройства, выходы третьего дополнительного блока эталонной памяти подключены к третьей группе информационных входов блока обнаружения и анализа ошибок, выход которого соединен с первым установоч-- ным входом блока управления, второй и

третий установочные входы которого подключены соответственно к второму выкоду формирователя сигналов обращения и выходу элемента И, управляющие входы первого, второго и третьего блоков дополнительной памяти, блока управления тестовыми последовательностями и счетчика разрядов подключены к выходу блока управления, выходы блока формирователей считанных сигналов подключены к первой группе информационных входов блока обнаружения и анализа ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1348912A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля при производстве перепрограммируемых постоянных запоминающих устройств. Цель изобретения - повышение быстродействия устройства и расширение его функциональных возможностей за счет выявления взаимосвязанных элементов памяти и дефектов адресных дешифраторов, обеспечения возможности классификации по емкости запоминающей матрицы, т.е. выявления блоков памяти с ограниченной годностью. Устройство содержит счетчики адресов и разрядов, блоки эталонной памяти, блок формирователей считанных сигналов, блок обнаружения и анализа ошибок, элемент И и группу элементов И, блок индикации, блок управления, генератор импульсов, блок управления тестовыми последовательностями, дешифратор, формирователь сигналов обращения. Устройство подключается к блоку контролируемой памяти. 4 ил.

Фиг.1

r

in

о

г- J1Л

ОтЩ

13 Ч К1Э

Omtt

ФигЧ

| Электронная промышленность, 1977, № 2, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Микросхемы интегральные | |||

| Запоминающие устройства | |||

| Методы измерения электрических параметров | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1990-02-28—Публикация

1988-02-15—Подача