Предлагаемое изобретение относится к системам автоматизированного контроля параметров самолетной аппаратуры истребителя-перехватчика и может быть применено для контроля ее параметров в процессе полета.

В настоящее время существует целый класс легких истребителей-перехватчиков с очень жесткими весовыми и габаритными ограничениями, для которых необходимо обеспечить контроль параметров аппаратуры в полете и индикацию отклонений этих параметров на индикаторе летчика при воздействии различных помех, например при наличии шумов, активных помех. В целом ряде случаев этот контроль должен осуществляться непрерывно, например контроль параметров датчиков информации, связанных с обеспечением безаварийного управления самолетом и решением ряда других задач.

По основному изобретению (авт.св. №1840568 от 6 мая 1983 г.) известно устройство для контроля (прототип), содержащее датчики, выходы которых соединены с входами коммутатора, вход которого соединен с первым выходом блока управления, второй и третий выходы которого соединены с входами индикатора и блока памяти, через который выход блока сравнения соединен с входом индикатора, блок задания уставок, выход которого соединен с входом блока сравнения, генератор частоты, генератор опорных фаз, синусно-косинусный преобразователь, сумматор, узел извлечения корня, триггер, счетчик, вычитатель, элемент И, причем выход коммутатора через соединенные последовательно триггер, элемент И, счетчик, вычитатель, синусно-косинусный преобразователь, сумматор и узел извлечения корня соединен с входом блока сравнения, четвертый выход блока управления соединен с входами триггера и счетчика, пятый выход блока управления соединен с входом сумматора, шестой выход блока управления через генератор опорных фаз соединен с входом вычитателя, выход генератора частоты соединен с входом элемента И, а блок управления содержит генератор, счетчик и два регистра сдвига, причем выход генератора соединен с входом первого регистра сдвига и через второй регистр сдвига с четвертым и шестым выходом блока управления, выходы первого регистра сдвига соединены с вторым, третьим и пятым выходами блока управления и через счетчик с первым выходом блока управления.

Недостатком известного устройства является невысокая пропускная способность при быстро меняющейся информации на входе, обусловленная тем, что для обеспечения суммирования без сбоев в сумматоре известного устройства во время суммирования не должно производиться запоминание информации, а во время запоминания и выдачи суммарного сигнала в узел извлечения корня не должно осуществляться суммирования. Необходимость раздельного во времени суммирования и выдачи суммарного сигнала обусловлено тем, что процесс суммирования обеспечивается следующими последовательными операциями: запоминание предыдущей информации, суммирование поступившего и запомненного сигналов, запоминание суммарного сигнала (для последующего суммирования) и выдачу его в узел извлечения корня.

Таким образом, в такт запоминания и выдачи суммарного сигнала входная информация не суммируется, что и является причиной невысокой пропускной способности и нежелательно при быстроменяющейся входной информации.

Цель изобретения - повышение пропускной способности при быстроменяющейся входной информации.

Поставленная цель достигается тем, что в известное устройство, содержащее датчики, выходы которых соединены с входами коммутатора, управляющий вход которого соединен с первым выходом блока управления, второй и третий выходы которого соединены с входами индикатора и блока памяти, через который выход блока сравнения соединен с входом индикатора, блок задания уставок, выход которого соединен с входом блока сравнения, генератор частоты, генератор опорных фаз, синусно-косинусный преобразователь, сумматор, узел извлечения корня, первый триггер, счетчик, вычитатель, первый элемент И, причем выход коммутатора через соединенные последовательно первый триггер, первый элемент И, счетчик, вычитатель, синусно-косинусный преобразователь, сумматор и узел извлечения корня соединен с входом блока сравнения, четвертый выход блока управления соединен с входами первого триггера и счетчика, пятый выход блока управления соединен с вторым входом сумматора, шестой выход блока управления через генератор опорных фаз соединен с входом вычитателя, выход генератора частоты соединен с вторым входом первого элемента И, а блок управления содержит генератор, счетчик и первый и второй регистры сдвига, причем выход генератора соединен с входом первого регистра сдвига и через второй регистр сдвига с четвертым и шестым выходом блока управления, первый, второй, третий и четвертый выходы первого регистра сдвига соединены с вторым, третьим и пятым выходами блока управления и через счетчик блока управления с первым выходом блока управления, дополнительно введены третий регистр сдвига, двоичный реверсивный счетчик адреса, четыре триггера, пять элементов И и два элемента ИЛИ, причем вход второго триггера соединен с пятым выходом первого регистра сдвига, неинверсный выход второго триггера через второй элемент И соединен с третьим входом сумматора, а инверсный выход через третий элемент И соединен с четвертым входом сумматора, первый вход четвертого элемента И соединен с третьим выходом второго регистра сдвига, а выход через первый элемент ИЛИ соединен с пятым входом сумматора, первый вход пятого элемента И соединен с четвертым выходом второго регистра сдвига, а выход через второй элемент ИЛИ соединен с шестым входом сумматора, второй вход первого элемента ИЛИ через третий триггер соединен с пятым выходом второго регистра сдвига, входом третьего регистра сдвига и первым входом шестого элемента И, второй вход второго элемента ИЛИ через четвертый триггер соединен с шестым выходом второго регистра сдвига и входом двоичного реверсивного счетчика адреса, выход которого соединен с седьмым входом сумматора, второй вход шестого элемента И соединен с выходом третьего регистра сдвига, а выход через пятый триггер соединен с вторыми входами второго, третьего, четвертого и пятого элементов И, а сумматор содержит первое и второе оперативные запоминающие устройства (ОЗУ), регистр, элемент суммирования, инвертор и четыре элемента И, причем первый вход элемента суммирования соединен с первым входом сумматора, второй вход элемента суммирования соединен с выходами сумматора и регистра, выход элемента суммирования через седьмой и восьмой элементы И соединен с входами установки в "Лог.0", соответственно, первого и второго ОЗУ и через инвертор, девятый и десятый элементы И - со входами установки в "Лог.1", соответственно, первого и второго ОЗУ, вторые входы седьмого и девятого элементов И соединены с третьим входом сумматора, вторые входы восьмого и десятого элементов И соединены с четвертым выходом сумматора, входы выборок кристалла, первого 34 и второго 35 ОЗУ соединены, соответственно, с пятым и шестым входами сумматора, адресные входы обоих ОЗУ соединены с седьмым входом сумматора, выходы обоих ОЗУ соединены с информационным входом регистра, управляющий вход которого соединен с вторым входом сумматора.

К техническим решениям, имеющим признаки, сходные с признаками, отличаемыми заявленное решение от прототипа, являются:

Изобретение по а.с. №468253 М. Кл. G06F 15/46, содержащее три элемента И, двоичный счетчик, два триггера, элемент задержки (эквивалент регистра сдвига), которые в совокупности с другими признаками этого решения обеспечивают повышение помехоустойчивости.

Изобретение по а.с. №481039 М. Кл. G06F 15/46, содержащее 2n элементов И, 5n элементов ИЛИ, 2n триггеров, которые в совокупности с другими признаками этого решения обеспечивают повышение надежности работы устройства.

Изобретение по а.с. №546895 М. Кл. G06F 15/46, содержащее регистр, сумматор по модулю (элемент суммирования), которые в совокупности с другими признаками этого решения обеспечивают упрощение устройства.

Изобретение по а.с. №579625 М. Кл. G06F 15/46, содержащее два счетчика, четыре элемента И, триггер, которые в совокупности с другими признаками этого решения обеспечивают расширение функциональных возможностей.

Таким образом, у заявленного технического решения появились свойства, не совпадающие со свойствами указанных известных решений, и оно обладает существенными отличиями относительно известных решений, заключающихся в повышении пропускной способности при быстроменяющейся входной информации. Пропускная способность увеличивается вдвое за счет того, что пока в одном ОЗУ информация считывается, в другое ОЗУ она записывается.

Достижение положительного эффекта обеспечивается введением дополнительных устройств: регистра сдвига, двоичного реверсивного счетчика адреса, четырех триггеров, пяти элементов И и двух элементов ИЛИ, которые легко выполняются на типовых интегральных микросхемах, например, серии 133, выпускаемых МЭП-ом. Остальные элементы заявленного решения, относящиеся к ограничительной части, также легко выполняются на серийной элементной базе, выпускаемой МЭП-ом (серии 133, 134, 185).

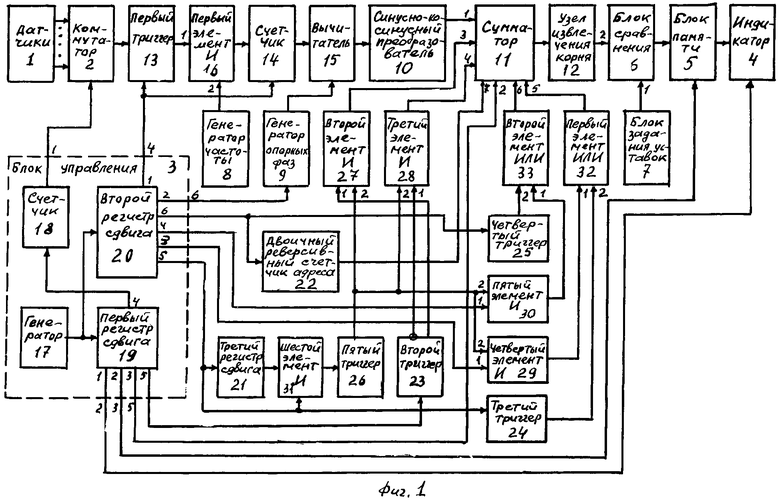

На фиг.1 приведена блок-схема предлагаемого устройства, на фиг.2 - блок-схема сумматора.

Предлагаемое устройство содержит датчики 1, выходы которых соединены с входами коммутатора 2, управляющий вход которого соединен с первым выходом блока управления 3, второй и третий выходы которого соединены с входами индикатора 4, блока памяти 5, через который выход блока сравнения 6 соединен с входом индикатора 4, блок задания уставок 7, выход которого соединен с первым входом блока сравнения 6, генератор частоты 8, генератор опорных фаз 9, синусно-косинусный преобразователь 10, сумматор 11, узел извлечения корня 12, первый триггер 13, счетчик 14, вычитатель 15, первый элемент И 16, причем выход коммутатора 2 через соединенные последовательно первый триггер 13, первый элемент И 16, счетчик 14, вычитатель 15, синусно-косинусный преобразователь 10, сумматор 11 и узел извлечения корня 12 соединен с вторым входом блока сравнения 6, четвертый выход блока управления 3 соединен с входами первого триггера 13 и счетчика 14, пятый выход блока управления 3 соединен с вторым входом сумматора 11, шестой выход блока управления 3 через генератор опорных фаз 9 соединен с входом вычитателя 15, выход генератора частоты 8 соединен с вторым входом первого элемента И 16, а блок управления 3 содержит генератор 17, счетчик 18 и первый и второй регистры сдвига 19, 20, причем выход генератора 17 соединен с входом первого регистра сдвига 19 и через второй регистр сдвига 20 с четвертым и шестым выходом блока управления 3, первый, второй, третий и четвертый выходы первого регистра сдвига 19 соединены с вторым, третьим и пятым выходами блока управления 3 и через счетчик 18 с первым выходом блока управления 3, третий регистр сдвига 21, двоичный реверсивный счетчик адреса 22, четыре триггера 23, 24, 25, 26, пять элементов И 27, 28, 29, 30, 31 и два элемента ИЛИ 32, первого 33, причем вход второго триггера 23 соединен с пятым выходом первого регистра сдвига 19, неинверсный выход второго триггера 23 через второй элемент И 27 соединен с третьим входом сумматора 11, а инверсный выход через третий элемент И 28 соединен с четвертым входом сумматора 11, первый вход четвертого элемента И 29 соединен с третьим выходом второго регистра сдвига 20, а выход через первый элемент ИЛИ 32 соединен с пятым входом сумматора 11, первый вход пятого элемента И 30 соединен с четвертым выходов второго регистра сдвига 20, а выход через второй элемент ИЛИ 33 соединен с шестым входом сумматора 11, второй вход первого элемента ИЛИ 32 через третий триггер 24 соединен с пятым выходом второго регистра сдвига 20, входом третьего регистра сдвига 21 и первым входом шестого элемента И 31, второй вход второго элемента ИЛИ 33 через четвертый триггер 25 соединен с шестым выходом второго регистра сдвига 20 и входом двоичного реверсивного счетчика адреса 22, выход которого соединен с седьмым входом сумматора 11, второй вход шестого элемента И 31 соединен с выходом третьего регистра сдвига 21, а выход через пятый триггер 26 соединен с вторыми входами второго 27, третьего 28, четвертого 29 и пятого 30 элементов И, а сумматор 11 содержит первое и второе оперативные запоминающие устройства (ОЗУ) 34, 35, регистр 36, элемент суммирования 37, инвертор 38 и четыре элемента И 39, 40, 41, 42, причем первый вход элемента суммирования 37 соединен с первым входом сумматора 11, второй вход элемента суммирования 37 соединен с выходами сумматора 11 и регистра 36, выход элемента суммирования через седьмой 39 и восьмой 40 элементы И соединены с входами установки в "Лог.0", соответственно, первого 34 и второго 35 ОЗУ и через инвертор 38, девятый 41 и десятый 42 элементы И со входами установки в "Лог.1", соответственно, первого 34 и второго 35 ОЗУ, вторые входы седьмого 39 и девятого 41 элементов И соединены с третьим входом сумматора 11, вторые входы восьмого 40 и десятого 42 элементов И соединены с четвертым входом сумматора 11, входы выборок кристалла первого 34 и второго 35 ОЗУ соединены, соответственно, с пятым и шестым входами сумматора 11, адресные входы обоих ОЗУ 34, 35 соединены с седьмым входом сумматора 11, выходы обоих ОЗУ 34, 35 соединены с информационным входом регистра 36, управляющий вход которого соединен с вторым входом сумматора 11.

Предлагаемое устройство работает следующим образом.

Выходные сигналы датчиков 1, содержащие помимо основного сигнала также и случайную помеху, через управляемый коммутатор 2 поступают на первый вход первого триггера 13. Управление коммутатором 2 для выбора контролируемого датчика (выдача адреса проверяемого датчика) производится от блока управления 3, который обеспечивает управление коммутатором 2 автоматически по заранее заложенной программе. На второй вход первого триггера 13 из блока управления 3 приходят в строгой временной последовательности импульсы коммутации, сбрасывающие первый триггер 13 в исходное положение (например, "Лог.0" на выходе) и подготавливающие его для приема информации. Установление первого триггера 13 в состояние "Лог.1" осуществляется передним фронтом импульса, поступающего через коммутатор 2 от контролируемого датчика 1 первичной информации. Таким образом, на выходе первого триггера 13 будет сигнал, соответствующий по длительности времени, равному от момента прихода переднего фронта исследуемого сигнала до момента прихода переднего фронта импульса коммутации от блока управления 3. Этот промежуток времени соответствует определенной фазе. При наличии случайных помех эта фаза будет все время флюктуировать, причем параметры флюктуации зависят от соотношения сигнала и случайной помехи. Сигнал с выхода первого триггера 13 поступает на первый вход двухвходового первого элемента И 16, на второй вход которого поступают высокочастотные импульсы от генератора частоты 8. Для обеспечения высокой стабильности генератор частоты 8 выполняется кварцевым. Частота генератора частоты 8 на порядок выше частоты сигналов с исследуемых датчиков 1. Счетчик 14 считает импульсы, поступающие на его вход с выхода первого элемента И 16. Количество импульсов соответствует фазе исследуемого сигнала в данный момент. Разрешение на начало счета счетчику 14 дается одновременно с подачей коммутирующего импульса на первый триггер 13, обеспечивая их синхронную работу. При подаче от первого выхода блока управления 3 адреса на коммутатор 2 подается также сигнал управления от шестого выхода блока управления 3 на вход генератора опорных фаз 9, который выдает, соответственно исследуемому датчику, эталонные фазы θi на второй вход вычитателя 15, который обеспечивает вычитание измеряемой фазы ϕi из эталонной фазы θi. Эта разность фаз θi-ϕi преобразуется синусно-косинусным преобразователем 10 в синусную и косинусную составляющие, т.е. происходит разложение фазы θi-ϕi по осям прямоугольной системы координат.

Сигналы sin(θi-ϕi) или cos(θi-ϕi) поступают на первый вход сумматора 11 и далее на сигнальный вход элемента суммирования 37, где суммируется с выходным сигналом сумматора 11, т.е. с выходным сигналом регистра 36. В процессе суммирования регистр 36 работает в режиме выдачи информации (этому режиму соответствует отсутствие сигнала на втором входе сумматора 11), что обеспечивает суммирование в установившемся режиме.

Первое ОЗУ 34 и второе ОЗУ 35 сумматора 11 работают одновременно и поочередно в режимах записи или чтения. При этом, когда с выхода второго элемента И 27 через третий вход сумматора 11 на вторые входы седьмого 39 и девятого 41 элементов И поступает импульс записи, то первое ОЗУ 34 находится в режиме записи. Одновременно на выходе третьего элемента И 28 и на четвертом входе сумматора 11 импульс записи отсутствует (что соответствует режиму чтения второго ОЗУ 35), восьмой 40 и десятый 42 элементы И закрыты и второе ОЗУ 35 находится в режиме чтения.

Когда с выхода третьего элемента И 28 через четвертый вход сумматора 11 на вторые входы восьмого 40 и десятого 42 элементов И поступает импульс записи, то второе ОЗУ 35 находится в режиме записи. Одновременно на выходе второго элемента И 27 и на третьем входе сумматора 11 импульс записи отсутствует (что соответствует режиму чтения первого ОЗУ 34), седьмой 39 и девятый 41 элементы И закрыты и первое ОЗУ 34 находится в режиме чтения.

Адреса ячеек первого 34 и второго 35 ОЗУ задаются одновременно на адресные входы обоих ОЗУ от двоичного реверсивного счетчика адреса 22 через седьмой вход сумматора 11. Ячейки ОЗУ 34, 35 приводятся в активное состояние сигналом выборки кристалла (ВК). На первое ОЗУ 34 сигнал ВК 1 поступает через пятый вход сумматора 11 с выхода первого элемента ИЛИ 32. На второе ОЗУ 35 сигнал ВК 2 поступает через шестой вход сумматора 11 с выхода второго элемента ИЛИ 33. Считывание информации с выхода первого 34 или второго 35 ОЗУ происходит в режиме чтения (отсутствие сигнала записи) соответствующего ОЗУ, при наличии сигнала ВК 1 или ВК 2 на его входе, а запись в регистр 36 при подаче на управляющий вход регистра 36 сигнала разрешения записи в регистр через второй вход сумматора 11 от третьего выхода первого регистра сдвига 19 (пятый выход блока управления 3). Во время подачи управляющего сигнала на регистр 36 осуществляется запись в его ячейки информации с выхода соответствующего ОЗУ 34 или 35 в зависимости от того, на какое ОЗУ подается сигнал выборки кристалла и соответствующий сигнал чтения.

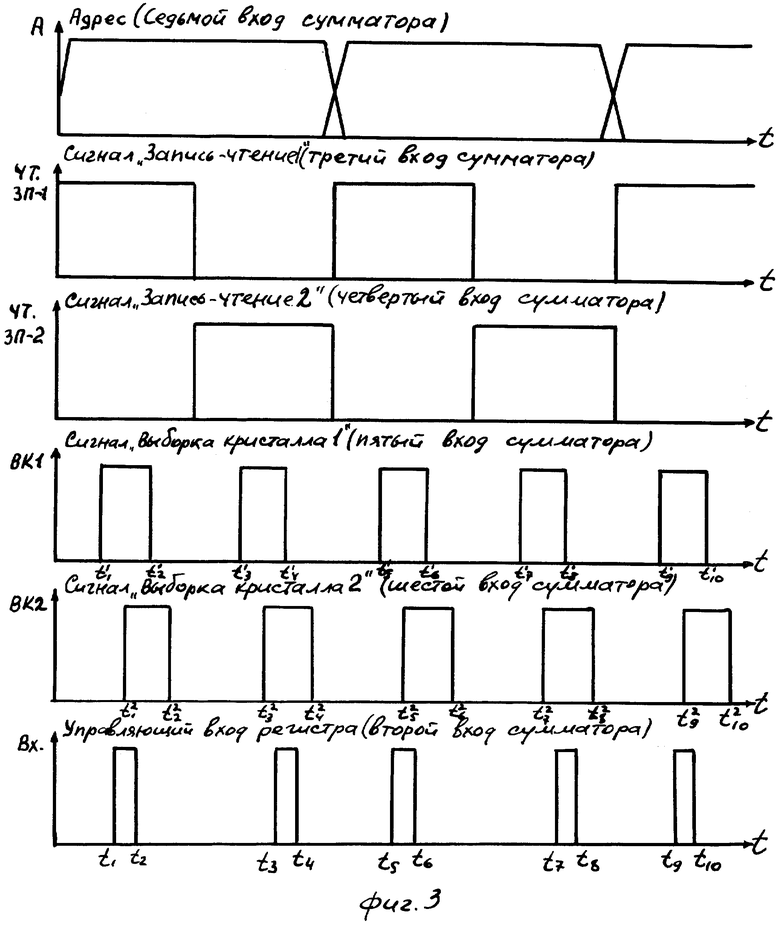

Временные характеристики сигналов, поясняющие работу сумматора 11, и сигналы, приходящие на входы ОЗУ 34, 35, показаны на фиг.3. Считывание информации с первого ОЗУ 34 и запись в регистр 36 происходит в промежутки времени t3-t4, t7-t8 и т.д. Считывание информации со второго ОЗУ 35 происходит в промежутки времени t1-t2, t5-t6 и т.д. Запись информации в первый ОЗУ 34 происходит в моменты времени t1'-t2', t5'-t6' и т.д. (второй ОЗУ 35 находится в режиме чтения). Запись информации во второе ОЗУ 35 производится в моменты t3 2-t4 2, t7 2-t8 2 и т.д. (первое ОЗУ находится в режиме записи). При записи информации на соответствующие ОЗУ 34 или 35 подается сигнал ВК со входов 5 или 6 сумматора 11 и сигнал записи со входов 3 или 4 сумматора 11. В это время на вторые входы седьмого 39 и девятого 41 элементов И или восьмого 40 и десятого 42 элементов И подается сигнал "Лог.1", позволяющий пропустить входной сигнал на входы установки ОЗУ в "Лог.0" или "Лог.1".

Третий регистр сдвига 21, четвертый 29, пятый 30, шестой 31 элементы И, второй 23, третий 24, четвертый 25, пятый 26 триггеры вместе с первым регистром 19 (пятый выход) и вторым регистром сдвига 20 (третий, четвертый, пятый и шестой выходы) обеспечивают временную расстановку импульсов, управляющих работой сумматора 11 в соответствии с временной диаграммой на фиг.3.

В процессе суммирования на выходе сумматора 11 накапливается сумма

и

и

Величина количества выборок m определяется соотношением сигнала и шума, и чем меньше это соотношение и чем выше требуемая точность измерения, тем больше выбирается m. Узел извлечения корня 12 обеспечивает возведение в квадрат сумм  и

и  , их сложение и извлечение квадратного корня. Выходной сигнал узла извлечения корня 12 сравнивается блоком сравнения 6 с уровнем сигнала, задаваемым блоком задания уставок 7 и при превышении этого сигнала запоминается блоком памяти 5 и выдает соответствующий сигнал "Отклонение" летчику на индикатор 4. Управление индикатором 4 осуществляется от первого регистра сдвига 19 блока управления 3 (второй выход).

, их сложение и извлечение квадратного корня. Выходной сигнал узла извлечения корня 12 сравнивается блоком сравнения 6 с уровнем сигнала, задаваемым блоком задания уставок 7 и при превышении этого сигнала запоминается блоком памяти 5 и выдает соответствующий сигнал "Отклонение" летчику на индикатор 4. Управление индикатором 4 осуществляется от первого регистра сдвига 19 блока управления 3 (второй выход).

Если при сравнении какого-либо параметра с уставкой блок сравнения 6 выдает сигнал "Отклонение", то он поступает на блок памяти 5 и запоминается в нем, при этом запрещается подключение следующего датчика до принятия летчиком решения, исключающего это отклонение. Переход на контроль следующего параметра может происходить по команде с блока управления 3, если отклонение параметров не влечет аварийной ситуации, в соответствии с программой, заложенной в блоке управления 3 (эти цепи в блоке сравнения не указаны).

Отсутствие сигнала "Отклонение" на выходе блока сравнения 6 соответствует сигналу "Норма".

При контроле каждого следующего датчика соответствующие элементы устройства (первый триггер 13, счетчик 14, блок задания уставок 7 и блок индикации 4) по сигналам с блока управления 3 устанавливаются в исходное состояние и подготавливаются к приему новой информации.

Описание работы блока управления 3: генератор 17 является генератором тактовых импульсов и обеспечивает синхронизацию работы элементов блока управления 3, а следовательно, и синхронизацию работы всего устройства.

Первый регистр сдвига 19 имеет 5 выходов. Четвертый выход обеспечивает выдачу n-ого импульса на счетчик 18 для изменения адреса на его выходе, третий выход выдает n импульсов (каждому импульсу соответствует своя выборка) на пятый выход блока управления 3 для обеспечения суммирования сумматором 11 информации предыдущей и измеряемой выборок. Число n соответствует числу выборок. После суммирования информации от n выборок и вычисления квадратного корня производится сравнение полученной суммы в блоке сравнения 6 с эталонным кодом, который задается блоком задания уставок 7. По сигналу с второго выхода первого регистра сдвига 19 (третий выход блока управления 3) сигнал превышения суммарной информации над порогом записывается в блок памяти 5 и затем по сигналу с первого выхода первого регистра сдвига 19 (второй выход блока управления 3) производится индикация полученной информации на индикаторе 4. Сигнал с пятого выхода первого регистра сдвига 19 обеспечивает синхронизацию (через второй триггер 23 и второй 27 и третий 28 элементы И) работы сумматора 11 по входам записи-чтения (третий и четвертый входы сумматора 11) в соответствии с временной диаграммой фиг.3.

В течение одной выборки второй регистр сдвига 20 последовательно сдвигает импульсы генератора 17 и последовательно выдает их на 1-6 свои выходы. Различные выходы первого 19 и второго 20 регистров сдвига используются для получения разнесенного во времени процесса обработки сигнала. Причем последовательность обработки информации в каждой выборке следующая:

1. Триггер 13 и счетчик 14.

2. Генератор опорных фаз 9 и вычитатель 15.

3. Установка адреса ячейки ОЗУ 34, 35 двоичным реверсивным счетчиком 22.

4. Установка режима записи первого ОЗУ 34 (или второго ОЗУ 35) и режима чтения второго ОЗУ 35 (или первого ОЗУ 34).

5. Возбуждение кристалла ОЗУ 34 (35) сигналом ВК.

6. запись промежуточного и конечного результатов суммирования в выходном регистре 36 сумматора 11 и выдача его на вход узла извлечения корня 12.

7. Запись сигнала превышения в блок памяти 5.

8. Выдача сигнала с блока памяти 5 на индикатор 4.

При этом третий регистр 21, управляемый сигналом с пятого выхода второго регистра сдвига 20, шестой элемент И 31, пятый триггер 26, второй триггер 23 совместно с вторым 27 и третьим 28 элементами И обеспечивают поочередную работу первого ОЗУ 34 и второго ОЗУ 35 в режимах запись или чтение. Третий 24, четвертый 25 триггеры, четвертый 29 и пятый 30 элементы И, сигналы на которые подаются, соответственно, с пятого, шестого, третьего и четвертого выходов второго регистра сдвига 20, обеспечивают формирование сигнала выборки кристалла (ВК 1 и ВК 2), подаваемого на 5, 6 входы сумматора 11.

Таким образом, совмещение режима записи одного ОЗУ и режима записи другого ОЗУ, полученные путем применения в сумматоре двух ОЗУ и других элементов устройства (элементы 21-36), позволяет вдвое повысить пропускную способность устройства, чем и обеспечивается положительный эффект - повышение пропускной способности при быстроменяющейся входной информации.

Технико-экономический эффект предлагаемого изобретения в сравнении с прототипом позволяет:

повысить пропускную способность аппаратуры, что особенно важно при быстроменяющейся входной информации;

соответственно вдвое сократить аппаратуру контроля при одном и том же количестве контролируемых сигналов;

использовать для реализации устройства серийно выпускаемые МЭП-ом цифровые интегральные схем;

снизить потребляемую мощность, что особенно важно для самолетной аппаратуры.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1986 |

|

SU1840561A2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для нормализации изображений объектов | 1984 |

|

SU1211771A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

Изобретение относится к системам автоматизированного контроля параметров самолетной аппаратуры истребителя-перехватчика и может быть применено для контроля ее параметров в процессе полета. Устройство содержит регистр сдвига, реверсивный счетчик, четыре триггера, пять элементов И, два элемента ИЛИ, сумматор. Техническим результатом является повышение коэффициента использования оборудования. 3 ил.

Устройство для контроля по авторскому свидетельству №1840568, отличающееся тем, что, с целью повышения коэффициента использования оборудования, в него введены регистр сдвига, реверсивный счетчик, четыре триггера, пять элементов И, два элемента ИЛИ, причем выходы второго регистра сдвига соединены с входами реверсивного счетчика, второго и третьего триггеров, второго, третьего и четвертого элементов И и третьего регистра сдвига, выход которого через соединенные последовательно второй элемент И и четвертый триггер соединен с входами с третьего по шестой элементов И, выход первого регистра сдвига через пятый триггер соединен с входами пятого и шестого элементов И, выходы которых, реверсивного счетчика, первого и второго элементов ИЛИ соединены с входами сумматора, выходы второго триггера и третьего элемента И соединены с входами первого элемента ИЛИ, выходы третьего триггера и четвертого элемента И соединены с входами второго элемента ИЛИ.

| Авт | |||

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1983 |

|

SU1840568A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2007-08-27—Публикация

1984-09-24—Подача