Изобретение относится к радиотехнике и может быть использовано в устройствах цифровой техники, автоматике и устройствах обработки дискретной информации.

Известно устройство дискретной линии задержки, содержащее генератор, блоки управления, счетчики импульсов, запоминающее устройство и датчик кода [1].

Использование в этом устройстве раздельных цепей считывания и записи, запись в ЗУ информации о количестве импульсов генератора, поступивших в промежутке между импульсами входной последовательности, обуславливающем применение многоразрядного ЗУ, а также отсутствие многократного использования для записи уже стандартных ячеек памяти увеличивают аппаратурные затраты, снижают надежность и приводят к линейной зависимости требуемого объема ЗУ от величины задержки.

Наиболее близкой по технической сущности к заявляемому устройству является выбранная в качестве прототипа дискретная линия задержки [2], содержащая входной блок, выход которого подключен к входам данных всех микросхем памяти, входящих в блок памяти, блок выработки тактирующих сигналов, состоящий из генератора тактовых импульсов, фазосдвигающего блока и счетчиков, выходы которых подключены к адресным входам соответствующих микросхем памяти, формирователь сигналов "Запись-считывание", выходы которого подключены к соответствующим входам Зп/Сч микросхем памяти, времязадающий блок, выход которого подключен к установочным входам всех счетчиков, блок памяти, состоящий из микросхем памяти, выходы которых подключены к входам формирователей, причем выходы формирователей подключены к входам элемента ИЛИ, а выход данного элемента является выходом линии задержки.

Данная линия задержки имеет общий счетчик адреса, который используется в режиме записи входной информации в память и в режиме считывания информации, что значительно ограничивает функциональные возможности дискретной линии задержки. К недостаткам последней следует отнести наличие погрешности величины задержки ± ΔТ, зависящей от количества микросхем памяти. Наличие в линии задержки сложного фазовращающего блока и использовании для каждой микросхемы памяти своего счетчика адреса усложняют линию задержки и уменьшают ее надежность.

Целью изобретения является улучшение универсальных свойств устройства дискретной задержки, получение однозначных планируемых величин задержек входной информации, повышение надежности и упрощение схемотехнической реализации.

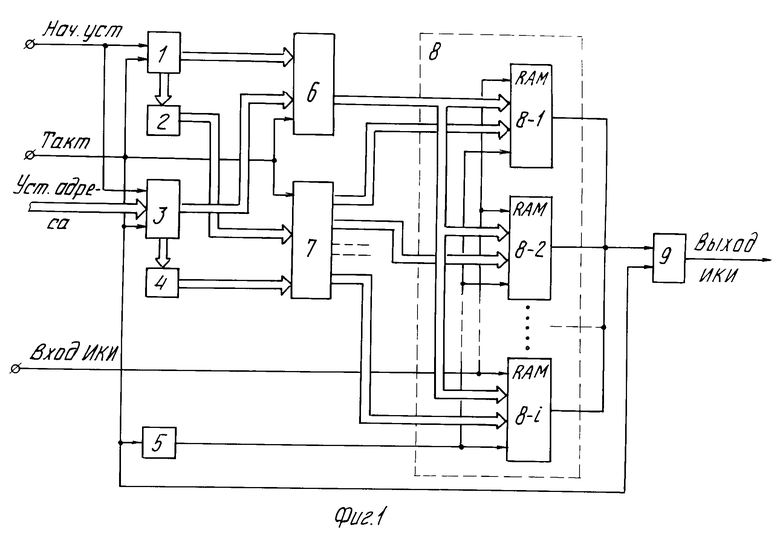

Цель достигается тем, что в устройство управляемой дискретной задержки, содержащее счетчики, формирователи и блок памяти введены управляемый счетчик адреса считывания, схема выбора микросхемы памяти при считывании, схема выбора микросхемы памяти при записи, схема разделения адресов Зп/Сч и схема разделения выбора микросхемы памяти Зп/Сч, причем входная шина "Вход ИКИ" соединена с входами данных всех микросхем памяти, шина тактовой частоты "Такт" одновременно соединена со счетными входами счетчиков адреса записи и считывания, тактовыми входами схем разделения адреса и микросхем памяти при записи и считывании, с входом формирователя сигналов Зп/Сч и с входом синхронизации триггера-формирователя, шина "Нач.уст." подключена к входам сброса счетчика адреса и к установочным входам счетчика адреса считывания, при этом сигналы с входной шины "Уст. адреса" подключены к параллельным входам счетчика адреса считывания, а параллельные выходы счетчика адреса записи и счетчика адреса считывания подключены к соответствующим входам схемы разделения адресов Зп/Сч, параллельные выходы данной схемы соединены с адресными входами каждой микросхемы памяти, параллельные выходы старших разрядов счетчика адреса записи подключены к входам схемы выбора микрсхемы памяти при записи, а параллельные выходы старших разрядов счетчика адреса считывания подключены к входам схемы выбора микросхемы памяти при считывании, выходы схем выбора микросхемы памяти при записи и считывании подключены к входам схемы разделения выбора микросхемы памяти Зп/Сч, а соответствующие выходы данной схемы подключены к входам выборки микросхемы памяти, выход формирователя сигналов Зп/Сч подключен к входам "Запись-считывание" всех микросхем памяти, выходы всех микросхем памяти соединены с входом данных триггера-формирователя, а выход триггера-формирователя подключен к выходной шине "Выход ИКИ" данного устройства.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием новых блоков: счетчика адреса считывания, схемы выбора микросхемы памяти при считывании, схемы выбора микросхемы памяти при записи, схемы разделения адресов Зп/Сч и схемы разделения выбора микросхемы памяти Зп/Сч. Таким образом, заявляемое устройство соответствует критерию изобретения "новизна".

Введение управляемого счетчика адреса считывания, схемы разделения адресов Зп/Сч и схемы разделения выбора микросхемы памяти Зп/Сч приводит к улучшению универсальных свойств устройства, к получению однозначных планируемых величин задержек входной информации, к повышению надежности и к упрощению схемотехнической реализации. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

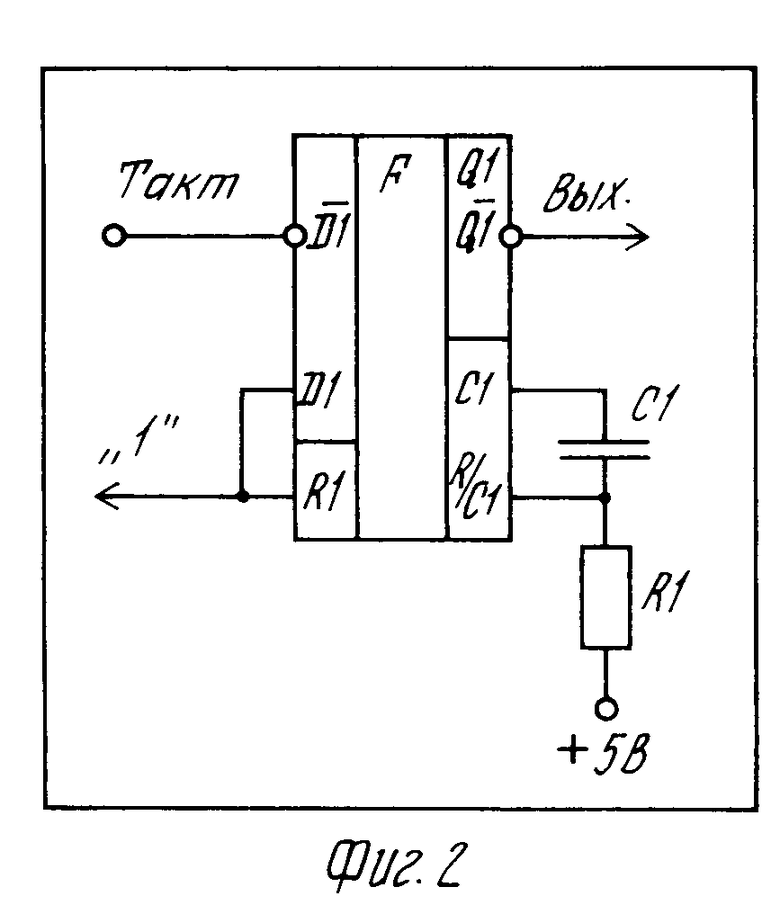

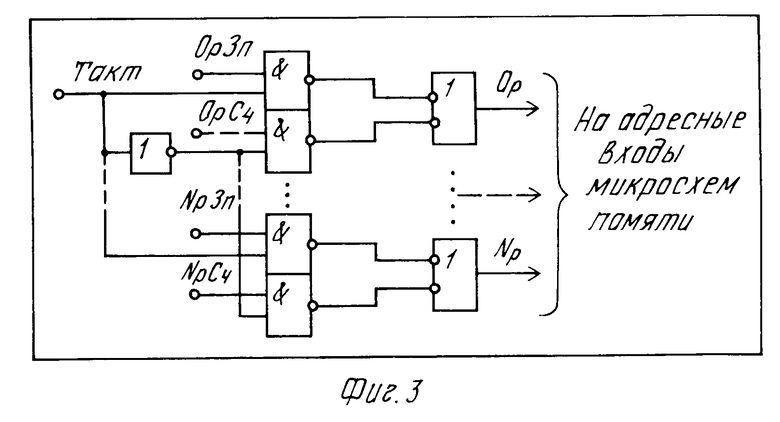

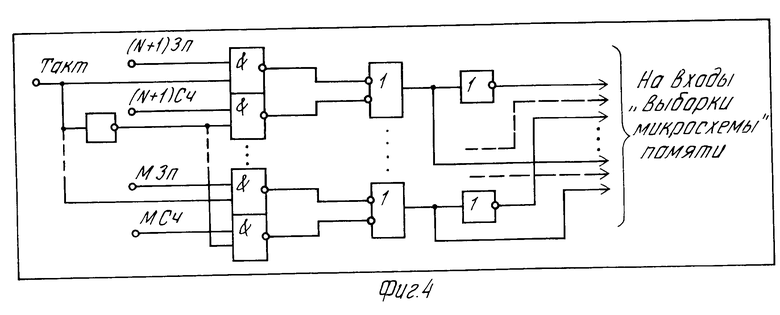

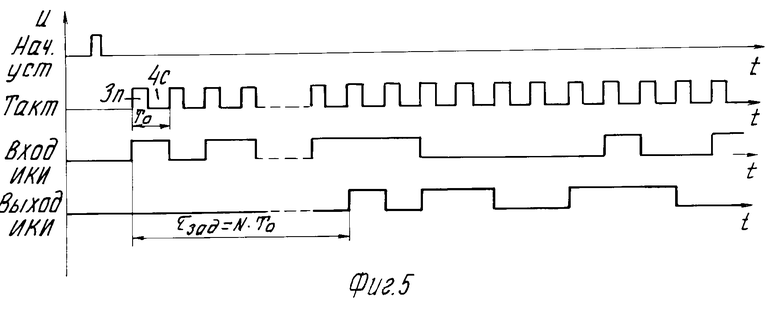

На фиг. 1 представлена блок-схем устройства; на фиг. 2 - электрическая схема формирователя сигналов; на фиг. 3 - схемы разделения адресов Зп/Сч; на фиг. 4 - схемы разделения выбора микросхемы памяти Зп/Сч; на фиг. 5 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит счетчик 1 адреса записи, схему 2 выбора микросхемы памяти при записи, счетчик 3 адреса считывания, схему 4 выбора микросхемы памяти при считывании, формирователь 5 сигналов Зп/Сч, схему 6 разделения адресов Зп/Сч, схему 7 разделения выбора микросхемы памяти Зп/Сч, блок 8 памяти и триггер-формирователь 9.

Устройство работает следующим образом.

Сигнал с входной шины "Нач.уст." поступает на входы сброса счетчика 1 адреса записи, устанавливая его в "нулевое" состояние. Данный сигнал поступает на установочные входы счетчика 3 адреса считывания и устанавливает на его выходе адрес, поступающий с входной шины "Уст.адреса" на его параллельные входы. Предварительная установка адреса счетчика 3 адреса считывания определяет величину задержки, на которую необходимо задержать входную импульсно-кодовую информацию. Меняя только адрес счетчика 3 адреса считывания, можно менять дискретную величину задержки входной информации от одного дискрета - минимальная задержка, до N дискретов - максимальная задержка. Величина дискрета определяется периодом тактовой частоты и равна T0=  , где fо - тактовая частота. Блок памяти в общем случае состоит из нескольких последовательно соединенных для режима записи информации микросхем памяти. Общая емкость памяти выбирается из величины максимальной задержки по следующей формуле:

, где fо - тактовая частота. Блок памяти в общем случае состоит из нескольких последовательно соединенных для режима записи информации микросхем памяти. Общая емкость памяти выбирается из величины максимальной задержки по следующей формуле:

N ≥  + 1 , где N - максимальное число ячеек блока памяти;

+ 1 , где N - максимальное число ячеек блока памяти;

Т - максимальная задержка;

То - период тактовых импульсов.

Работа устройства начинается с поступления на него импульсно-кодовой информации и тактовых импульсов, причем тактовые импульсы должны иметь форму меандра. Для сохранения достоверности выходной задержанной информации предусматривается когерентность входной информации и тактовых импульсов и длительность минимального элемента входной информации должна быть равна или больше, но в целое число раз периоду тактовых импульсов. Импульсно-кодовая информация с входной шины "Вход ИКИ" поступает на входы данных всех микросхем памяти для ее записи. Тактовые импульсы с входной шины "Такт" поступают на счетные входы счетчика 1 адреса записи, на счетные входы счетчика 3 адреса считывания. Оба счетчика работают в режиме сложения, т.е. по каждому периоду тактовых импульсов меняют свой адрес на единицу в сторону увеличения. Принципиальным условием работы данного устройства является то, что на каждом периоде тактовых импульсов происходят запись входной информации (на первом полупериоде) и считывание задержанной входной информации (на втором полупериоде). Причем изменение адреса счетчика 1 адреса записи происходит по концу первого полупериода тактовых импульсов, а счетчика 3 адреса считывания - по концу второго полупериода тактовых импульсов. Тактовые импульсы поступают на схему 6 разделения адресов Зп/Сч, где происходит коммутация на выход данной схемы по первому полупериоду тактового импульса адреса счетчика 1 адреса записи, а по второму полупериоду тактовому импульса адреса счетчика 3 адреса считывания, аналогичное коммутирование происходит и в схеме 7 разделения выбора микросхемы памяти Зп/Сч. Следовательно, по первому полупериоду тактового импульса с помощью схем 6 и 7 происходит выбор ячейки памяти, куда должен записаться минимальный элемент входной информации, соответствующий по времени данному тактовому импульсу, а по второму полупериоду тактового импульса - выбор ячейки памяти, из которой должен считаться задержанный минимальный элемент входной информации. Запись и считывание информации происходят по сигналам, поступающим с выхода формирователя 5 сигналов Зч/Сч на вход "Запись-считывание" выбранных микросхем памяти. Формирование данных сигналов происходит из тактовых импульсов. Сигналы, поступающие с выхода данного формирователя, имеют защитные интервалы, которые позволяют производить запись и считывание информации в устойчивых временных интервалах. Из выше сказанного следует, что после начальной установки по первому тактовому импульсу входная информация записывается в нулевую ячейку блока 8 памяти (нулевая ячейка первой микросхемы памяти), а считывание информации происходит из ячейки памяти с адресом, записанным с входной шины "Уст.адреса". По второму тактовому импульсу происходит запись следующего минимального элемента входной информации в первую ячейку памяти, а считывание информации происходит из ячейки памяти с адресом, записанным с выходной шины "Уст. адреса" плюс одна ячейка и т.д. Отсюда задержанная выходная информация появляется на выходе блока памяти, когда адрес счетчика 3 адреса считывания равен нулю "нулевое" состояние счетчика), т.е. считывание информации происходит из нулевой ячейки блока 8 памяти, с которой начиналась запись входной информации в блок 8 памяти.

Задержанная входная информация с выхода блока 8 памяти поступает на вход данных триггера-формирователя 9. Параллельное подключение выходов всех микросхем памяти справедливо только для случая, когда в блоке 8 памяти применяются микросхемы памяти с тремя состояниями выхода. Если это условие не выполняется, то необходимо для каждой микросхемы памяти использовать свой триггер-формирователь с последующим суммированием всех выходов данных формирователей на элементе ИЛИ. На вход синхронизации триггера-формирователя 9 подаются тактовые импульсы, по передним фронтам которых происходит перезапись входной информации на выход данного формирователя. С выхода триггера-формирователя 9 задержанная импульсно-кодовая информация поступает на выходную шину "Выход ИКИ". Данный выход является выходом данного устройства.

Для более точной подстройки задержки выходной информации на выходе триггера-формирователя 9 можно использовать дискретную линию задержки с фиксированными выводами, например задержку типа МЛЗ. Причем минимальный дискрет данной линии задержки должен быть меньше, чем длительность периода тактовых импульсов.

В качестве элементной базы можно использовать ТТЛ (533, 1533 серии или др.). Блок памяти можно набирать из микросхем серии 132.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Формирователь стробирующего сигнала | 1991 |

|

SU1830194A3 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для сопряжения внешних устройств с общей памятью | 1985 |

|

SU1297069A1 |

Использование: радиотехника, устройства цифровой техники, автоматики, устройства обработки дискретной информации. Устройство осуществляет дискретную задержку входной импульсно-кодовой информации (ИКИ) и состоит из счетчика адреса записи, схемы выбора микросхемы памяти при записи, счетчика адреса считывания, схемы выбора микросхемы памяти при считывании, формирователя сигналов "Запись-считывание" (Зп/Сч), схемы разделения адресов Зп/Сч, схемы разделения выбора микросхемы памяти Зп/Сч, блока памяти и триггера-формирователя. За счет введения в устройство управляемого счетчика адреса считывания, схем выбора микросхем памяти при записи и при считывании, схемы разделения адресов Зп/Сч и схемы разделения выбора микросхемы памяти Зп/Сч стало возможным осуществлять дискретную задержку входной ИКИ с высокой точностью и в большом временном диапазоне с минимальными аппаратурными затратами. Способ задания величины задержки с помощью установки начального адреса в счетчик адреса считывания прост и универсален. Указанное выше существенно расширяет возможности данного устройства и делает его универсальным. 5 ил.

УСТРОЙСТВО УПРАВЛЯЕМОЙ ДИСКРЕТНОЙ ЗАДЕРЖКИ, содержащее счетчик адреса записи, формирователь сигналов "Запись-считывание" и блок памати, отличающееся тем, что, с целью повышения точности задержки входной информации и появления универсальных свойств данного устройства, в него введены управляемый счетчик адреса считывания, схема выбора микросхемы памяти при записи, схема выбора микросхемы памяти при считывании, схема разделения адресов "Запись-считывание", схема разделения выбора микросхемы памяти "Запись-считывание", шина "Начальная установка", шина "Такт" и шина "Установка адреса", причем входная шина "Вход импульсно-кодовой информации" соединена с входами данных всех микросхем памяти, а шина тактовой частоты "Такт" одновременно соединена со счетными входами счетчиков адреса, тактовыми входами схем разделения адреса и микросхем памяти "Запись-считывание", с входом формирователя сигналов "Запись-считывание" и входом синхронизации триггера-формирователя, а шина "Начальная установка" подключена к входу сброса счетчика адреса записи и к установочному входу счетчика адреса считывания, при этом сигналы установки адреса с входной шины "Установка адреса" подключены к параллельным входам счетчика адреса считывания, а параллельные выходы данного счетчика подключены к входам считывания схемы разделения адреса "Запись-считывание", а к входам записи данной схемы подключены параллельные выходы счетчика адреса записи, при этом параллельные выходы схемы разделения адресов, "Запись-считывание" соединены с адресными входами каждой микросхемы памяти, параллельные выходы старших разрядов счетчика адреса записи подключены к входам схемы выбора микросхемы памяти при записи, а параллельные выходы старших разрядов счетчика адреса считывания соединены с входами схемы выбора микросхемы памяти при считывании, при этом выходы схемы выбора микросхем памяти при записи подключены к входам записи схемы разделения выбора микросхемы памяти "Запись-считывание", а входы считывания данной схемы соединены с выходами схемы выбора микросхемы памяти при считывании, выходы схемы разделения выбора микросхемы памяти "Запись-считывание" подключены к входам выборки микросхем памяти, при этом выходы формирователя сигналов "Запись-считывание" подключены к входам "Запись-считывание" всех микросхем памяти, а выходы всех микросхем памяти соединены с входом данных триггера-формирователя, выход которого подключен к выходной шине "Выход импульсно-кодовой информации" данного устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1182647, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-11-30—Публикация

1991-05-05—Подача