Изобретение относится к вычисли- тельной технике и может быть использовано при организации обмена, информацией в режиме прямого доступа к памяти в цифровых вычислительных системах, в частности микропроцессорных .

Целью изобретения является увеличение быстродействия.

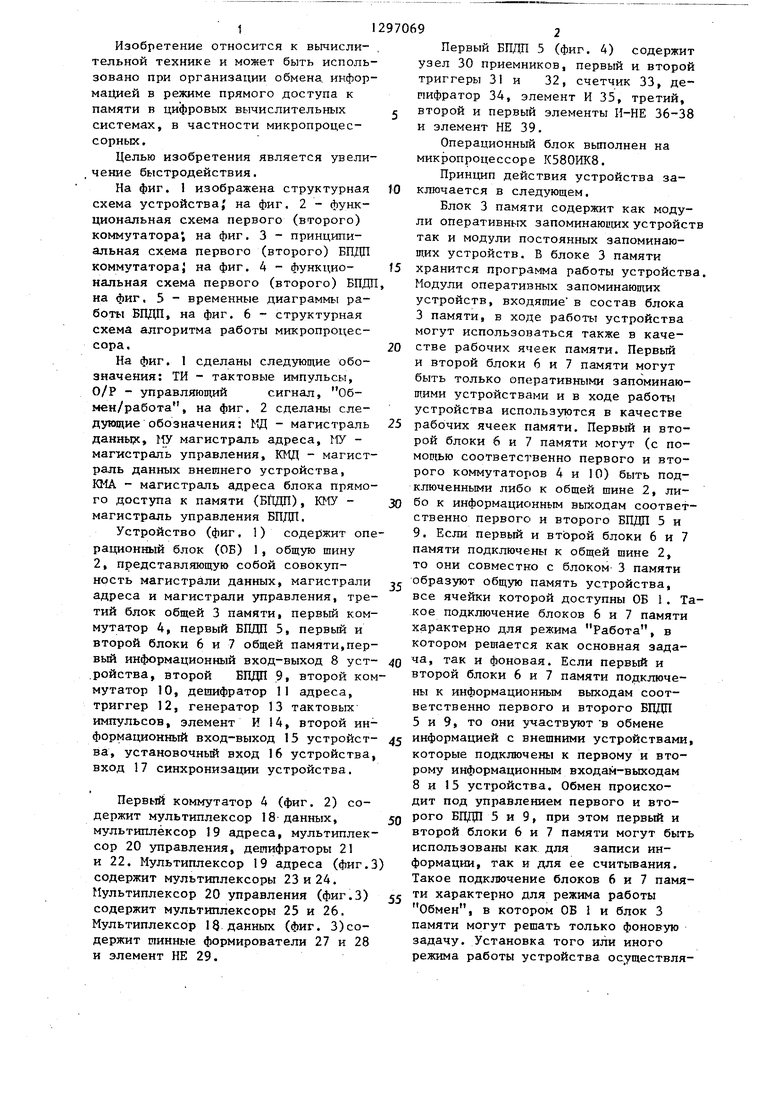

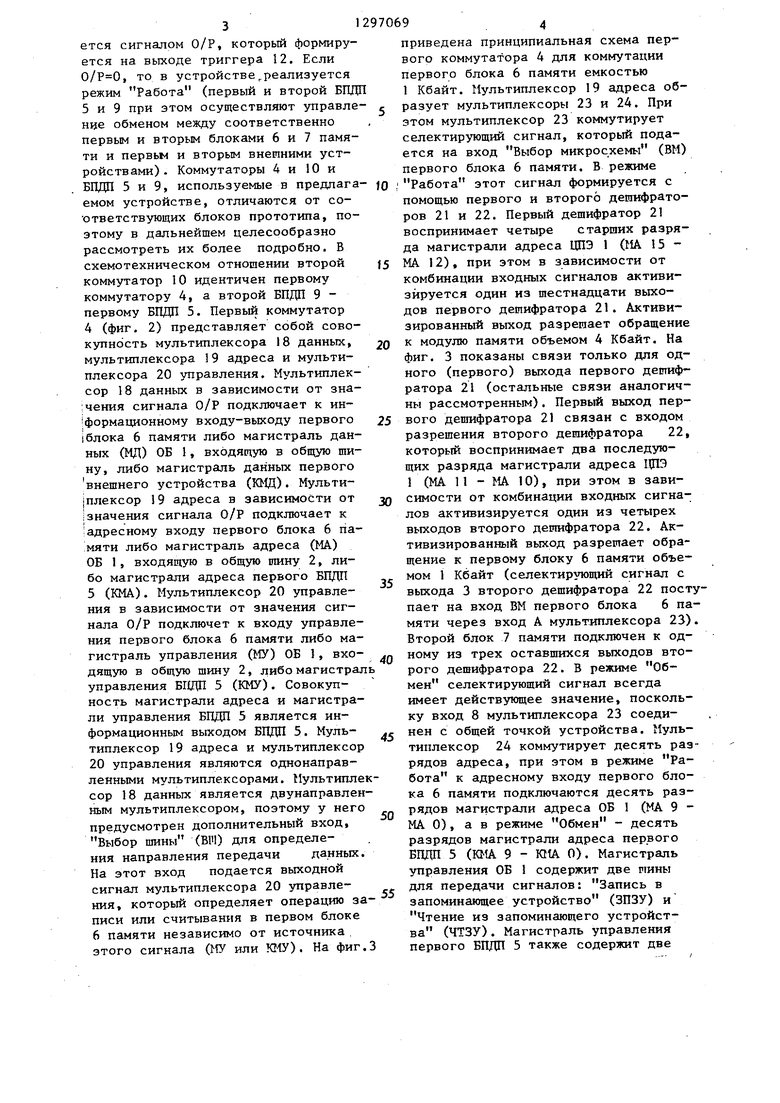

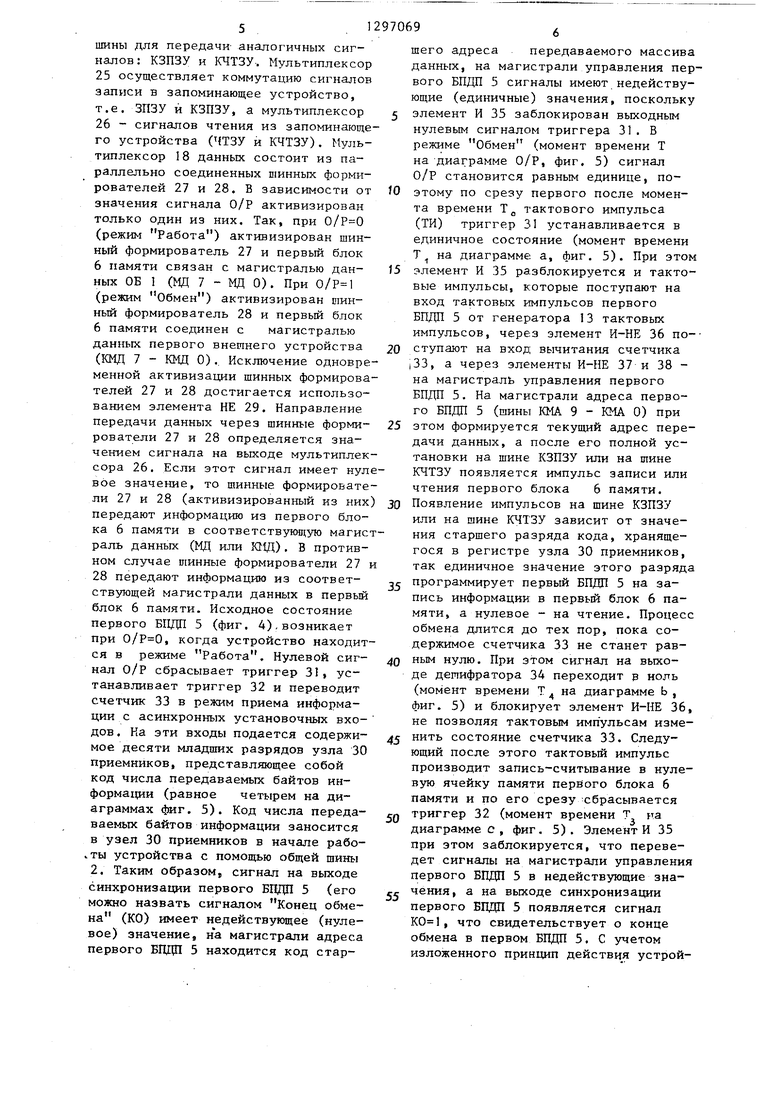

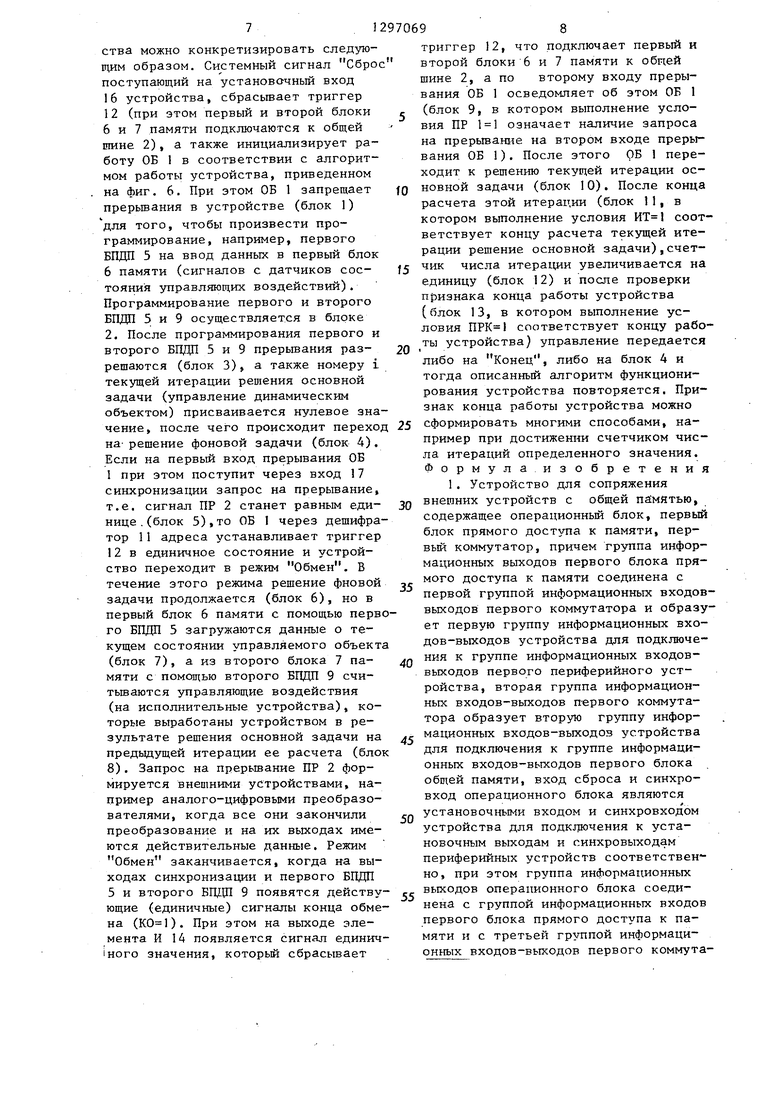

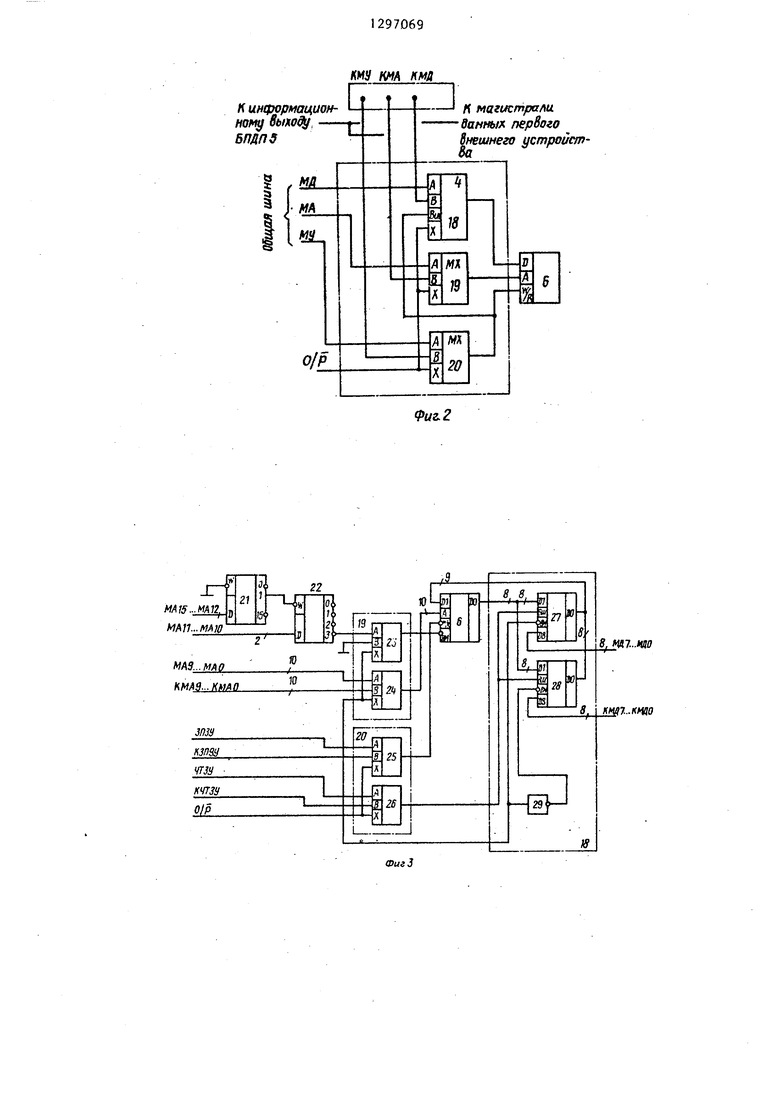

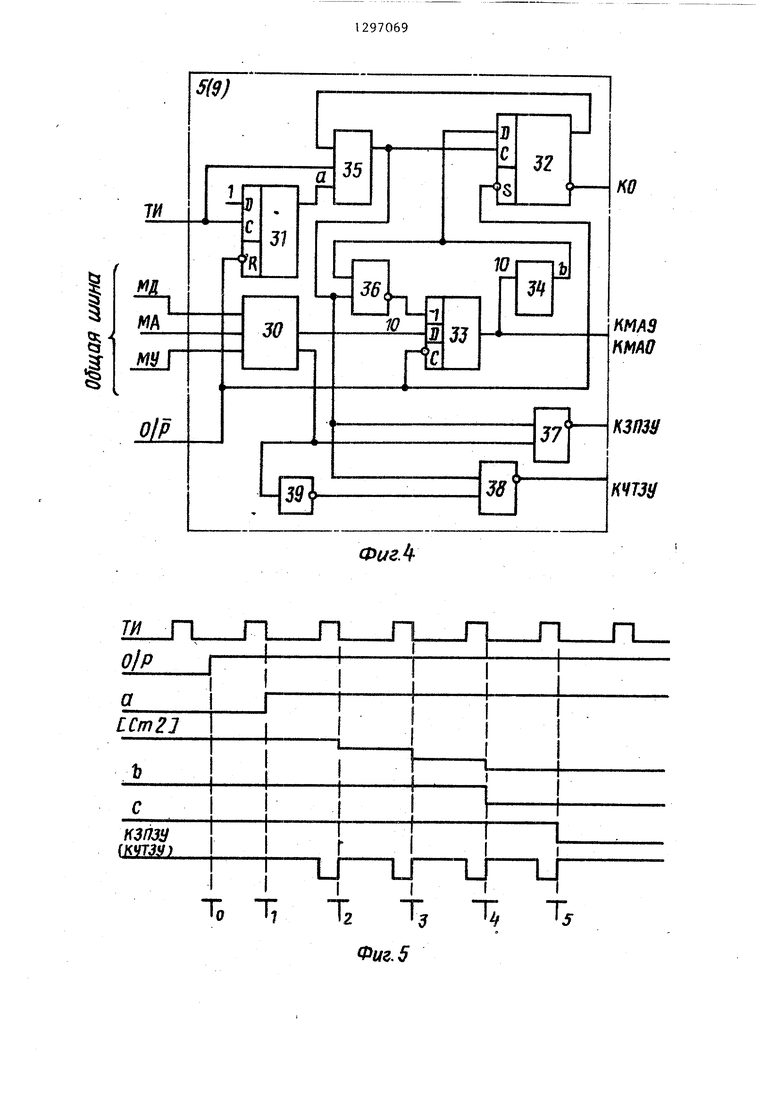

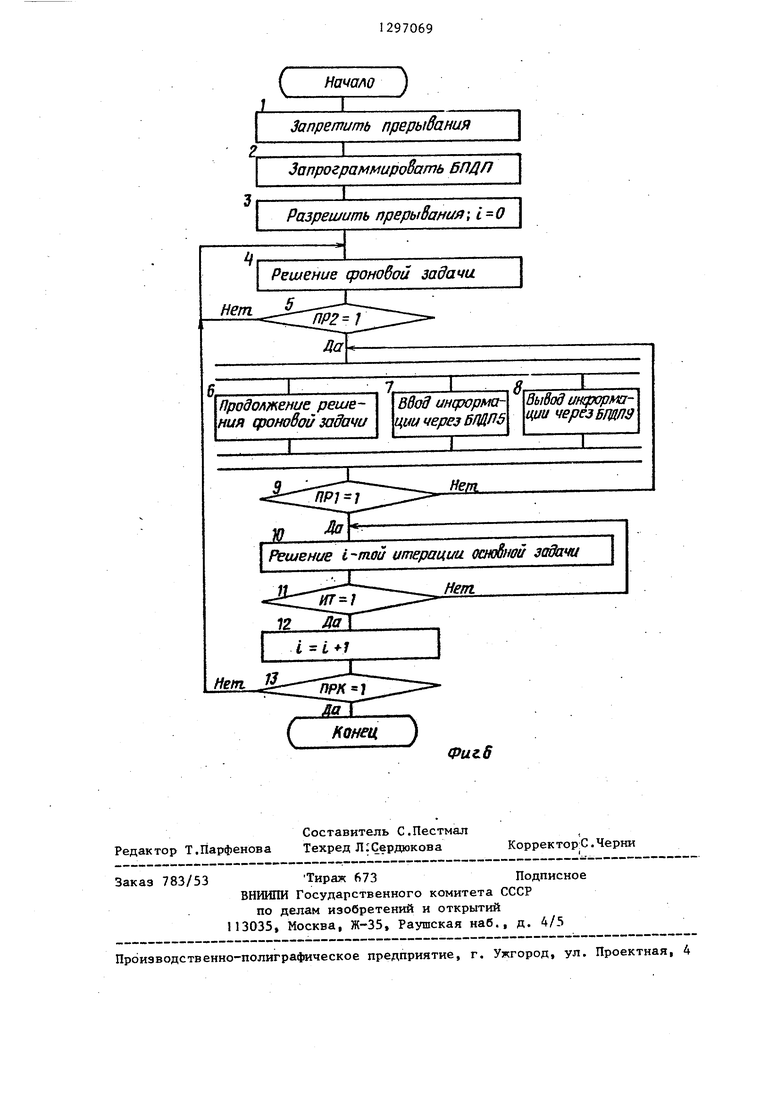

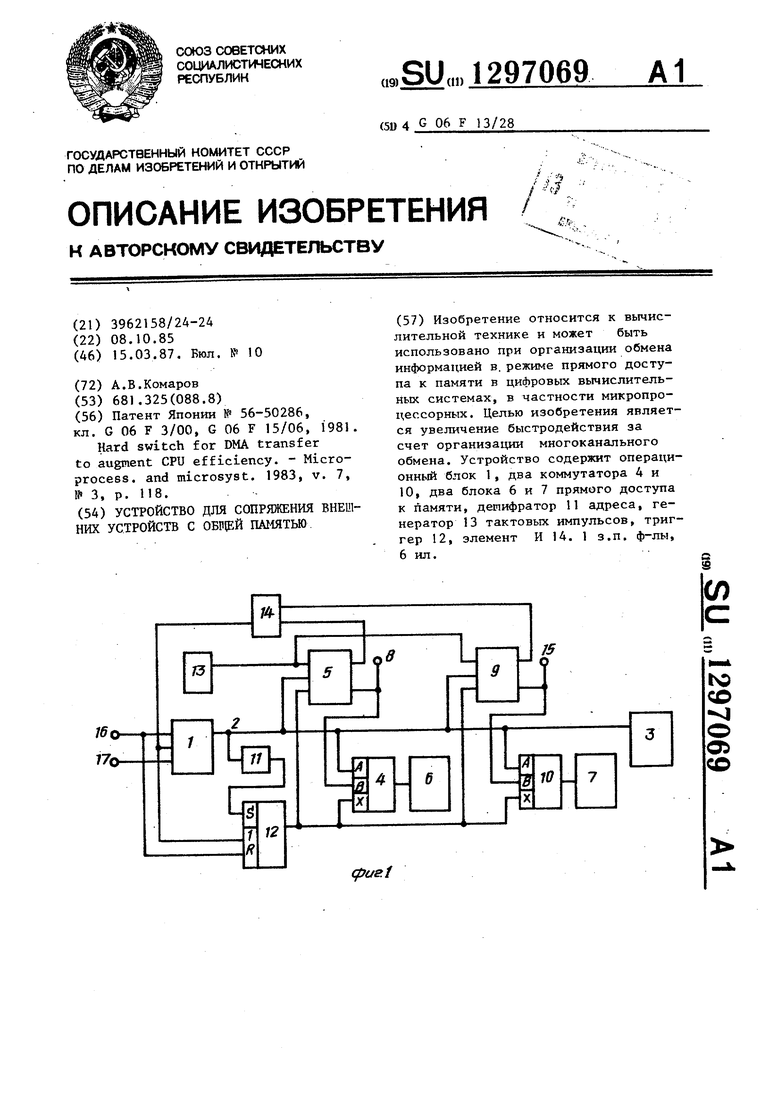

На фиг. 1 изображена структурная схема устройства, на фиг. 2 - функциональная схема первого (второго) коммутатора; на фиг. 3 - принципиальная схема первого (второго) БПДП коммутатораJ на фиг. 4 - функциональная схема первого (второго) БПДП на фиг, 5 - временные диаграммы работы БПДП, на фиг. 6 - структурная схема алгоритма работы микропроцессора.

На фиг. 1 сделаны следующие обозначения: ТИ - тактовые импульсы, О/Р - управляющий сигнал, Обмен/работа, на фиг. 2 сделаны следующие обозначения: ЬЗД - магистраль данньрс, Ш магистраль адреса, flY - магистраль управления, ЮШ - магистраль данных внешнего устройства, КМА - магистраль адреса блока прямого доступа к памяти (БПДП), КМУ - магистраль управления БПДП.

Устройство (фиг, 1) содержит опрационный блок (ОБ) 1, общую шину 2, представляющую собой совокупность магистрали данных, магистрали адреса и магистрали управления, третий блок общей 3 памяти, первый коммутатор 4, первый БЩЩ 5, первый и второй блоки 6 и 7 общей памяти,первый информационный вход-выход 8 уст .ройства, второй БПДП 9, второй комутатор 10, дешифратор 11 адреса, триггер 12, генератор 13 тактовых импульсов, элемент И 14, второй информационный вход-выход 15 устройст на, установочный вход 16 устройства вход 17 синхронизации устройства.

Первьтй коммутатор 4 (фиг. 2) содержит мультиплексор 18-данных, мультиплексор 19 адреса, мультиплексор 20 управления, дешифраторы 21 и 22. Мультиплексор 19 адреса (фиг.З) содержит мультиплексоры 23 и 24. Мультиплексор 20 управления (фиг.З) содержит мультиплексоры 25 и 26. Мультиплексор 18 данных (фиг. 3)содержит шинные формирователи 27 и 28 и элемент НЕ 29.

0

f5

45

0

25

Первый БПДП 5 (фиг. 4) содержит узел 30 приемников, первый и второй триггеры 31 и 32, счетчик 33, дешифратор 34, элемент И 35, третий, второй и первый элементы И-НЕ 36-38 и элемент НЕ 39.

Операционный блок вьтолнен на микропроцессоре К580ИК8.

Принцип действия устройства заключается в следующем.

Блок 3 памяти содержит как модули оперативных запоминающих устройств так и модули постоянных запоминающих устройств. В блоке 3 памяти хранится программа работы устройства. Модули оперативных запоминающих устройств, входящие в состав блока 3 памяти, в ходе работы устройства могут использоваться также в качестве рабочих ячеек памяти. Первый и второй блоки 6 и 7 памяти могут быть только оперативными запоминающими устройствами и в ходе работы устройства используются в качестве рабочих ячеек памяти. Первый и второй блоки 6 и 7 памяти могут (с помощью соответственно первого и второго коммутаторов 4 и 10) быть подключенными либо к общей щине 2, либо к информационным выходам соответственно первого и второго БПДП 5 и 9. Если первый и второй блоки 6 и 7 памяти подключены к общей щине 2, то они совместно с блоком 3 памяти , образуют общую память устройства,

все ячейки которой доступны ОБ 1. Такое подключение блоков 6 и 7 памяти характерно для режима Работа, в котором решается как основная задача, так и фоновая. Если первый и второй блоки 6 и 7 памяти подключены к информационным выходам соответственно первого и второго БЩЩ 5 и 9, то они участвуют в обмене информацией с внешними устройствами, которые подключены к первому и второму информационным входам-выходам 8 и 15 устройства. Обмен происходит под управлением первого и второго БПДП 5 и 9, при этом первый и второй блоки 6 и 7 памяти могут быть использованы как. для записи информации, так и для ее считьгеания. Такое подключение блоков 6 и 7 памяти характерно для режима работы Обмен, в котором ОБ I и блок 3 памяти могут решать только фоновую задачу. Установка того или иного режима работы устройства осуществля30

40

50

55

3

ется сигналом 0/Р, который формируется на выходе триггера 12. Если , то в устройстве реализуется режим Работа (первый и второй БП 5 и 9 при этом осуществляют управлние обменом между соответственно первым и вторым блоками 6 и 7 памяти и первьм и вторым внешними устройствами) . Коммутаторы 4 и 10 и БПДП 5 и 9, используемые в предлагемом устройстве, отличаются от со- ответствующих блоков прототипа, поэтому в дальнейшем целесообразно рассмотреть их более подробно. В схемотехническом отношении второй коммутатор 10 идентичен первому коммутатору 4, а второй БПДП 9 - первому БПДП 5. Первый коммутатор

4(фиг. 2) представляет собой совокупность мультиплексора 18 данных, мультиплексора 19 адреса и мультиплексора 20 управления. Мультиплексор 18 данньк в зависимости от зна;чения сигнала 0/Р подключает к ин- формационному входу-выходу первого iблока 6 памяти либо магистраль данных (МД) ОБ 1, входящую в общую щи ну, либо магистраль данных первого внешнего устройства (КМД). Мульти- |плексор 19 адреса в зависимости от I значения сигнала 0/Р подключает к ; адресному входу первого блока 6 па мяти либо магистраль адреса (МА) ОБ 1, входящую в общую шину 2, либо магистрали адреса первого БПДП

5(КМА). Мультиплексор 20 управления в зависимости от значения сигнала 0/Р подключет к входу управления первого блока 6 памяти либо магистраль управления (МУ) ОБ 1, входящую в общую шину 2, либо магистра управления БГЩП 5 (КМУ). Совокупность магистрали адреса и магистрали управления БПДП 5 является информационным выходом БПДП 5. Мультиплексор 19 адреса и мультиплексо 20 управления являются однонаправленными мультиплексорами. Мультиплсор 18 данных является двунаправленым мультиплексором, поэтому у нег предусмотрен дополнительный вход, Выбор шины (ВШ) для определения направления передачи данных На этот вход подается выходной сигнал мультиплексора 20 управления, который определяет операцию з писи или считывания в первом блоке

6памяти независимо от источника . этого сигнала (МУ или КМУ). На фиг

10

f5

20

25

ьЗ

30

35

40

45

50

55

приведена принципиальная схема первого коммутатора 4 для коммутации первого блока 6 памяти емкостью 1 Кбайт. Мультиплексор 19 адреса образует мультиплексоры 23 и 24. При этом мультиплексор 23 коммутирует селектирующий сигнал, который подается на вход Выбор микросхемы (ВМ) первого блока 6 памяти. В режиме Работа этот сигнал формируется с помощью первого и второго дешифраторов 21 и 22. Первый дешифратор 21 воспринимает четыре старших разряда магистрали адреса ЦПЭ 1 (IIA 15 - МА. 12), при этом в зависимости от комбинации входных сигналов активизируется один из шестнадцати выходов первого дешифратора 21. Активизированный выход разрешает обращение к модулю памяти объемом 4 Кбайт. На фиг. 3 показаны связи только для одного (первого) выхода первого дешифратора 21 (остальные связи аналогичны рассмотренным). Первый выход первого дешифратора 21 связан с входом разрешения второго дешифратора 22, который воспринимает два последующих разряда магистрали адреса ЦПЭ 1 (МА 11 - МА 10), при этом в зависимости от комбинации входных сигналов активизируется один из четырех выходов второго дешифратора 22. Активизированный выход разрешает обращение к первому блоку 6 памяти объемом 1 Кбайт (селектирующий сигнал с выхода 3 второго дешифратора 22 поступает на вход ВМ первого блока 6 памяти через вход А мультиплексора 23). Второй блок 7 памяти подключен к одному из трех оставшихся выходов второго дешифратора 22. В режиме Обмен селектирующий сигнал всегда имеет действующее значение, поскольку вход 8 мультиплексора 23 соединен с общей точкой устройства. Мультиплексор 24 коммутирует десять разрядов адреса, при этом в режиме Работа к адресному входу первого блока 6 памяти подключаются десять разрядов магистрали адреса ОБ 1 (МА 9 - МА 0), а в режиме Обмен - десять разрядов магистрали адреса первого БПДП 5 (КМА 9 - КМА 0). Магистраль управления ОБ 1 содержит две шины для передачи сигналов: Запись в запоминающее устройство (ЗПЗУ) и Чтение из запоминающего устройства (ЧТЗУ). Магистраль управления первого БПДП 5 также содержит две

шины для передачи- аналогичных сигналов: КЗПЗУ и КЧТЗУ.. Мультиплексор

25осуществляет коммутацию сигналов записи в запоминающее устройство, т.е. ЗПЗУ и КЗПЗУ, а мультиплексор

26- сигналов чтения из запоминающего устройства (ЧТЗУ и КЧТЗУ). Мультиплексор 18 данных состоит из параллельно соединенных шинных формирователей 27 и 28. В зависимости от значения сигнала 0/Р активизирован только один из них. Так, при (режим Работа) активизирован шинный формирователь 27 и первый блок

6 памяти связан с магистралью данных ОБ 1 (МД 7 - МД 0). При (режим Обмен) активизирован щин- ный формирователь 28 и первый блок 6 памяти соединен с магистралью данных первого внешнего устройства (КМД 7 - КМД 0).. Исключение одновременной активизации щинных формирователей 27 и 28 достигается использованием элемента НЕ 29. Направление передачи данных через шинные формирователи 27 и 28 определяется значением сигнала на выходе мультиплексора 26. Если этот сигнал имеет нулвое значение, то шинные формирователи 27 и 28 (активизированный из них передают янформацию из первого блока 6 памяти в соответствуюп;ую магисраль данных (МД или ЮЩ). В противном случае вшнные формирователи 27 28 передают информацию из соответствующей магистрали данных в первьй блок 6 памяти. Исходное состояние первого БЩЩ 5 (фиг. 4), возникает при , когда устройство находится в режиме Работа, Нулевой сигнал 0/Р сбрасывает триггер 31, устанавливает триггер 32 и переводит счетчик 33 в режим приема информации с асинхронных установочных вхо- доз. На эти входы подается содержимое десяти младших разрядов узла 30 приемников, представляющее собой код числа передаваемых байтов информации (равное четырем на диаграммах фиг. 5). Код числа передаваемых байтов информации заносится в узел 30 приемников в начале рабо- ты устройства с помощью общей шины 2. Таким образом, сигнал на выходе синхронизации первого БЩЩ 5 (его можно назвать сигналом Конец обмена (КО) имеет недействующее (нулевое) значение, на магистрали адреса первого БПДП 5 находится код стар

5

0

О

шего адреса передаваемого массива данных, на магистрали управления первого БПДП 5 сигналы имеют недействующие (единичные) значения, поскольку элемент И 35 заблокирован выходным нулевым сигналом триггера 31. В режиме Обмен (момент времени Т на диаграмме 0/Р, фиг. 5) сигнал 0/Р становится равным единице, поэтому по срезу первого после момента времени Т, тактового импульса (ТИ) триггер 31 устанавливается в единичное состояние (момент времени Т на диаграмме а, фиг. 5). При этом элемент И 35 разблокируется и тактовые импульсы, которые поступают на вход тактовых импульсов первого БПДП 5 от генератора 13 тактовых импульсов, через элемент И-НЕ 36 по-- ступают на вход вычитания счетчика |33, а через элементы И-НЕ 37 и 38 - на магистраль управления первого БПДП 5. На магистрали адреса первого БПДП 5 (шины КМА 9 - КМА 0) при

5 этом формируется текущий адрес передачи данных, а после его полной установки на щине КЗПЗУ или на щине КЧТЗУ появляется импульс записи или чтения первого блока 6 памяти. Появление импульсов на щине КЗПЗУ или на шине КЧТЗУ зависит от значения старшего разряда кода, хранящегося в регистре узла 30 приемников, так единичное значение этого разряда

программирует первый БПДП 5 на запись информации в первый блок 6 памяти, а нулевое - на чтение. Процесс обмена длится до тех пор, пока содержимое счетчика 33 не станет равным нулю. При этом сигнал на выходе дешифратора 34 переходит в ноль (момент вр€;мени Т на диаграмме Ь , фиг. 5) и блокирует элемент И-НЕ 36, не позволяя тактовым импульсам изме5 нить состояние счетчика 33. Следующий после этого тактовый импульс производит запись-считьгаание в нулевую ячейку памяти первого блока 6 памяти и по его срезу -сбрасывается

Q триггер 32 (момент времени Т на диаграмме с, фиг. 5). Элемент И 35 при этом заблокируется, что переведет сигналы на магистрали управления первого БПДП 5 в недействующие знаг чения, а на выходе синхронизации первого БПДП 5 появляется сигнал , что свидетельствует о конце обмена в первом БЩЩ 5. С учетом изложенного принцип действи я устрой0

ства можно конкретизировать следующим образом. Системный сигнал Сброс поступающий на установочный вход 16 устройства, сбрасывает триггер 12 (при этом первый и второй блоки 6 и 7 памяти подключаются к общей шине 2), а также инициализирует работу ОБ 1 в соответствии с алгоритмом работы устройства, приведенном на фиг. 6. При этом ОБ 1 запрещает прерьшания в устройстве (блок 1) для того, чтобы произвести программирование, например, первого БПДП 5 на ввод данных; в первый блок 6 памяти (сигналов с датчиков сое- тояния управляющих воздействий). Программирование первого и второго БПДП 5 и 9 осуществляется в блоке 2. После программирования первого и второго БПДП 5 и 9 прерьшания раз- решаются (блок 3), а также номеру i текущей итерации решения основной задачи (управление динамическим объектом) присваивается нулевое значение, после чего происходит переход на- решение фоновой задачи (блок 4), Если на первый вход прерывания ОБ 1 при этом поступит через вход 17 синхронизации запрос на прерывание, т.е. сигнал ПР 2 станет равным еди- нице . (блок 5),то ОБ I через дешифратор 11 адреса устанавливает триггер 12 в единичное состояние и устройство переходит в режим Обмен, В течение этого режима решение фновой задачи продолжается (блок 6), но в первый блок 6 памяти с помощью первого БПДП 5 загружаются данные о текущем состоянии управляемого объекта (блок 7), а из второго блока 7 па- мяти с помощью второго БПДП 9 счи- тьтаются управляющие воздействия (на исполнительные устройства), которые выработаны устройством в результате решения основной задачи на предьщущей итерации ее расчета (блок 8). Запрос на прерьгоание ПР 2 формируется внешними устройствами, например аналого-цифровыми преобразователями, когда все они закончили преобразование и на их выходах имеются действительные данные. Режим Обмен заканчивается, когда на выходах синхронизации и первого БЩЩ 5 и второго БЩЩ 9 появятся действу- ющие (единичные) сигналы конца обмена (). При этом на выходе элемента И 14 появляется сигнал единич- iHoro значения, которьй сбрасывает

триггер 12, что подключает первый и второй блоки 6 и 7 памяти к общей шине 2, а по второму входу прерывания ОБ 1 осведомляет об этом ОБ 1 (блок 9, в котором выполнение условия ПР означает наличие запроса на прерывание на втором входе прерывания ОБ 1). После этого ОБ 1 переходит к решению текущей итерации основной задачи (блок 10). После конца расчета этой итерации (блок 11, в котором выполнение условия соответствует концу расчета текущей итерации решение основной задачи),счетчик числа итерации увеличивается на единицу (блок 12) и после проверки признака конца работы устройства (блок 13, в котором выполнение условия соответствует концу работы устройства) управление передается

либо на Конец, либо на блок 4 и тогда описанный алгоритм функционирования устройства повторяется, При знак конца работы устройства можно сформировать многими способами, например при достижении счетчиком числа итераций определенного значения. Формулаизобретения

1. Устройство для сопряжения внешних устройств с общей памятью, содержащее операционньй блок, первый блок прямого доступа к памяти, первый коммутатор, причем группа информационных выходов первого блока прямого доступа к памяти соединена с первой группой информационных входов выходов первого коммутатора и образует первую группу информационных входов-выходов устройства для подключения к группе информационных входов- выходов первого периферийного устройства, вторая группа информационных входов-выходов первого коммутатора образует вторую группу информационных входов-выходов устройства для подключения к группе информационных входов-выходов первого блока общей памяти, вход сброса и синхро- вход операционного блока являются установочными входом и синхровходом устройства для подключения к установочным выходам и синхровыходам периферийных устройств соответствен - но, при этом группа информационных выходов операционного блока соединена с группой информационных входов первого блока прямого доступа к памяти и с третьей группой информационных входов-выходов первого коммутатора, отличающееся тем, что, с целью увеличения быстродействия, в него введены второй блок прямого доступа к памяти, второй коммутатор, триггер,, дешифратор адреса, генератор тактовых импульсов, элемент И, причем группа информационных выходов второго блока прямого доступа к памяти соединена с первой группой информационных входов-выходов второго коммутатора и образует третью группу информационных входов-выходов устройства для подключения к группе информационных входов-выходов второго периферийного устройства, вторая группа информационных входов-выходов второго коммутатора образует четвертую группу информационных входов-выходов устройства для подключения к грзшпе информационных входов-выходов второго блока обтей памяти, при этом группа информационных выходов операционного блока соединена с группой информационных входов второго блока прямого доступа к памяти, с третьей группой информационных входов-выходов второго коммутатора и с группой информационных входов дешифратора адреса, выход которого, соединен с единичными входом триггера, выход которого соединен с управляющими входами первого и второго- коммутаторов, с входами режима работы первого и второго блоков прямого доступа к памяти, выходы конца обмена которых соединены с первым и вторым входами элемента И соответственно,выход которого соединен с первьм нулевым входом триггера и входами пре- рьшания операционного блока, второй нулевой вход триггера соединен с установочным входом устройства, выход генератора тактовых импульсов соединен с тактовыми входами первого и второго блоков прямого доступа к памяти.

2. Устройство по п. 1, отличающееся тем, что блок прямого доступа к памяти содержит узел приемников, счетчик, два триггера, дешифратор, элемент И, три элемента И-НЕ, элемент НЕ, причем группа информационных входов узла приемников образует группу информационных входов, блока прямого доступа к памяти, синхровход первого триггера соединен с первьм входом элемента И и

является тактовым входом блока прямого доступа к памяти, нулевой вход первого триггера соединен с единичным входом второго триггера, с син- хровходом счетчика и является входом

режима работы блока прямого доступа к памяти, группа выходов счетчика, выходы первого и второго элементов И-НЕ образуют группу информационных выходов блока прямого -доступа к памяти, нулевой выход второго триггера является выходом конца обмена блока прямого доступа к памяти, при этом в блоке прямого доступа к памяти группа информационных выходов

узла приемников соединена с группой информационн1 1х входов счетчика, группа выходов которого соединена с группой входов дешифратора, выход которого сое,динен с первым входом

третьего элемента Й-НЕ и с информационными входом второго триггера, единичный выход которого соединен с вторым входом элемента И, выход которого сое,гшнен с синхровходом второго триггера с вторым входом третьего элемента И-НЕ, с первым входом второго элемента И-НЕ, с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом эле- мента НЕ, вход которого соединен с вторым входом второго элемента И-НЕ и с информационным выходом узла приемников счетный вход счетчика соединен с выходом третьего элемента И-НЕ, третий вход элемента И

соединен с выходом первого триггера, информационный вход которого соединен С шиной единичного потенциала устройства.

МАГ5...МА12.

MftJ1...

МАЗ... MA О

КМА9... КМАО

8, тг.що

...KHSO

Фиг. 5

fНачало j

УI

Запретить прерывания

Запрограммировать бПДП

Разрешить прерываний-,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

Изобретение относится к вычислительной технике и может быть использовано при организации обмена информацией в. режиме прямого доступа к памяти в цифровых вычислительных системах, в частности микропроцессорных. Целью изобретения является увеличение быстродействия за счет организации многоканального обмена. Устройство содержит операционный блок 1, два коммутатора 4 и 10, два блока 6 и 7 прямого доступа к памяти, дешифратор 11 адреса, генератор 13 тактовых импульсов, триггер 12, элемент И 14. 1 з.п. ф-лы, 6 ил. to ;о о о со

Решение сронобой задачи

iT

Продолжение решения сронобой

X

Решение i-fnou итерации з(ча

12

Нет

i t ;

HeiriJl

( /f (7//Д )

Редактор Т.Парфенова

Составитель С.Пестмал Техред ЛI Сердюков а

Заказ 783/53

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(риг 6

Коррек тор С.Черни

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Hard switch for DMA transfer to augment CPU efficiency | |||

| - Micro- process, and microsyst | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-08—Подача