Изобретение относится к вычислительной технике и может быть использовано для передачи бинарной информации с помощью сигналов трех уровней напряжения между ЭВМ и периферийными устройствами, находящимися на больших расстояниях друг от друга

Целью изобретения является повышение достоверности передачи информации в виде сигналов трех уровней напряжения (+U,-U,0) за счет выде- |ления логического значения 1 или из двухполярных импульсов, подсчета числа бит в перобразуемом слове, контроля двоичного кода преобразуемого .слова по четности, временного контроля преобразования,фик- сируннцего его начало и конец.

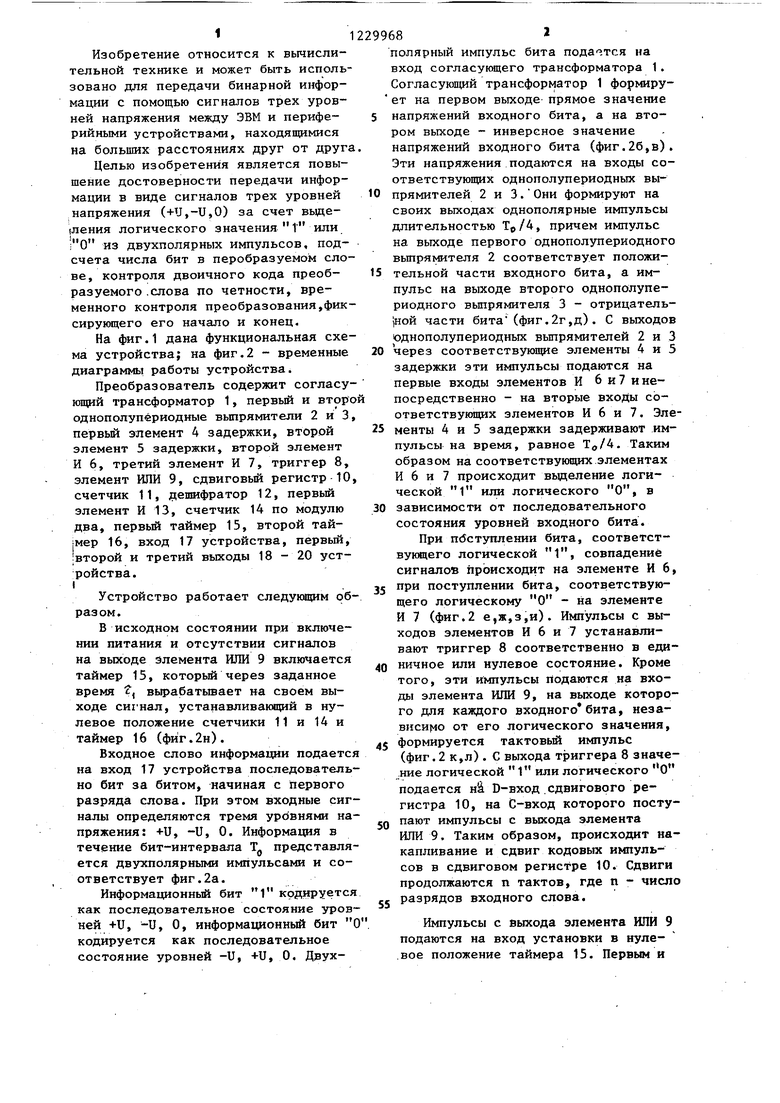

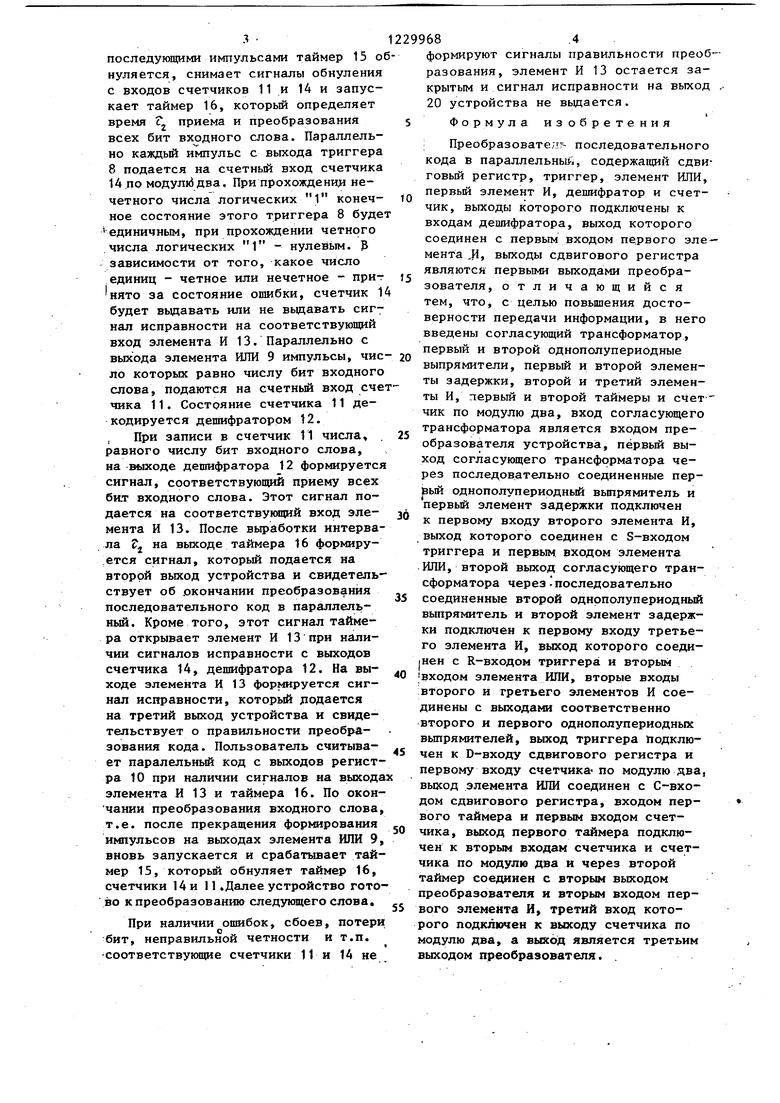

На фиг.1 дана функциональная схема устройства; на фиг.2 - временные диаграммь работы устройства.

Преобразователь содержит согласующий трансформатор 1, первый и второ однополупёриодные вьшрямители 2 и 3, первьй элемент 4 задержки, второй элемент 5 задержки, второй элемент И 6, третий элемент И 7, триггер 8, элемент ИЛИ 9, сдвиговьй регистр 10, счетчик 11, дешифратор 12, первый элемент И 13, счетчик 14 по модулю два, первый таймер 15, второй тай- |Мер 16, вход 17 устройства, первьА, второй и третий выходы 18 - 20 устройства. I

Устройство работает следуницим образом.

В исходном состоянии при включении питания и отсутствии сигналов на выходе элемента ИЛИ 9 включается таймер 15, который через заданное время , вырабатывает на своем выходе сигнал, устанавливающий в нулевое положение счетчики 11 и 14 и таймер 16 {фиг.2н).

Входное слово информации подается на вход 17 устройства последовательно бит за битом, начиная с первого разряда слова. При этом входные сигналы определяются тремя урЬвнями напряжения: +U, -и, 0. Информация в течение бит-интервала Т.. представляется двухполярными импульсами и соответствует фиг.2а.

Информационньй бит 1 кодируется как последовательное состояние уровней +U, -и. О, информационный бит О кодируется как последовательное состояние уровней -U, +U, 0. Двухполярный импульс бита подается на вход согласующего трансформатора 1. Согласуюпи1й трансформатор 1 формиру- ет на первом выходе прямое значение

напряжений входного бита, а на втором выходе - инверсное значение напряжений входного бита (фиг.26,в). Эти напряжения подаются на входы соответствующих однополупериодных выпрямителей 2 и З. Они формируют на своих выходах однополярные импульсы длительностью То/4, причем импульс на выходе первого однополупериодного вьтрямителя 2 соответствует положительной части входного бита, а импульс на выходе второго однополупериодного вьшрямителя 3 - отрицатель- (Ной части бита (фиг.2г,д). С выходов

однополупериодных выпрямителей 2 и 3

через соответствующие элементы 4 и 3 задержки эти импульсы подаются на первые входы элементов И 6 и7 и непосредственно - на вторые вхоДы со- ответствунлцих элементов И 6 и 7. Элементы 4 и 5 задержки задерживают импульсы на время, равное Т,/4. Таким образом на соответствующих .элементах И 6 и 7 происходит вьщеление логической 1 или логического О, в

зависимости от последовательного состояния уровней входного бита.

При поступлении бита, соответствующего логической 1, совпадение сигналов происходит на элементе И 6,

при поступлении бита, соответствующего логическому О - на элементе И 7 (фиг.2 е,ж,з,и). Импульсы с выходов элементов И 6 и 7 устанавливают триггер 8 соответственно в единичное или нулевое состояние. Кроме того, эти импульсы подаются на входы элемента ИЛИ 9, на выходе которого для каждого входного бита, независимо от его логического значения,

формируется тактовый импульс

(фиг.2 к,л) . С выхода триггера 8 значение логической 1 или логического О подается н& D-вход. сдвигового регистра 10, на С-вход которого поступают импульсы с выхода элемента

ИЛИ 9. Таким образом, происходит накапливание и сдвиг кодовых импульсов в сдвиговом регистре 10. Сдвиги продолжаются п тактов, где п - число разрядов входного слова.

Импульсы с выхода элемента ИЛИ 9 подаются на вход установки в нулевое положение таймера 15. Первым и

последующими импульсами таймер 15 онуляется, снимает сигналы обнуления с входов счетчиков 11 и 14 и запускает таймер 16, который определяет время 2 приема и преобразования всех бит входного слова. Параллельно каждьй импульс с выхода триггера 8 подается на счетный вход счетчика 14 по модул1Йдва. При прохождение нечетного числа логических 1 конечное состояние этого триггера 8 буде единичным, при прохождении четного числа логических 1 - нулевьтм. Э зависимости от того, какое число единиц - четное или нечетное - при-г нято за состояние ошибки, счетчик 1 будет выдавать или не вьщавать сигнал исправности на соответствующий вход элемента И 13. Параллельно с выхода элемента ИЛИ 9 импульсы, чис ло которых равно числу бит входного слова, подаются на счетньй вход счечика 11. Состояние счетчика 11 декодируется дешифратором 12.

При записи в счетчик 11 числа . равного числу бит входного слова, на выходе дешифратора 12 формируется сигнал, соответствующий приему всех бкт входного слова. Этот сигнал подается на соответствукяций вход элемента И 13. После выработки интервала j на выходе таймера 16 формируется сигнал, который подается на второй выход устройства и свидетельствует об окончании преобразования последовательного код в параллельный. Кроме того, этот сигнал таймера открывает элемент И 13 при наличии сигналов исправности с выходов счетчика 14, дешифратора 12. На выходе элемента И 13 формируется сигнал исправности, который додается на третий выход устройства и свидетельствует о правильности преобразования кода. Пользователь считывает паралельный код с выходов регистра 10 при наличии сигналов на выхода элемента И 13 и таймера 16. По окон- чании преобразования входного слова, т.е. после прекращения формирования импульсов на выходах элемента ИЛИ 9, вновь запускается и срабатывает таймер 15, которьй обнуляет таймер 16, счетчики 14 и 11 .Далее устройство гото

ВО к преобразованию следующего слова.

При наличии ошибок, сбоев, потери бит, неправильной четности и т.п. -соответствующие счетчики 11 и 14 не

10

t5

25

200

5

0

5

0

5

формируют сигналы правильности преобразования, элемент И 13 остается закрытым и сигнал исправности на выход . 20 устройства не выдается.

Формула изобретения

; Преобразовател последовательного кода в параллельный, содержащий сдвиговый регистр, триггер, элемент ИЛИ, первьй элемент И, дешифратор и счетчик, выходы которого подключены к входам дешифратора, выход которого соединен с первым входом первого элемента .И, выходы сдвигового регистра являются первыми выходами преобразователя, отличающийся тем, что, с целью повьшения достоверности передачи информации, в него введены согласующий трансформатор, первый и второй однополуперибдные выпрямители, первьй и второй элементы задержки, второй и третий элементы И, первый и второй таймеры и счет- чик по модулю два, вход согласующего трансформатора является входом преобразователя устройства, первьй выход согласующего трансформатора через последовательно соединенные пер- вьй однополупериодньй выпрямитель и первьй элемент задержки подключен к первому входу второго элемента И, выход которого соединен с S-входом триггера и первым входом элемента ИЛИ, второй выход согласующего трансформатора через-последовательно соединенные второй однополупериодньй выпрямитель и второй элемент задержки подключен к первому входу третьего элемента И, выход которого соеди- |нен с R-входом триггера и вторым 1ВХОДОМ элемента ИПИ, вторые входы второго и третьего элементов И соединены с выходами соответственно второго и первого однополупериодных выпрямителей, выход триггера Подключен к D-входу сдвигового регистра и первому входу счетчика- по модулю два, выход элемента ИЛИ соединен с С-вхо- дом сдвигового регистра, входом первого таймера и первым входом счетчика, выход первого таймера подключен к вторым входам счетчика и счетчика по модулю два и через второй таймер соеда1нен с вторым выходом преобразователя и вторым входом первого элемента И, третий вход которого подключен к выходу счетчика по модулю два, а выход является третьим выходом преобразователя. .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1992 |

|

RU2025048C1 |

| Устройство для сопряжения абонента с каналом связи | 1984 |

|

SU1211740A1 |

| Устройство для передачи и приема информации | 1983 |

|

SU1156109A1 |

| Резервированное устройство | 1989 |

|

SU1635185A1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1615891A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU822175A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного кода в параллельный | 1980 |

|

SU924696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-10-04—Подача